基于ZYNQ平台的XDMAIP核性能研究

金璐

关键词: Xilinx XDMA 数据通路 性能

PCIe Gen5 信号速率已经达到32 Gb/s[1],在数据采集、雷达通信、遥感探测等领域,数据量的日益增大和数据处理的日益复杂化,使高速数据传输逐渐成为通信系统设计中的关键点[2]。XDMA 是Xilinx 系列FPGA 中官方自带的PCIe“高级”IP[3],所谓的“高级”指的就是XDMA 操作层面比较“高级”,其操作层面主要在应用层,简单来说,在FPGA 例化配置完以后基本上不需要FPGA 在逻辑层面上进行过多的操作[4],FPGA 只需要对Host 主机进行中断触发操作即可,所有的DMA 操作完全由Host 主机通过PCIe 配置XDMA的寄存器来实现。

1 XDMA IP 核概述

Xilinx DMA/Bridge Subsystem for PCI Express?是Xilinx 公司2017 年前后新推出的PCIe FPGA 解决方案[5]。功能上涵盖了PCIe IP 核、SGDMA 功能、多通道分离,同时支持AXI 总线访问等。XDMA 支持Ultra‐Scale+、UltraScale 和Virtex7 XT Gen3,以及7 系列[6]。最高支持4 对Host-to-Card(H2C)和Card-to-Host(C2H)数据通道。

2 XDMA IP 核结构

该IP 核的主要功能就是完成Host 主机和FPGA 之间完成PCIe 接口的数据传输。配置部分主要分为DMA 配置和PCIe Bridge 配置这两个部分具体描述如下(如图1 所示)。

2. 1 DMA 配置

XDMA IP 核可通过AXI Memory Mapped 接口或者通过AXI Streaming 接口来配置,以支持直接连接至RTL 逻辑。在PCIe 地址空间与AXI 地址空间之间可使用所提供的字符驱动程序通过以上任一接口进行高性能块数据移动。除了基本DMA 功能外,DMA 还支持最多4 条上行和下行通道、支持PCIe 流量绕过DMA 引擎(主机DMA 旁路),还支持通过可选描述符旁路来管理来自FPGA 互连结构的描述符,以满足需要最高性能和最低时延的应用的需求。

2. 2 PCIe Bridge

接收到PCIe 数据包将被转换为AXI 流量,接收到的AXI 流量则将被转换为PCIe 流量。桥接功能适合需要快速且轻松地访问PCI Express 子系统的AXI 外设使用。桥接功能可用作为端点(Endpoint)或根端口(Root Port)。

读写部分分为两种:一种是数据的读写,DMA 通过MIG 控制DDR 完成数据读写;另一种是配置数据的读写,通过AXI-lite 总线与BRAM 连接后,XDMA 将PCIe 配置信息存在BRAM。

3 XDMA IP 核配置说明

配置说明主要包括3 个部分来介绍XDMA IP 的使用方式,分别是PL 端的配置说明、PS 端的配置说明及XDMA 驱动相关设计。

3. 1 PL 端配置说明

PL 端搭建最基本的Block Design,如图2 所示,该设计使用的软件版本是Vivado 2020.2。

其中DMA/Bridge Subsystem for PCI Express 核与ZYNQ7 Processing System 的相关配置情况如下。

3.1.1 DMA/Bridge Subsystem for PCI Express 核配置情况

(1)Basic 项。lane width 表示PCIe 通信并行数据宽度,设计中使用的ZYNQ7 最高只支持X4,兼容情况需考虑Host 主机的PCI 卡槽最大支持。

link speed 选择最大的,这里的IP 核都是PCIe 2.0协议的。

AXI clock 是AXI 总线时钟频率,选125 M。

DMA interface 是AXI Memory Mapped 即地址映射,用于访问存储类的设备, 另一个 AXI Stream 表示AXI 数据流,没有地址,数据直接流入或流出。

(2)PCIe ID 项。这里是一些厂商ID、设备ID 等配置,保持默认即可,否则对应驱动需要修改INF 文件。

(3)PCIe:BARs 项。PCIe to AXILite Master Interface:XDMA 作为PCI-AXI 桥接器时,Host 主机可以通过XDMA 访问PL 端的BRAM,值得注意的是PCIe toAXI Translation 需要PC 与PL 端商定,否则访问地址会出现偏差。

PCIe to DMA Interface:默认选项,Host 主机访问DDR 的方式如下 Host->XDMA->PS->DDR。

PCIe to DMA Bypass Interface:不做勾选,如勾选则IP 核仅作为PCIe 使用,如需使用DMA 功能,可另行添加定制DMA 核配合使用。

(4)PCIe:MISC 项。

User Interrupts:这里选择2 个,即PL2PC 的中断一共两个。

Legacy Interrupt Settings:這种使用的INTA,为漏极开路且低电平有效(相应的IRQ 应编程为电平触发方式)。

3.1.2 ZYNQ7 Processing System 核配置情况

(1)PS-PL 配置项。

使能M AXI GP0 interface,用于PS 端访问BRAM使用;使能S AXI HP0 interface,用于PC 端访问DDR使用。

(2)MIO 配置项。

使能Quad SPI Flash,固化程序;使能UART1,用于调试输出。

(3)Interrupt 配置项。

使能IRQ_F2P[15:0]选项,用于PL 端到PS 端的中断触发通路,具体PS 端的中断响应后面会进行描述。

3. 2 PS 端配置说明

下面介绍PS 端搭建设置,Vivado2020.2 与以往的Vivado 版本不同需要手动关联. xsa 文件,具体流程如下。

3.2.1 Export Hardware

生成bit 文件后,File->Export,在这个界面下可以看到Vivado2020.2 这个版本已经没有SDK 的启动选项了,Include bitstream 文件->Next。

3.2.2 生成xsa 文件

文件生成路径选择默认路径,项目根目录下->Next,即可生成文件。

3.2.3 创建Demo 工程

后面根据需要创建工程即可,这里创建了一个Hello World 基础工程。

3.2.4 添加中断触发函数

由于使用到PL 端到PS 端中断触发,所以需要在main.c 中添加PL 中断的触发函数,这里使用到了SDK 提供的中断库文件xscugic.h,以下仅中断函数库提供的函数变量和函数体,具体操作可自行查阅资料,默认即可。在该设计中使用的到函数具体介绍如下。

(1)产生一个中断控制器实例——XScuGic。

(2)中断控制器配置实例——XScuGic_Config。

(3)找到scugic 实体——XScuGic_LookupConfig。

(4)初始化scugic——XScuGic_CfgInitialize。

(5)Xilinx 提供的通用异常处理程序——Xil_ExceptionRegisterHandler。

(6)中断处理函数——XScuGic_InterruptHandler(中断方式为查表方式)。

(7)使能异常处理——Xil_ExceptionEnable。

(8)连接到自己定义的中断处理函数——XScuGic_Connect(对应IRQ_F2P[15:0]配置个数,注册中断回调函数)。

(9)设立的中断实例——XScuGic_Enable。

基本流程为:初始化中断控制器→建立中断→注册特定的中断→写中断处理函数。PL 到PS 的中断就完成了。

3. 3 XDMA 驱动设计说明

下面介绍PL 到PC 的中断控制搭建,需要结合XDMA 驱动说明,该设计中使用的是Xilinx 官方提供的驱动文件,编译环境是VS2017,针对Win10 平台编译,这里仅讲解XDMA 驱动通路设计原理,不进行过多的逻辑编程。pg195-pcie-dma 提到,XDMA 模块中的DMA 操作以描述符形式。

3.3.1 DMA Engine

XDMA 驱动中的DMA Engine Framework 使用的也是描述符操作,基本操作步骤如下。

(1)申请一个DMA Channel。

(2)根据设备(Slave)特性,配置DMA Channel。

(3)要进行DMA 传输的时候,获取一个用于识别该次传输的描述符(descriptor)。

(4)将该次传输提交给dma engine 并启动传输。

(5)等待传输结束。

(6)然后,重复3~5 次即可。

3.3.2 User interrupt

(1)注册中断回调函数XDMA_UserIsrRegister。

(3)注册中断ISR 和DPC 的回调函数。

WDF_INTERRUPT_CONFIG_INIT(&config,EvtInterruptIsr,EvtInterruptDpc)。

(3)中断DPC 处理函数EvtInterruptDpc。

(4)HandleUserEvent 函数。

4 具体测试方案结果及结论

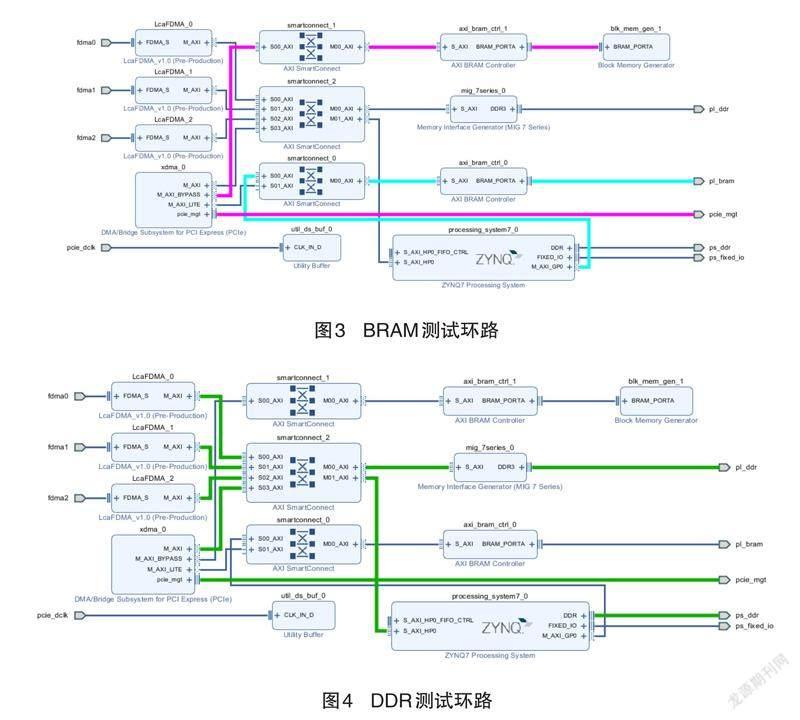

如图3 所示,针对BRAM 测试结果如下。

bypass mode:64 bytes≈0.000058s,lite mode 与bypassmode 测试速率一样。

如图4 所示,针对DDR 测试结果如下。

XDMA X1Gen2 模式(PS DDR)读取速率 400 MB/s左右,写入速率340 MB/s 左右。

XDMA X2Gen2 模式(PS DDR)读取速率 600 MB/s左右,写入速率640 MB/s 左右。

XDMA X2Gen2 PC 全速读取PL DDR 速率(PLDDR),讀取速率670 MB/s 左右。

XDMA X2Gen2 PL 读写PL DDR 时,PC 读取PLDDR 速率(PL DDR),读取速率360 MB/s 左右。

PCIE X1Gen2 模式的理论速率是500 MB/s,X2Gen2 模式的理论速率是1 GB/s,XDMA 实测结果达到PCIe 的理论数值的70% 左右。