射频模块中晶振对电磁兼容影响研究

马世娟,肖永平,倪晓东

(中科芯集成电路有限公司,江苏 无锡 214072)

0 引言

20 世纪70 年代,研究者发现通过在不同介质表面上引入周期性的结构可对电磁波幅度进行控制。该类设计可对不同频率下的电磁波产生滤波器效应。21 世纪,研究者对电磁波的控制拓展到相位层面,利用周期性界面对电磁波的幅度和相位进行控制。电磁场的应用带动科技突飞猛进的发展[1]。但在实际应用中,有用电磁波被利用的同时,无用电磁波给系统或者模块造成干扰,导致系统或者模块不能正常工作。

随着通信技术的不断发展,飞机、船舶、卫星、地面应用等载体的需求量越大、功能越来越复杂,其间的电磁干扰也变得尤为突出[2-4]。根据电磁兼容(EMC)的定义,不难理解,某一设备不会干扰处在同一电磁环境中的其他设备,同时自身也不会受到其他电磁干扰(Electromagnetic Interference,EMI)的影响。现在大多数产品均对EMC 提出了要求。同时,相关领域也制定了详细的标准、规范以及辐射参考标准。

在实际应用中,对电磁兼容的研究应用大多处于问题解决法的阶段[5-9]。文献[10]利用CST 仿真机壳缝隙大小与电缆间耦合大小等参数,实现电磁辐射干扰的有效抑制,但并未对板级电磁兼容进行研究与仿真;文献[11]结合测试事例,讨论按元器件布局与布线原则来达到抗干扰设计的目的,并未对其中间过程进行研究。在产品预言前期,缺乏通过仿真手段对电磁干扰进行仿真、分析的手段,以达到提前识别电磁干扰是否存在干扰风险的目的。结合电磁干扰仿真结果,对产品提供理论优化指导,既能最大化减小电磁干扰对产品的影响,也能缩短产品设计周期以及提高产品调试效率。

本文提出了一种SoC 芯片时钟方案,提供了两种版图设计方案。通过信号间隔离度仿真,提前识别到版图设计方案一中CLK50M 与clk3 差分对间的隔离度低,存在CLK50M 间接干扰SoC 芯片内部模拟信号的风险,进而恶化SoC 芯片输出模拟信号质量。根据信号间隔离度仿真结果指导版图设计,本文给出了版图设计方案二。对比两种版图设计方案的实测结果,方案一的输出模拟信号测试结果中存在干扰,而方案二的输出模拟信号测试结果中无干扰。测试结果验证了仿真结果的准确性。与传统的建模仿真方法相比,本文提出的板级隔离度仿真方法具有高效、准确的优点。同时该方法也具有较强的实用型,可应用于板级任意两信号的隔离度评估,对规避板级EMI 风险以及模块EMC 具有参考意义。

1 硬件方案设计

模块主要实现功能为信号处理,即将数字信号处理成中频模拟信号,中频模拟信号经过滤波等输出到连接器。其中,时钟发生器产生4 对差分时钟提供给SoC 芯片(JS71XX 型高速多通道信号处理电路),晶振输出的50 MHz 时钟信号为时钟发生器提供参考时钟。为了避免晶振信号通过耦合路径将时钟谐波干扰信号带入到芯片内部,本方案要求晶振输出时钟信号与时钟发生器产生4 对差分时钟间的隔离度为60 dB。

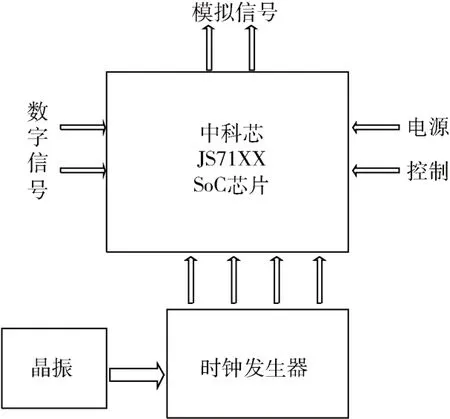

如图1 所示,方案中采用中科芯的JS71XX 型高速多通道信号处理电路,其封装采用SiP 封装,简称SoC 芯片。该SoC 芯片主要功能有完成模拟信号数字化、信号正交变换、通道校准、功率控制、中频模拟信号输出等。

图1 硬件方案

在方案实施版图设计时,重点评估晶振信号及时钟发生器输出信号对模拟信号的干扰影响,评估时钟信号与模拟信号间的隔离度。

2 方案设计与仿真

2.1 方案设计

为了时钟信号与模拟信号间的隔离度,根据设计经验,本方案提供了两种不同版图设计方案SoC 芯片、晶振、时钟发生器三部分的布局、布线,其他部分的布局、布线方案均相同,用于分析对比布局、布线对隔离度的影响。

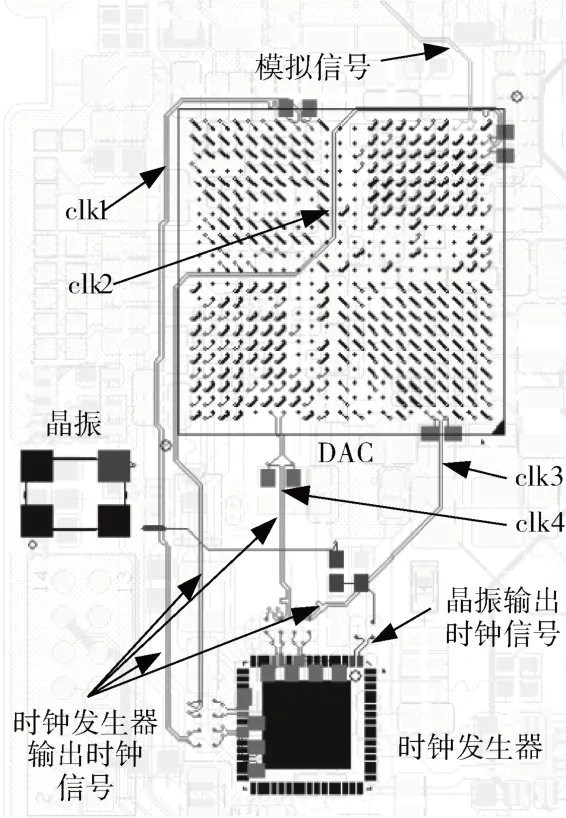

第一种版图设计方案中,晶振位于SoC 芯片左下方,时钟发生器位于晶振的右下方且位于SoC 芯片的下方,其详细布局如图2 所示。印制板层叠为8 层,晶振位于上表层,SoC 芯片、时钟发生器两个器件位于下表层。晶振输出时钟信号命名为CLK50M,其相关器件与走线均位于上表层。时钟发生器输出4 对时钟差分对信号,分别命名为clk1、clk2、clk3、clk4。clk1、clk2 两对时钟差分对走线位于印制板第6 层,clk3、clk4 两对时钟差分对走线位于印制板第3 层。SoC 芯片输出的模拟信号走线位于印制板第3 层。

图2 版图设计方案一

第二种版图设计方案中,晶振位于SoC 芯片斜下方。时钟发生器位置不变,仍位于晶振的右下方且位于SoC 芯片的下方,其详细布局如图3 所示。晶振仍位于上表层,SoC 芯片仍位于下表层。与第一种版图设计方案不同的是,为方便clk1、clk2 两对时钟差分对走线,将时钟发生器放置于上表层,且印制板层叠调整为10 层。晶振输出时钟信号CLK50M 相关器件与走线均位于上表层。为方便走线,将时钟发生器输出4 对时钟差分对进行换pin。本文仍按照到达SoC 芯片pin 脚位置进行命名,分别为clk1、clk2、clk3、clk4。clk1、clk2 两对时钟差分对走线位于印制板第8 层,clk3、clk4 两对时钟差分对走线位于印制板第3 层。Soc 芯片输出的模拟信号走线位于印制板第3 层。

图3 版图设计方案二

2.2 仿真

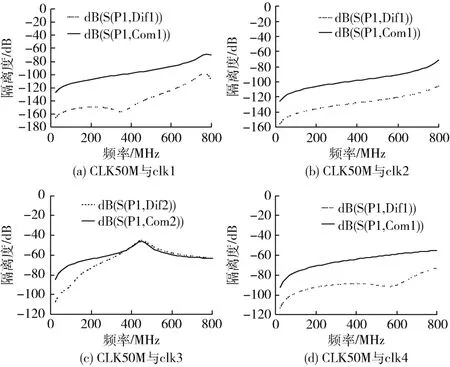

版图设 计方案一中,CLK50M 与clk1、CLK50M 与clk2、CLK50M 与clk3、CLK50M 与clk4 的隔离度分别如图4 (a)、图4 (b)、图4 (c)、图4 (d)所示。SoC 芯片输出模拟信号的频率为347.5 MHz,故文中关注50 MHz 晶振产生的N次谐波是否通过时钟发生器输出的时钟差分对信号带入到SoC 芯片内部,从而影响SoC 芯片模拟信号的信号质量。在频率为600 MHz 处,CLK50M 与clk1差分对间的隔离度为-87 dB,CLK50M 与clk2 差分对间的隔离度为-98 dB,CLK50M 与clk3 差分对间的隔离度为-48 dB,CLK50M 与clk4 差分对间的隔离度为-61 dB。

图4 版图设计方案一仿真结果

由仿真结果可以看出,CLK50M 与clk1、clk2 差分对间的隔离度比CLK50M 与clk3、clk4 差分对间的隔离度大,其原因为CLK50M 走线在上表层,clk1、clk2 走线在第6 层,而clk3、clk4 走线在第3 层,且clk3、clk4 信号器件与CLK50M 信号器件均在上表层且距离较近。

版图设 计方案二中,CLK50M 与clk1、CLK50M 与clk2、CLK50M 与clk3、CLK50M 与clk4 的隔离度分别如图5 (a)、图5 (b)、图5 (c)、图5 (d)所示。在频率为600 MHz处,CLK50M 与clk1 差分对间的隔离度为-60 dB,CLK50M 与clk2 差分对间的隔离度为-65 dB,CLK50M与clk3 差分对 间的隔 离度为-94 dB,CLK50M 与clk4 差分对间的隔离度为-86 dB。由仿真结果可以看出,CLK50M 与clk1、clk2 差分对 间的隔 离度比CLK50M 与clk3、clk4 差分对间的隔离度大。

图5 版图设计方案二仿真结果

对比以上两种版图设计方案的信号隔离度仿真结果可以看出,因版图设计二中将时钟发生器输出clk1、clk2 的pin 脚换到 了版图 设计一 中clk3、clk4 的pin 脚 的位 置,所 以CLK50M 与clk1、CLK50M 与clk2 的隔离 度因表层器件位置拉近,其间的隔离度变小。同样,CLK50M 与clk3、CLK50M 与clk4 的隔离 度因表 层器件位置拉远,其间的隔离度变大。与时钟发生器相同输出pin 脚处对比,版图设计方案一中CLK50M 与clk3 差分对间的隔离度比版图设计方案二中CLK50M 与clk1 差分对间的隔离度小12 dB。版图设计方案一中CLK50M与clk4 差分对间的隔离度比版图设计方案二中CLK50M 与clk2 差分对间的隔离度小4 dB。

3 实测结果

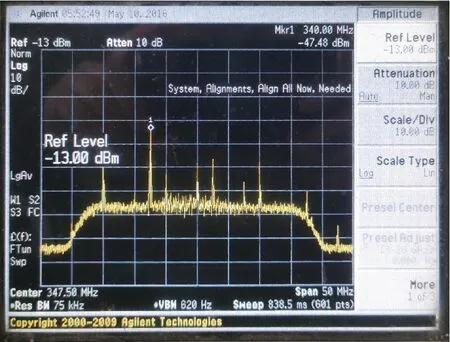

将贴片后的射频模块进行测试。版图设计方案一的测试结果如图6 所示,由测试结果可以看出,在347.5 MHz±25 MHz 范围内存在杂散干扰,导致模拟信号质量变差,射频模块不能正常工作。

图6 版图设计方案一测试结果

版图设计方案二的测试结果如图7 所示。由测试结果可以看出,当模拟信号输出增益为-24.4 dBm 时,在347.5 MHz±25 MHz 范围内无杂散干扰。当模拟信号输出增益为-59.8 dBm 时,在347.5 MHz±25 MHz 范围内无杂散干扰。

图7 版图设计方案二测试结果

结合两种方案的版图设计、隔离度仿真结果以及输出信号测试结果分析,版图设计方案一的输出模拟信号测试结果中存在干扰,其原因为时钟发生器的时钟输入信号与时钟输出信号的布局、走线在空间上存在交叉以及布局不优,导致时钟发生器的时钟输入信号与时钟输出信号间的隔离度较低,时钟输出信号上存在时钟输入信号的谐波,该谐波干扰通过时钟输入信号带入到SoC芯片内部,从而恶化SoC 芯片的输出模拟信号质量。版图设计方案二中CLK50M 与clk1 差分对间的隔离度比版图设计方案一中CLK50M 与clk3 差分对间的隔离度大12 dB,版图设计方案二中作为强干扰源的CLK50M、clk1~clk4 被保护得比版图设计方案一中的信号好,且时钟发生器的时钟输入信号与时钟输出信号在空间上无交叉以及相关布局优,减小了SoC 芯片中模拟信号被干扰的风险,故版图设计方案二的输出信号质量优于版图设计方案一中的输出信号质量,且不存在干扰。

4 结论

本文提出了一种SoC 芯片时钟方案,并设计了两种版图设计方案。针对电磁干扰的原因进行分析,通过判断信号间隔离度仿真结果,可提前识别版图方案中是否存在信号间干扰风险,进而恶化SoC 芯片输出模拟信号质量。文中根据信号间隔离度仿真结果指导版图设计,并给出优化版图方法,即拉远干扰源与受干扰体之间的距离,改善了信号间隔离度性能。测试结果表明,版图设计两种方案的仿真结果与实测结果吻合,验证了仿真结果的准确性、可参考性。本文研究结果对规避板级EMI 风险以及模块EMC 具有参考意义。