芯片样品验证平台自适应和同步测试功能的设计与实现

徐靖林,王 栋,魏 斌,王 赟,窦志军,成 嵩

(北京智芯微电子科技有限公司,北京 100192)

0 引言

随着芯片行业的快速发展,在芯片设计公司,芯片测试贯穿于整个设计生产过程中,测试验证是芯片设计中非常重要的一部分。当芯片量产回来,首要的任务是对芯片所有的功能和性能进行充分的测试验证,只有经过全面验证达到预期的设计指标,才能推进市场。而对于量产级的芯片,验证通常选取一定比例数量来进行抽样测试。

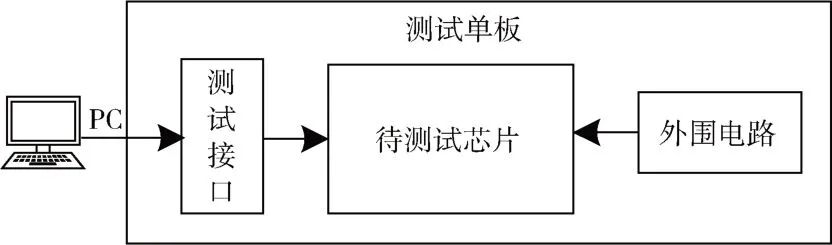

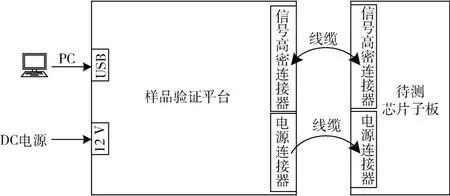

目前,传统的芯片样品验证,在行业内大多是基于自身芯片特征设计相应的测试设备,通过测试夹具来逐一测试,针对不同的芯片需要设计不同的测试设备。图1 为传统的芯片样品验证单板测试电路结构。单板测试对于样品数量要求多、测试时间长的测试项目来说,搭建环境、测试仪器设备的利用率以及时间配置完全不占优势,大大降低了测试效率,导致项目周期延长。

图1 传统样品验证单板测试电路结构

在一些大型的设计公司,也有专门设计的自动化测试平台,采用微控制器 (Microcontroller Unit,MCU)来实现自动化控制,通过对数据处理来实现多芯片的同步测试,这种自动化控制平台,能满足各种测试项目的自动化测试需求,是比较理想的测试方案。但是专业化的自动测试平台需要投入大量的研发成本,通常这些公司会依据自研芯片的特征来开发符合自身标准要求的特定的自动化测试平台。

本方案是针对工业级芯片的测试验证提出的。在芯片样品验证时,某些测试验证项目的规范要求样品数量需达到77 颗1 000 小时的连续性测试实验,其中包括长时间的可靠性环境实验测试[1-2]。如果采用传统的单板测试方案,一颗芯片对应一个测试设备,这将会耗费大量的测试时间,测试效率极低,对测试资源都是一个极大的挑战和浪费;同时无法保证测试环境的一致性,影响测试结果,再加上测试需要迭代,更是很难掌控。

针对这类测试项的问题,前期的测试方案采用了一种多芯片同步自测试的方法,如图2 所示电路结构。从测试成本、资源、周期方面考虑,将多颗芯片放置在同一个测试台上,且每颗芯片提前下载好可以上电自循环的测试程序,测试时将安装好芯片的测试平台放置在对应测试项目的测试仪器设备中,然后通过外供电方式给平台提供电源进行测试。如果中间有测试失败的现象是不清楚的,需要等待一个测试循环周期结束后,连接测试夹具来读取每颗芯片里的数据,通过程序预设的一些特殊标识符号去判断测试结果。这种多芯片测试平台方案虽然提高了测试效率,但是不能实时跟踪测试状态,而且仅支持某一类测试,因此也具有局限性。

图2 前期多芯片样品验证平台的电路结构

本文提出了一种芯片样品验证平台的自适应与同步测试的设计方案,具有多通信接口自适应和多颗芯片同步测试的功能。硬件方案设计简单,没有MCU 开发的成本,根据测试项目用例,通过上位机编写对应的测试脚本对芯片进行测试,同时在PC 上可实时监测芯片的测试状态。同时兼容不同测试接口、不同工作电压的芯片,既可以进行可靠性实验,也可以进行其他功能的测试项目。

1 样品验证平台的设计方案

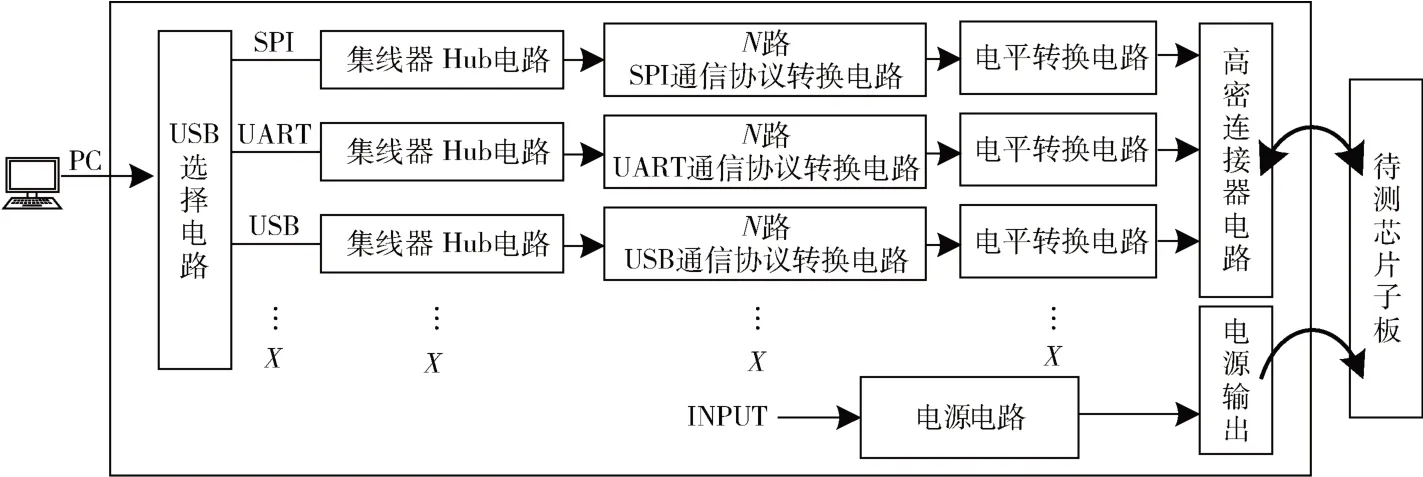

本文提出的样品验证平台方案主要以硬件电路为出发点,无MCU,仅需很少的开发成本。系统电路原理结构如图3 所示,结构上电路系统主要划分为两部分:样品验证平台和待测芯片子板,测试时通过测试线缆将两部分连接起来,对外接口通过通用串行总线(Universal Serial Bus,USB)连接PC 进行测试。样品验证平台测试系统电路[3-4]功能主要包括:USB 选择电路、通信协议转换电路、电平转换电路、测试接口电路、待测芯片子板电路。

图3 芯片样品验证平台的设计模型

其中样品验证平台包括了测试系统的主要功能电路。本方案将待测芯片子板与测试平台分开,其目的是将样品验证平台设计为一个内部标准化的测试验证平台,待测芯片子板可灵活选择,能兼容公司内部不同类型的芯片测试。同时分开设计,大大简化了待测芯片子板上的负载电路,尤其针对可靠性环境的测试项目,避免了因待测芯片子板的复杂设计而引入的影响。测试时只需将待测芯片子板通过统一的标准线缆与验证平台连接形成完整的测试系统,便于操作。

样品验证平台具有自适应和同步测试功能。自适应功能主要表现为灵活选择不同的测试接口、不同的通信链路、不同的芯片工作电压、不同的数据流向;同步测试功能表现为可以同步测试多颗芯片,本方案选定USB2.0 作为PC 的外设测试接口,而一台电脑按照USB2.0 的规范最多可以接入127 个USB 设备[5-8],所以从理论上,通过集线器扩展可以实现同步测试127 颗芯片。

基于芯片样品验证平台的设计模型,图4 为样品验证平台的具体电路结构图,图中X表示可实现多种测试接口选择,N表示可实现多颗芯片的测试。本方案从电路设计、结构大小、芯片通用接口等方面综合评估,最后X选定为3 种通信测试接口,分别为USB、通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)、串行外设接口(Serial Peripheral Interface,SPI),这3 种接口也是芯片最通用的测试接口。然后从PC 外设USB的识别效率、测试数据运行时间、平台系统功耗、待测芯片子板规格、测试芯片样品数量等各要素平衡考量,最终N选定20,即可实现对20 颗芯片的同步测试。

图4 芯片样品验证平台的电路结构图

2 自适应功能的设计

本文提出的验证平台方案是基于USB 外设可扩展的功能基础之上形成的自适应和同步测试方案。为实现通信测试接口的可选择,通信时的数据流向自动选择,芯片工作电压可选择,因为电路设计中不涉及MCU主控电路,本文针对这几部分电路分别做了自适应设计电路。

2.1 通信接口的自适应设计

本文提出的验证平台方案支持3 种不同类型的通信测试接口,分别为SPI、UART、USB 通信接口,3 种通信链路在物理上是相互独立的。不管是哪种通信接口,到PC 端都汇集到一个USB 端口,因此通信接口的自适应设计需要通过USB 选择电路来实现。

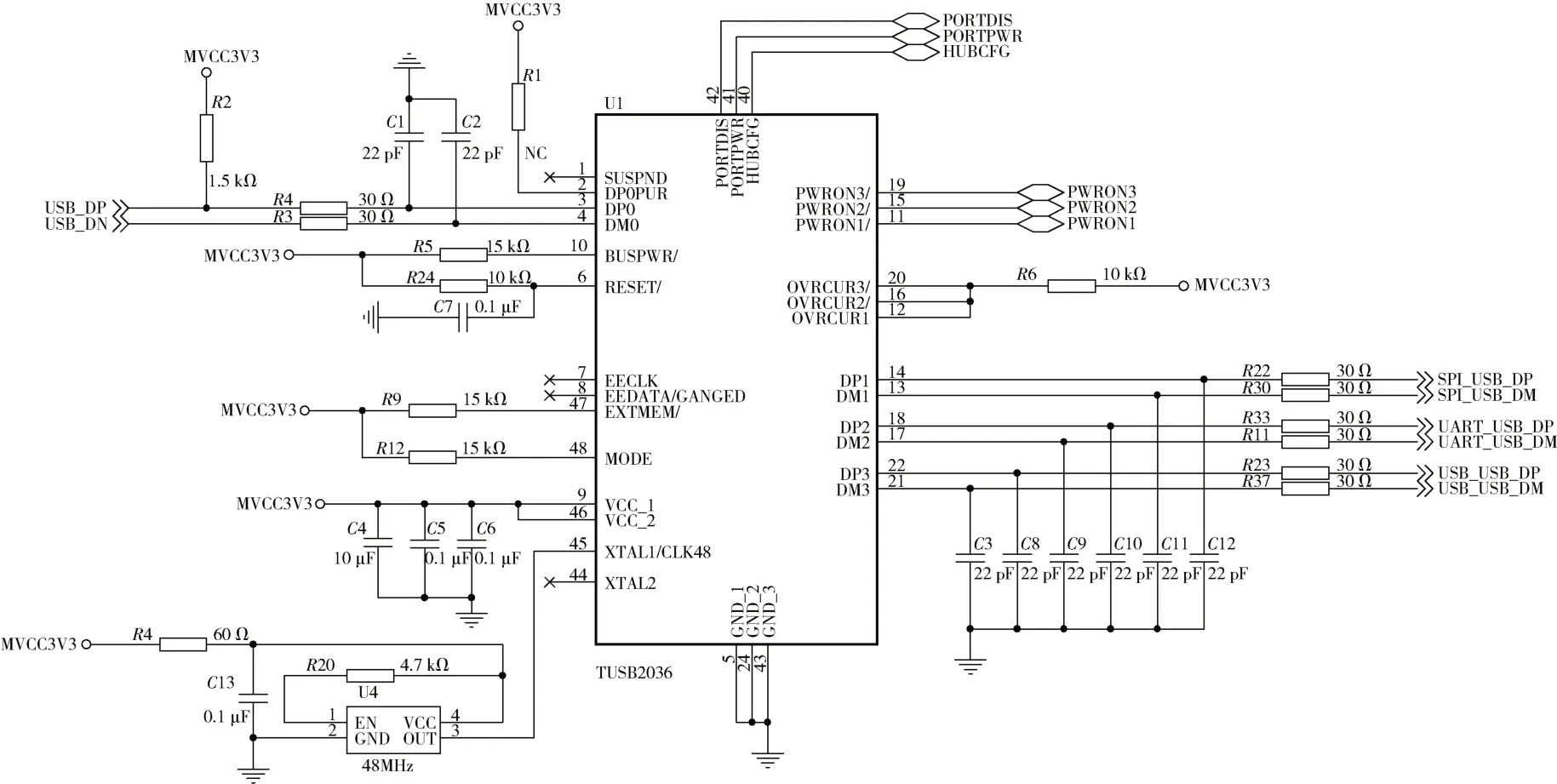

图5 为通信接口的自适应电路原理图,通过TUSB2036 芯片的POWERON 等信号配置,USB 选择电路实现了通信链路的模式选择。以SPI 通信接口测试为例,当待测芯片的通信测试接口为SPI 时,PC 端通过USB 选择电路进入SPI 通信测试模式,然后通过两级Hub(多端口集线器)将20 对扩展后的USB 信号分别通过USB 转SPI 的协议转换电路,转换为20 组SPI 信号,与待测芯片的20 组SPI 信号在高密连接器接口对接,从而实现对20 个芯片的同步测试。其中一级选用1:4 端口的Hub 芯片,二级选用1:7 端口的Hub 芯片。

图5 通信接口的自适应电路原理图

2.2 电源电压的自适应设计

为了支持不同种类芯片的测试,本方案提供了多种输出电压的选择。设计上,电源电压的自适应[9]主要通过大功率可调节的电源模块来实现,大功率用来满足20 颗待测芯片子板的功耗,可调节功能通过不同的反馈电阻值切换来实现不同芯片的工作电压选择。此方案不仅可以对不同工作电压的芯片进行测试,也可对同一种类芯片进行电压拉偏实验测试。测试时,通过验证平台上的电源端子用指定线缆将待测芯片子板连接起来。电路原理图如图6 所示。

图6 电源电压的自适应电路原理图

方案中,电源设计[9]按照功能划分均采用独立供电的方式,验证平台主板和待测芯片子板的电源分开设计,可灵活实现各功能的电源开关切换。同时为了节省功耗,验证平台的每一种通信链路电源也采用了独立分开供电的方式。独立供电的方式除了能实现灵活开关切换,更有利于不同功能模块的功耗测试。本方案涵盖了目前芯片所需要的多种电压范围,可实现0.69 V~5.5 V范围的任意输出电压。

2.3 测试接口的自适应设计

本方案支持SPI、UART、USB 3 种通信接口的待测芯片。测试接口为验证平台上的高速连接器电路,电路设计将这3 种通信接口定义为统一的标准化接口。待测芯片子板通过线缆连接到这个标准化接口上进行相应的测试。不论待测芯片为上述3 种通信接口的哪一种,待测芯片子板只需设计一个主板上的标准化定义接口,通过线缆与主板连接,就可实现自动匹配选择。

设计中,根据通信接口信号的特点,验证平台的高速连接器电路,图7 为测试接口的自适应电路原理图,将20 组SPI 信号和20 路UART 信号分别定义到单端50Ω 阻抗的高速[10-11]连接器端,20 路USB 信号定义到差分100 Ω 阻抗的高速连接器端[12-13]。这样设计的目的是为了保证测试信号的完整性[14-15],进一步降低因线缆等其他因素带来的信号衰减和引入的干扰。

图7 测试接口的自适应电路原理图

2.4 电平转换的自适应设计

在通信链路中包括电平转换电路,它的作用有3 点:(1)为了适应不同工作电压的测试芯片,需要将通信接口信号做电平匹配[1-2],确保传输数据在同一参考水平,不发生跳变;(2)确保在长距离的通信链路上信号不发生衰减,给信号适当的驱动能力,保证信号完整性;(3)在通信过程中,数据具有一定的方向性,既有单向传输,也有双向传输,电平转换电路设计是根据信号的方向性,设计为双向自适应的电平转换电路,同时实现了主从设备的自适应选择。

图8 为电平转换的自适应电路原理图,IC_VCC 为待测芯片的工作电压,电平转换自适应待测芯片的工作电压。同样,电平转换自适应设计除了适用于不同工作电压的待测芯片测试,也适用于同一种芯片的电压拉偏实验测试。

图8 电平转换的自适应电路原理图

3 同步测试功能的设计

对于测试样片数量多、测试时间长的测试项目用例,多芯片同步测试是非常必要的,多芯片同步测试不仅可以提高测试效率,更是对人力、资源设备、测试时间大幅度的节约,同时也能保证测试样品的环境一致性、测试结果一致性。

本文提出的验证平台方案一套测试平台即可对20 颗芯片进行同步测试,目前限定支持对SPI、USB、UART 3种不同通信接口的芯片测试。

3.1 同步测试设计

本文的多芯片同步测试的思路主要源于PC 上外设USB 端口的可扩展性,按照USB2.0 的规范,一台电脑最多可以接入127 个USB 设备,但并不是同步测试的芯片越多就越好,样品验证平台需要从各方面进行可行性评估。(1)要对PC 枚举识别USB 设备[7-8]的时间进行评估,每一颗芯片对应一个设备ID,设备越多,测试启动时间就越长;(2)同步测试的芯片越多,增加电路设计的复杂程度,同时样品验证平台和待测芯片的规格尺寸也会相应增加,需要考虑测试仪器设备的箱体体积;(3)样品验证平台需要给待测芯片子板提供电源,同步测试的芯片越多,功耗就会越大,不同的芯片,功耗也相差甚远,这会对电源设计提出很大的挑战;(4)同步测试的芯片越多,通信信号线就越多,也会增加高密连接器电路的设计难度,降低对测试接口的易用性。

在芯片样品验证测试实验中,77 颗通常作为测试样品数量,综合以上各种因素评估,本方案限定于对20 颗芯片的同步测试。电路设计上,通过两级集线器Hub 扩展出20 个USB 端口,然后每个端口通过协议转换芯片,将USB信号转换成芯片对应的通信接口,到达待测芯片。图9 为SPI 通信接口的其中一种类型的待测芯片子板电路。

图9 待测芯片子板的电路

3.2 同步测试方法

样品验证平台同步测试时,样品验证平台的测试连接示意图如图10 所示。首先选定待测芯片的子板,安装好待测试的芯片,然后根据测试项选择用长线或短线的高密连接线缆,将待测子板与验证平台连接起来;其次根据待测芯片需要的工作电压,将验证平台上的输出电源切换到所需的工作电压档位,再用专用电源线缆将电测芯片子板与验证平台连接起来。

图10 样品验证平台的测试连接示意图

与此同时,明确待测芯片的通信接口是目前所支持SPI、UART、I2C 3 种通用通信接口任意一种,通过USB 选择电路匹配相应的通信链路,为了节省功耗,也可以把其他两路通信链路的电源关掉。待测试系统准备就绪,连接12 V 的直流外供电电源。如果测试项目为可靠性等实验项目时,将待测芯片子板放置在测试仪器箱体里,只需将线缆从箱体的出线口伸出来与验证平台连接即可。最后USB 线连接PC 端到样品验证平台,上位机按照测试项目编写不同测试项的脚本,运行相应的程序开始测试。

测试启动前,PC 端为每个待测芯片编码属于自己的ID,实时监测每一颗待测芯片的动态测试状态,同时根据采集数据,在线生成并保存对应的测试结果报告。图11 为样品验证平台的测试界面,图下方显示的为测试芯片的实时测试状态,左上方记录了每颗芯片的测试数据结果,右上方为脚本编写区。

图11 样品验证平台的测试界面

3.3 同步测试范围

样品验证平台的系统电路结构中将样品验证平台与待测芯片子板分开设计,目的是兼容各类测试实验。样品验证平台与待测芯片子板之间分别配备了长、短线缆,在常温环境下进行的测试项目,可以通过短线缆连接验证平台与子板进行测试;针对特定的可靠性测试实验,需要将待测芯片子板放置在模拟应用场景的温度箱里,通过长线缆连接外面的验证平台,PC 端控制验证平台进行测试。

目前可实现的测试项目包括:芯片功能测试、随机数采集测试、功耗测试、电压拉偏试验测试、可靠性试验测试、通信测试等;支持SPI、UART、I2C 3 种通用通信接口的芯片测试;支持工作电压范围为0.69 V~5.5 V 的芯片测试。

4 样品验证平台的测试实现

样品验证平台已完成芯片样品验证测试的各类测试项目:同步筛片测试、同步可靠性测试、同步随机数采集测试等,测试过至少3 种不同类型的芯片,经实测验证是一种可靠的、高效的测试方法。

4.1 自适应测试效果

根据以上四部分的自适应设计,自适应功能实现了对SPI、USB、UART 3 种不同通信接口的芯片测试,可实现通信链路的自由选择;实现了在0.69 V~5.5 V 范围工作电压的芯片测试,通过选择键自由切换选择所需要的供电电压;实现了3 种接口的信号定义在统一标准化的高密连接器上,考虑了信号阻抗特征,兼容性强、自适应、简单、便捷;实现了通信数据主从模式的自动选择,且保证了信号的完整性[2,15]。

4.2 同步测试的效果

本方案的样品验证平台一套平台可实现20 颗芯片的同步测试。对于样品数量为77 颗的测试项目,也可以搭建4 套系统,通过级联的方式将4 套平台同时进行测试,仅用一台PC,通过USB 集线器功能即可实现同步测试80 颗芯片样片,这样一个测试循环周期就能完成所有样品数量的全部测试,大幅缩短了测试时间,释放了测试资源。

4.3 样品验证平台的实际对比效果

样品验证平台除自适应和同步测试功能外,测试时还可以实时监测每颗芯片的测试状态,同时自动生成测试报告。另外,将验证平台和待测芯片子板分开设计的思路,一方面简化了待测芯片的电路设计,增加了测试平台稳定性;另一方面,也增加了使用上的灵活性。表1列出了样品验证平台与传统测试方案的功能对比。

表1 样品验证平台与传统测试方案的功能对比

可靠性测试循环周期时间都比较长,传统单板的测试方法显然是不可行的。多芯片同步自测试方法既不能对芯片的测试状态进行实时监控,测试程序也不能灵活编写,更重要的是仅适合特定的测试项目,测试项目受到一定的局限性。芯片样品验证平台方案相比传统测试方案,既提高了测试效率,也实现了灵活性。

5 结论

目前芯片样品验证平台不仅可以作为内部的一款标准化芯片样品验证测试平台,也可以作为一款业内通用的自适应同步测试设备。设计方案思路更是值得借鉴,自适应同步测试简化了测试流程,节约了开发成本、时间成本、设备资源成本,提高了测试效率和灵活性。未来将进一步优化自适应设计方面的功能,打造一款覆盖测试项目更全面、更智能化的芯片样品验证平台。