56 Gbps高速信号传输系统仿真验证设计*

李宝峰,黎铁军,刘勇辉,马柯帆,罗煜峰,姚信安

(国防科技大学计算机学院,湖南 长沙 410073)

1 引言

随着高性能计算机中的信号传输速率超过25 Gbps,传统NRZ(Non-Return-to-Zero)信号对传输链路设计的限制更加严苛[1],通过提高波特率来实现高带宽传输的难度越来越大[2 - 4]。而PAM4(4 Pulse Amplitude Modulation)信号采用4个电平表征符号,每个符号编码2比特信息,相同波特率下的带宽是NRZ的1倍,在25 Gbps以上高速信号传输系统中广泛应用。但是,PAM4信号的信噪比相对NRZ劣化了约9.5 dB[5],相同电平幅度下的眼高只有NRZ的1/3,更易受到噪声影响,导致误码率大幅增加[6 - 9]。

新一代高性能计算机的高速信号传输系统采用56 Gbps PAM4信号实现,传输通道跨越多块PCB(Printed Circuit Borad)板和多级连接器,走线长度长、阻抗不连续点多,信号完整性设计面临极大挑战。为提高设计成功率,本文提出了面向全通道的56 Gbps高速信号传输系统仿真验证方案,通过仿真与测试相结合的方法,建立了更接近实际情况的跨越多PCB和多连接器的复杂传输通道模型,并对其进行了全通道的协同仿真实验。通过多次仿真实验与设计优化迭代验证了该设计较好地预测了56 Gbps高速信号传输系统的性能瓶颈,有力保障了56 Gbps PAM4高速信号的稳定传输。

2 仿真验证设计

2.1 仿真验证方案

56 Gbps高速信号传输系统的传输通道由1块背板BPM、3块子板(上层互连接口板ZNIB、下层互连接口板ZNIT和互连通信板NRM)和3级连接器组成,PCB走线层采用松下M7N(MEGTRON7系列低介电常数DK(Dielectric Constant)材料)板材,铜箔类型为极低轮廓HVLP(High-frequency Very Low Profile)铜箔。为提高仿真精准度,本文提出了面向全通道的仿真验证方案。第1步,通过仿真与测试拟合方法确定板材仿真参数;第2步,通过测试确定连接器仿真参数;第3步,提取传输通道上各传输链路的PCB设计模型,建立全通道HFSS(High Frequency Structure Simulator)仿真模型;第4步,对仿真模型进行全通道的TDR(Time Domain Reflectometry)仿真、S参数仿真和有源仿真,根据仿真结果验证56 Gbps高速信号传输系统设计的可靠性。

仿真验证的硬件环境:3台Windows 7服务器,每台服务器配备2颗Intel Xeon E5530 12核CPU,内存160 GB。软件环境:ANSYS SIwave 2018.2.0、HFSS 2018.2.0、ANSYS HPC软件套件和KEYSIGHT ADS2017软件。

2.2 确定板材参数

高速信号仿真中,PCB板材的介电常数DK、损耗角正切DF(Dissipation Factor)值及铜箔粗糙度是主要输入参数[10]。通过对真实测试板进行仿真与测试结果的拟合,不断调整优化PCB板材的DK、DF值及铜箔表面粗糙度,以得到与测试相吻合的仿真结果。

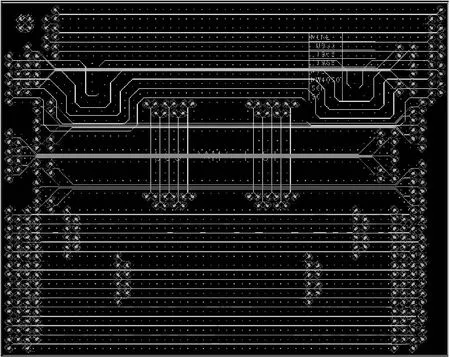

制作的56 Gbps-PAM4测试板各通道的出线情况如图1所示;测试板所采用的板材为M7N板材,铜箔类型为HVLP铜箔,各通道中的过孔均能满足最小的过孔残桩要求。

Figure 1 56 Gbps-PAM4 test board图1 56 Gbps-PAM4测试板

采用矢量网络分析仪VNA(Vector Network Analyzer)测量得到该通道的S参数结果,如图2所示。

Figure 2 S parameter of VNA measured channel图2 VNA实测链路S参数

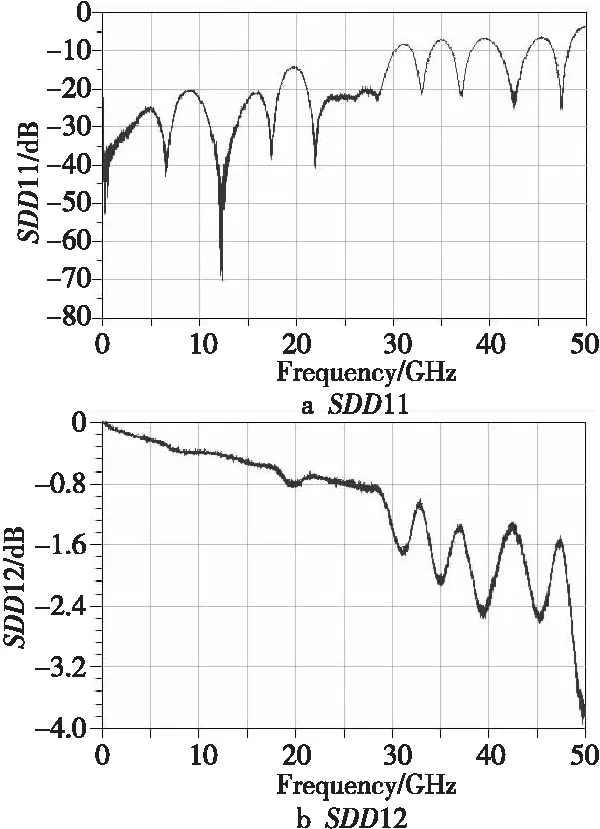

在SIwave软件中提取相应的模型并导入HFSS仿真软件进行仿真参数的提取,仿真模型如图3a所示。该模型中,为达到仿真与测试环境的一致性,在该模型的4个端口处分别添加了4个SMA(Sub-Miniature-A)模型。仿真与测试的对比结果如图3b所示。

Figure 3 Simulation model and comparison of simulation & test results图3 仿真模型和仿真与测试结果对比

图3所示为仿真与测试的插入损耗和回波损耗结果对比图。由图3可知,两者的插入损耗曲线拟合得较好,30 GHz之前两曲线完全重合;回波损耗曲线在第2个谐振点可以很好地对应上,且随频率变化的趋势相同。以上仿真和测试的对比结果较好地说明了当铜箔粗糙度为0.3 um时,采用表1所示的DK、DF值,可较好实现仿真与测试结果的一致性,仿真可信度较高。

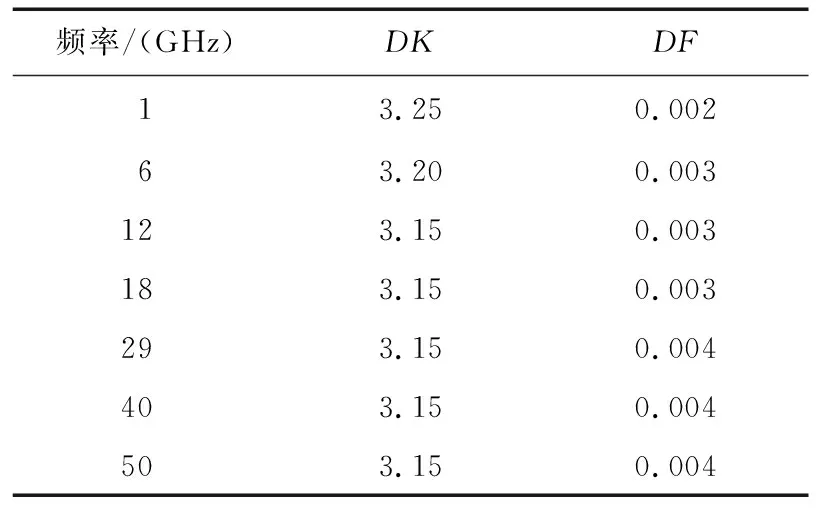

Table 1 DK/DF values after simulation and test fitting 表1 仿真与测试拟合后的DK/DF值

2.3 确定连接器参数

为提高信道中的数据传输速率,减少由于损耗引起的信号完整性问题,高速连接器在设计时会综合考虑引脚排列、板卡间距、介质材料和信号完整性等因素,提供低损耗、低串扰和阻抗匹配性能强的高速连接器[11]。

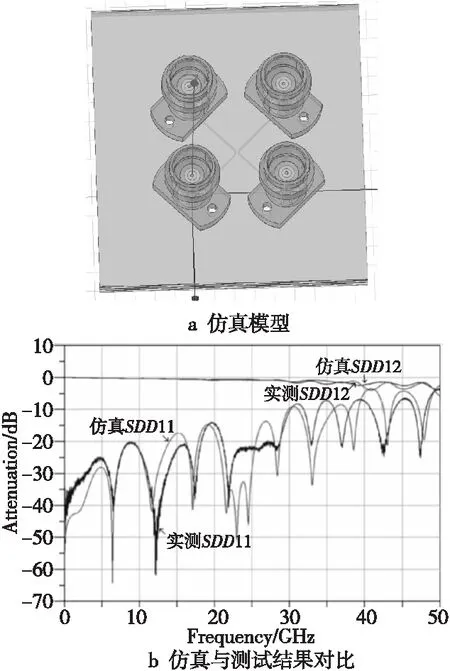

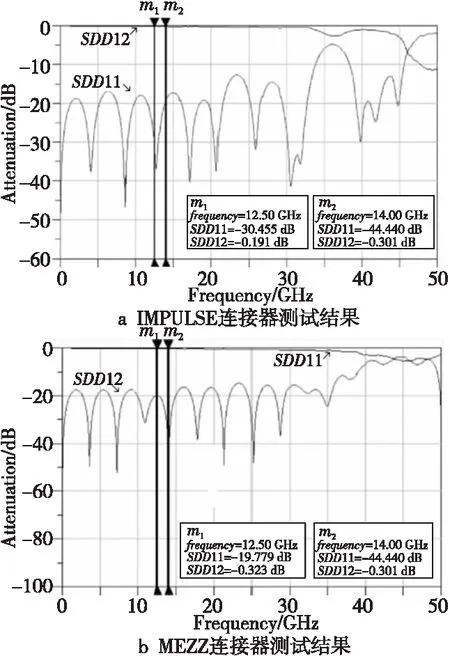

56 Gbps高速信号传输系统中的最长通道采用了3级连接器传输链路,共使用了IMPULSE连接器和MEZZ连接器2种类型的高速连接器。分别对2种连接器采用VNA进行传输参数的测试,得到的结果如图4所示。

Figure 4 Results of connector test 图4 连接器测试结果图

2.4 建立全通道HFSS仿真模型

2.4.1 传输通道拓扑结构

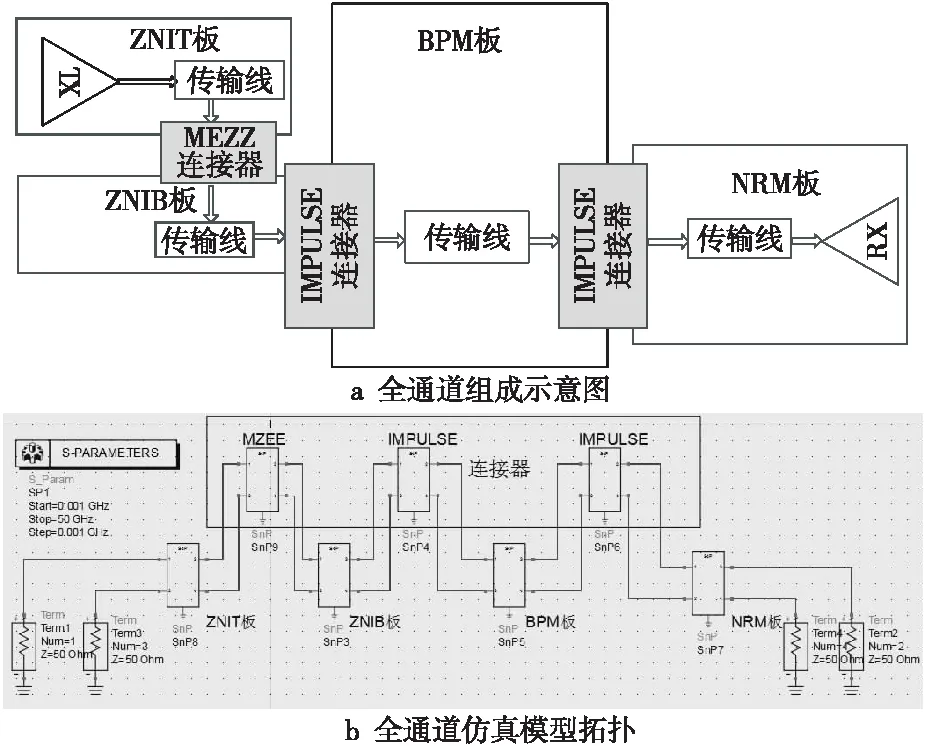

为保证仿真验证结果的代表性和覆盖性,本文选取了56 Gbps高速信号传输系统中长度最长、构成最复杂的通道作为仿真对象。如图5a所示,该通道跨越3级连接器和4块PCB板,分别为ZNIT板、ZNIB板、BPM板以及NRM板、2级IMPULSE连接器和1级MEZZ连接器。由于信号经过的PCB板较多,传输损耗加大;经过的连接器较多,链路的阻抗一致性变差,从而使得56 Gbps PAM4高速信号的传输面临巨大挑战。

Figure 5 Composition of full channels and simulation model topology 图5 全通道组成与仿真模型拓扑

为预先验证设计的有效性,本文采用HFSS仿真软件分别对各PCB传输链路进行提取,进而在ADS(Advanced Design System)仿真软件中建立了全通道HFSS仿真模型,如图5b所示。

2.4.2 BPM传输链路模型

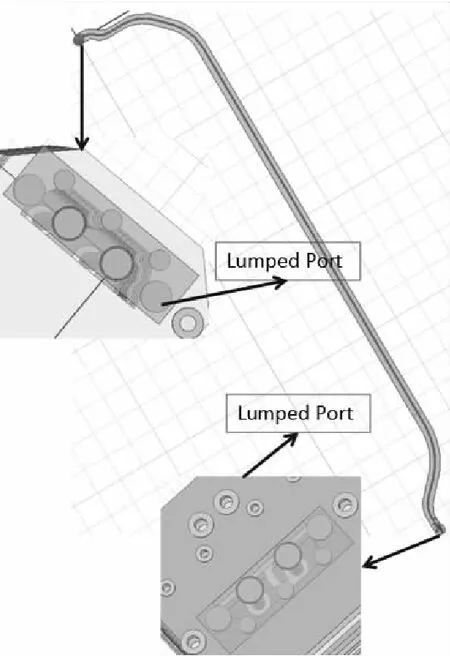

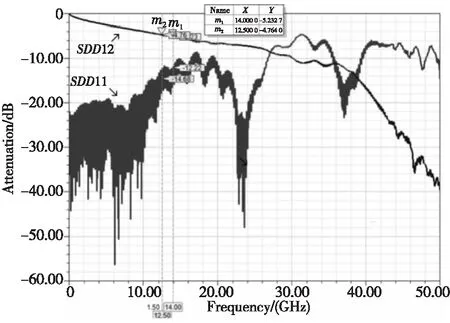

对BPM板创建的仿真模型如图6所示。BPM板共计28层,所选择的仿真网络位于S07层,线长为329.419 4 mm(12.969 inch),线宽、线距为9 mil/12 mil/9 mil,信号的目标阻抗为92 (1±10%)Ω,过孔的成品孔径为0.31 mm(12.20 mil);板厚为5.984 mm(235.59 mil),最大板厚孔径比设计为19.3∶1。该信号一端为NRM板的连接器,一端为ZNIB板的连接器,其中NRM板的连接器位于Bottom层,背钻需从Top层钻至GND06层;ZNI板的连接器位于Top层,背钻需从Bottom层钻至GND08层,该端所经历的过孔通道较长。走线2端均添加Lumped Port仿真端口,仿真的中心频点为14 GHz,扫频在10 MHz~50 GHz,步进(Step)为0.001 GHz。所创建的模型中过孔的背钻均能够钻至与走线层相邻的信号参考层,因而过孔残桩对信号的影响可以忽略[12 - 15]。仿真结果如图7所示,图7中分别给出了该模型的回波损耗和插入损耗结果,并分别列出了信号在12.5 GHz频点和14 GHz频点时的传输损耗。

Figure 6 Manual HFSS model of BPM board图6 BPM板HFSS手动建模模型

Figure 7 Simulation results of BPM board图7 BPM板仿真结果

由仿真结果可知:在12.5 GHz频点处,信号的插入损耗值为-4.764 dB@12.5 GHz,回波损耗值为-14.68 dB@12.5 GHz;在14 GHz频点处,信号的插入损耗值为-5.232 7 dB@14 GHz,回波损耗值为-12.22 dB@14 GHz。信号的传输损耗表现较好。

2.4.3 ZNIT传输链路模型

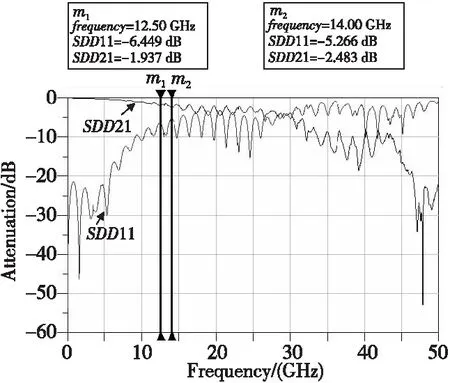

对ZNIT板创建的仿真模型如图8所示。模型中过孔的背钻均能满足最小的残桩要求,因而过孔残桩对信号的影响可以忽略。仿真结果如图9所示。

Figure 8 Manual HFSS model of ZNIT board图8 ZNIT板HFSS手动建模模型

Figure 9 Simulation results of ZNIT board图9 ZNIT板仿真结果

由仿真结果可知:在12.5 GHz频点处,信号的插入损耗值为-1.937 dB@12.5 GHz,回波损耗值为-6.449 dB@12.5 GHz;在14 GHz频点处,信号的插入损耗值为-2.483 dB@14 GHz,回波损耗值为-5.266 dB@14 GHz。信号的传输损耗表现较好。

2.4.4 ZNIB传输链路模型

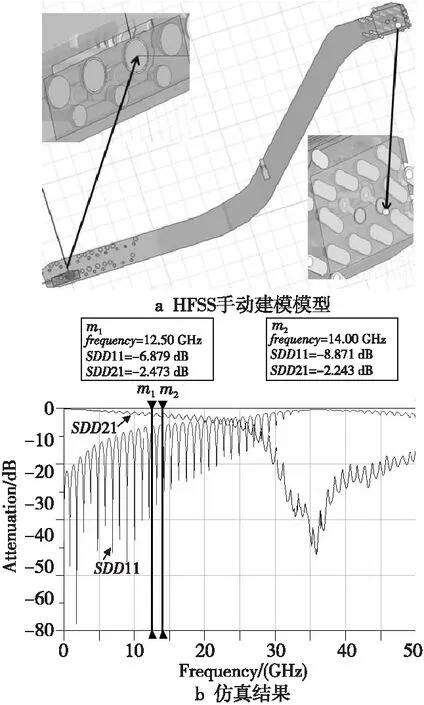

对ZNIB板创建的仿真模型如图10a所示,仿真的插入损耗SDD21和回波损耗SDD11结果如图10b所示。

Figure 10 Manual HFSS model and simulation results of ZNIB board图10 ZNIB板HFSS手动建模模型及仿真结果

由仿真结果可知:在12.5 GHz频点处,信号的插入损耗值为-2.473 dB@12.5 GHz,回波损耗值为-6.879 dB@12.5 GHz;在14 GHz频点处,信号的插入损耗值为-2.243 dB@14 GHz,回波损耗值为-8.871 dB@14 GHz。信号的传输损耗表现较好。

2.4.5 NRM传输链路模型

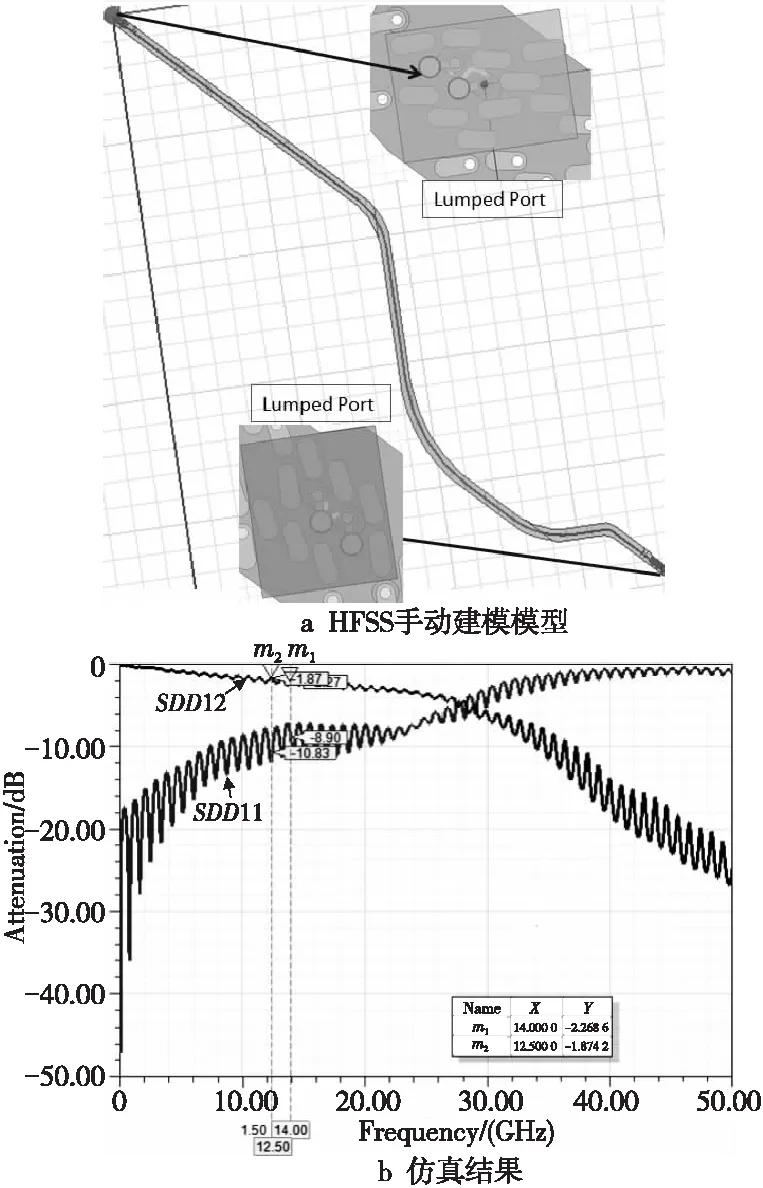

对NRM板创建的仿真模型如图11a所示,仿真的插入损耗和回波损耗结果如图11b所示。

Figure 11 Manual HFSS model and simulation results of NRM board图11 NRM板HFSS手动建模模型及仿真结果

由仿真结果可知:在12.5 GHz频点处,信号的插入损耗值为-1.87 dB@12.5 GHz,回波损耗值为-10.83 dB@12.5 GHz;在14 GHz频点处,信号的插入损耗值为-2.26 dB@14 GHz,回波损耗值为-8.90 dB@14 GHz。信号的传输损耗表现较好。

3 仿真验证结果

本节对建立的全通道仿真模型进行TDR仿真、S参数仿真和有源仿真实验。

3.1 TDR仿真结果及分析

根据图5b所搭建的全通道仿真模型拓扑图,进行全通道TDR仿真分析,通过TDR仿真可以查看到全通道中阻抗突变的点,从而有针对性地进行优化。得到的仿真结果如图12所示。

Figure 12 TDR simulation results图12 TDR仿真结果

从TDR仿真结果中可发现,全通道的阻抗基本满足目标阻抗92±10%的要求,通道中个别点处的阻抗值较低,对应为连接器与过孔相接处。由于此处突变较短,因此对全通道整体影响不大。

3.2 S参数仿真结果及分析

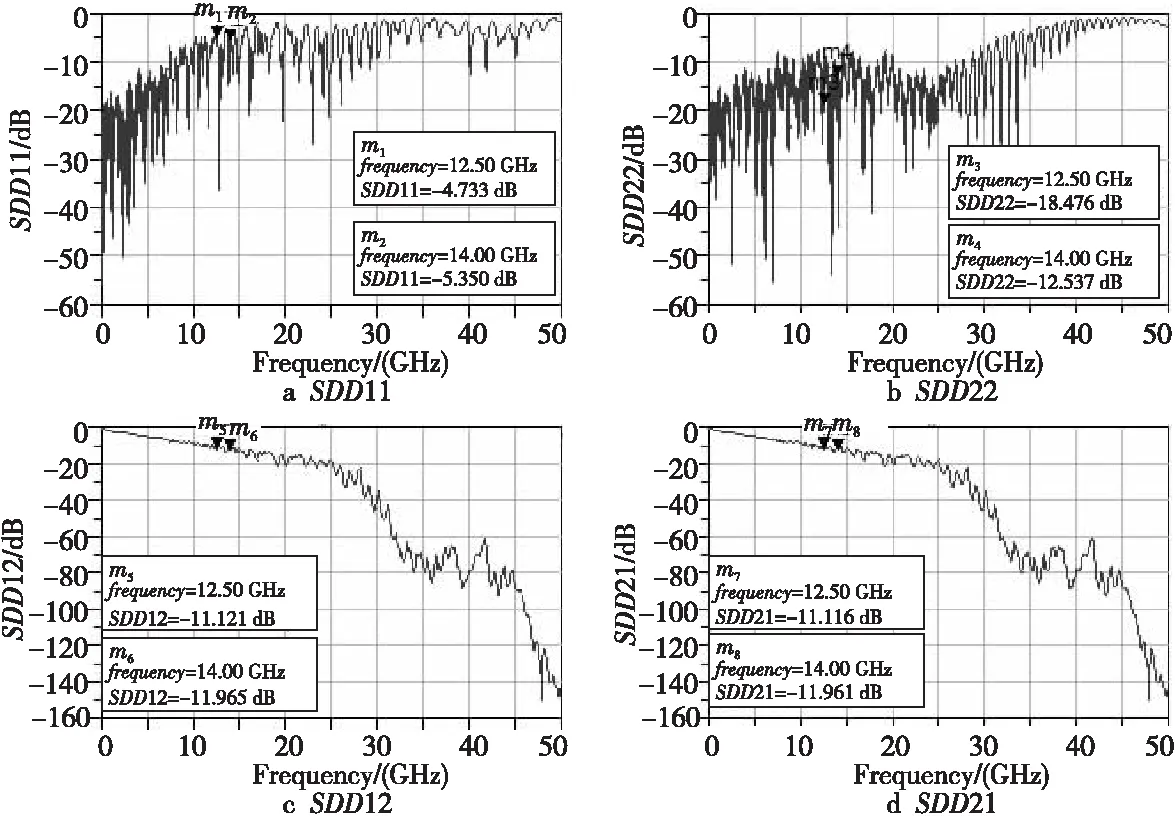

根据图5b所搭建的拓扑图,进行全通道S参数仿真,得到的全通道的S参数结果如图13所示。

Figure 13 Simulation results of S parameter of full channel 图13 全通道S参数仿真图

由全通道的S参数仿真结果可以看出,插入损耗在12.5 GHz频点处为-11.121 dB@12.5 GHz,在14 GHz频点处的插入损耗值为-11.965 dB@14 GHz;回波损耗在12.5 GHz频点处为-18.476 dB@12.5 GHz,在14 GHz频点处的回波损耗值为-12.537 dB@14 GHz。全通道的传输损耗较低。

3.3 有源仿真结果及分析

在得到全通道S参数的基础上进行有源仿真,搭建的仿真拓扑图如图14所示。图14中全通道S参数导入的文件为利用图5b所示拓扑仿真得到的全通道S参数结果。

Figure 14 Topology of active simulation图14 有源仿真拓扑图

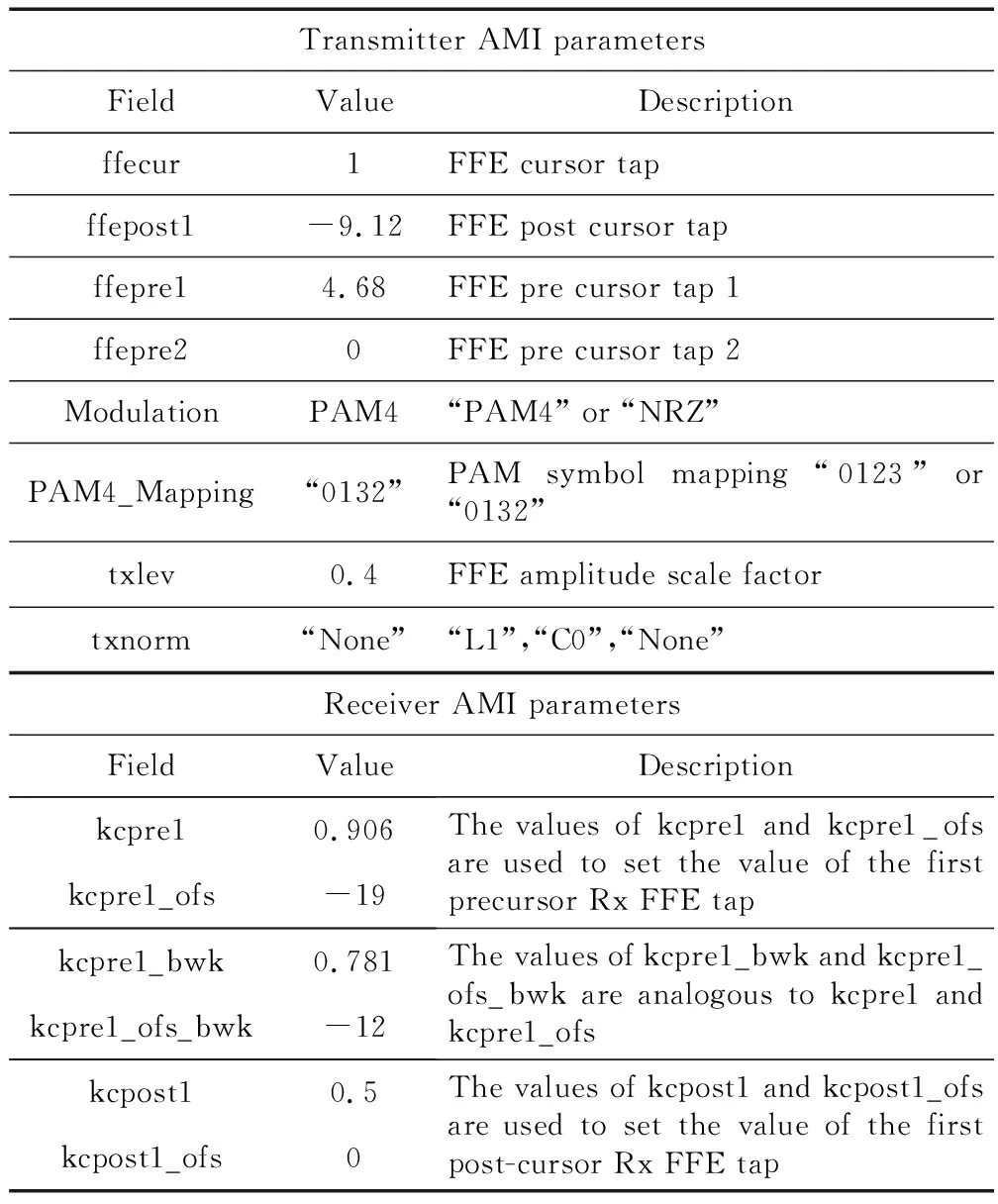

图14中,接收端TX和发送端RX的芯片模型采用厂家提供的IBIS-AMI模型代替,该模型可设置不同的信号调制方式,作为与56 Gbps-PAM4信号的对比,此处同时仿真了25 Gbps-NRZ信号。链路跨板且有多级连接器长,需要对TX和RX端进行均衡参数的设置才能够在接收端得到眼图,实现有效的传输。基于全通道的传输损耗,发送端和接收端AMI参数设置如图15所示。

仿真的速率分别设置为25 Gbps和56 Gbps,图14中该模型的第2部分为芯片的封装参数,此处采用芯片厂家提供的封装S参数文件;该模型的第3部分为CHANNEL,该部分为所需要仿真的全通道,此处导入图5b中仿真得到的全通道S参数文件;该模型的第4部分为眼图探针,作为仿真结果的查看窗口,此处分别在接收端芯片前添加一个差分探针,查看未经接收端芯片处理的眼图效果及在接收端芯片后添加一个探针,查看对比经过接收端芯片后的眼图效果。具体的眼图仿真结果如图15所示。

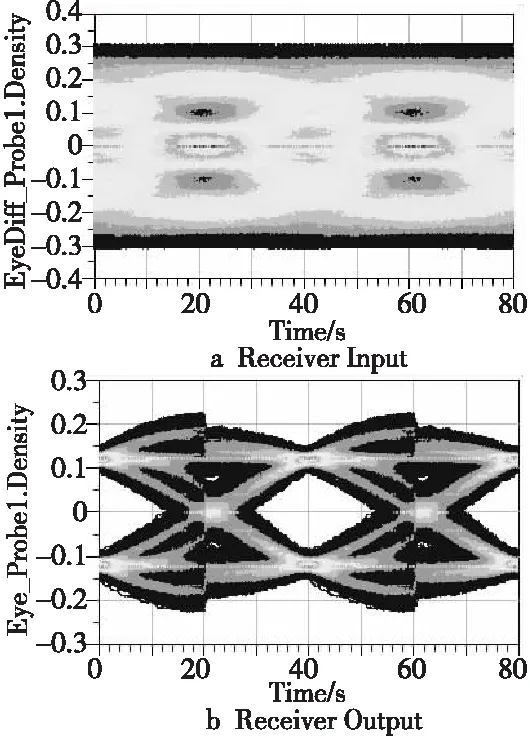

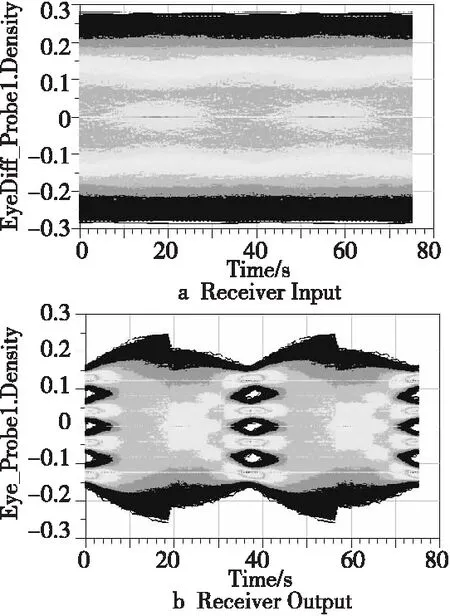

Figure 15 25 Gbps-NRI simulation results of eye pattern图15 25 Gbps-NRI 眼图仿真结果

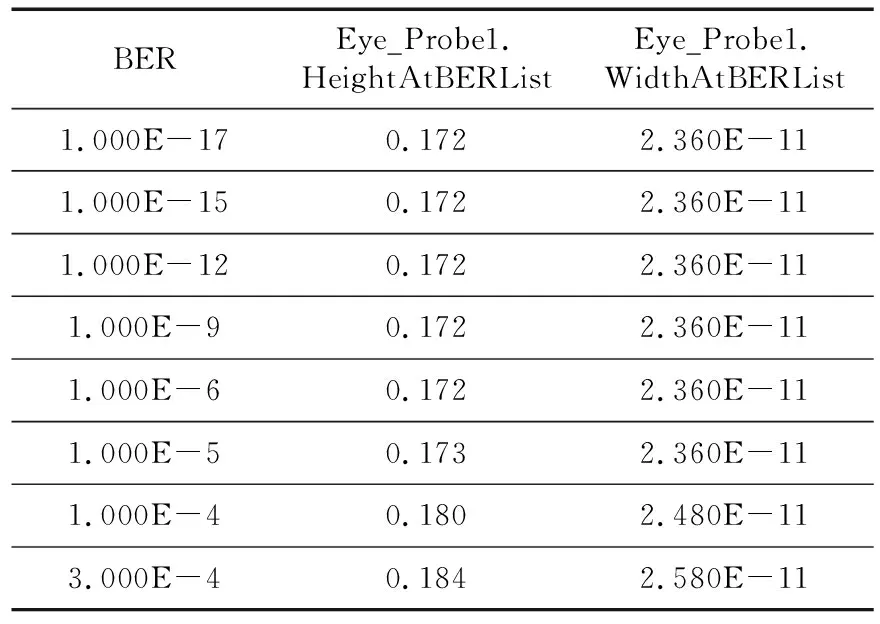

图15为25 Gbps-NRZ的眼图仿真结果。由图15可知,在Receiver Input端未经过接收端芯片均衡时,眼睛完全关闭;在Receiver Output经过接收端芯片均衡后,眼睛的张开情况得到较大的改善。图16a给出了该眼图的具体眼高和眼宽值。由图16a可知,当误码率为1.000E-6时,能够得到张开的眼睛,此时的眼高为0.172,眼宽为2.360E-11;但当误码率超过1.000E-6时,眼图成闭合趋势,得不到信号质量良好的眼图。

a 眼图误码率

b 不同误码率下的眼高和眼宽Figure 16 25 Gbps-NRZ eye map and eye height & eye width of eye pattern with different error rates图16 25 Gbps-NRZ眼图误码率及在不同误码率下的眼高和眼宽

图17为56 Gbps-PAM4的眼图仿真结果,在Receiver Input端未经过接收端芯片均衡时,眼睛完全关闭;在Receiver Output经过接收端芯片均衡后,眼睛的张开情况得到较大的改善。图18b给出了具体的眼高眼宽值。

Figure 17 56 Gbps-PAM4 simulation results of eye pattern图17 56 Gbps-PAM4眼图仿真结果

Figure 18 56 Gbps-PAM4 eye map and eye height & eye width of eye pattern with different error rates图18 56 Gbps-PAM4眼图误码率及在不同误码率下的眼高和眼宽

Table 2 Transmitter and receiver AMI parameters表2 发送端和接收端AMI参数

由图18b可知,当误码率为1.000E-6时,能够得到张开的眼睛,但误码率超过 1.000E-6时,眼睛关闭,得不到眼图。

对比图16a和图18a的眼图仿真结果可以发现,在当前跨板多级连接器长链路传输系统中,通过对发送端和接收端的均衡设置,系统能够有效地实现25 Gbps-NRZ和56 Gbps-PAM4信号的传输;同时,在相同的链路环境下,系统传输NRZ信号和PAM4信号的误码率相同,均为1.000E-6,但系统的传输速率却从25 Gbps上升到了56 Gbps,传输速率大为提高。

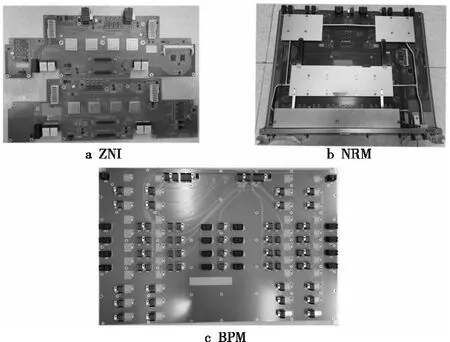

3.4 结论与工程实现

从全通道的TDR仿真可知,全通道的真实阻抗基本满足设计的目标阻抗要求,减少了信道传输过程中因阻抗匹配不一致而造成的反射问题;S参数仿真结果表明,全通道的传输损耗较低,14 GHz处的插入损耗低于-12 dB;有源仿真中当加入均衡时能够有效地得到张开的25 Gbps-NRZ和56 Gbps-PAM4眼图,此时全通道的传输误码率为1.000E-6。全通道的仿真结果表明,在当前仿真验证设计中能够有效地实现56 Gbps PAM4信号的传输。本文所述成果已经应用于本单位高性能计算机系统的工程构建,实际应用结果表明,系统能很好地保证56 Gbps PAM4高速信号的稳定传输,系统所需印制板如图19所示。

Figure 19 System engineering implementation图19 系统工程实现

4 结束语

本文针对56 Gbps高速信号传输系统进行仿真分析研究,基于信号完整性,通过对仿真板材参数的精准确定、连接器参数的确定及各传输子模块仿真模型的建立,基于仿真结果实现了56 Gbps-PAM4信号的稳定传输。通过仿真结果可知,采用仿真与测试的拟合方法可较好地确定板材仿真参数,为进行高速信号仿真建立基础;连接器和过孔为全通道中阻抗不连续的点,但在整个通道中由于突变较短,对通道整体性能影响较小;基于真实PCB板提取的3D仿真模型较准确地说明了各子模块的传输损耗,并把每个模块的S参数代入全通道拓扑中,通过调整均衡值仿真得到全通道的S参数与眼图满足设计要求。本文实现的传输系统仿真设计不仅为56 Gbps高速信号传输系统提供了指导,还为未来更高速率的设计打下了基础。PAM4信号传输中较为关注的传输介质的线性度及对应的群延时影响方面的研究有待进一步深入。