一种用于核与粒子物理实验数字化的多重数触发判选电路设计*

刘尚铭,曹 平,李 超,汪晓虎

(1.中国科学技术大学 核探测与核电子学国家重点实验室,安徽 合肥 230026;2.中国科学技术大学 近代物理系,安徽 合肥 230026)

0 引言

核与粒子物理主要研究原子核内部及以下层次的微观结构,为研究粒子间相互作用,人们通过数量庞大的探测器阵列和电子学设备对实验物理现象进行观测[1−2]。物理实验采用触发判选机制来滤除实验本底与探测器噪声,通过触发系统的设计从前端原始信息中筛选出有效物理事例,从而降低后端数据传输与缓存压力。

核与粒子物理实验中的触发判选技术主要有模拟硬件触发、无硬件触发、数字硬件触发三种方式。早期实验的触发系统因技术限制,通常使用模拟硬件触发方式提取前端信号特征参量并进行触发判选,如中国原子能院GTAF 谱仪[3],这些触发系统大多专用且固定,具有一定死时间,无法适应物理实验高事例率的发展需要。随着数据传输处理能力的快速提高,压缩重物质实验[4]、反质子湮灭实验[5]、大型高海拔宇宙线观测站[6]等实验开始采用无硬件触发的数据读出方法,将前端所有数据传输至后端,由后端高性能计算单元进行触发判选,但对所有数据不加区分的读出给读出系统与数据获取系统带来了更大的设计压力与资源消耗。近年来在某些实验上,如反角白光中子源GTAF-II 谱仪[7]、江门中微子实验[8],逐渐开展了基于FPGA 实时硬件的全数字化硬件触发技术研究,充分利用FPGA 并行处理能力强和实时性高的优点,对原始数据进行实时的触发判选与数据筛选。

物理实验中的触发判选一般根据有效物理事例与本底噪声的特点,设置相应的判选条件。击中多重数(Hit multiplicity,NHit)是一种常用的判选依据,在反角白光中子源GTAF-II 谱仪、大型高海拔宇宙线观测站、江门中微子实验、暗物质探测[9]等实验中被广泛应用。触发系统需要接收汇聚前端所有原始数据,并从中快速统计NHit 信息,从而完成全局触发判选。在高事例率情况下,基于数字硬件方式的NHit 触发相比于无硬件触发方式具有更好实时性,同时可以有效降低实验成本资源开销,而数字硬件触发方式需要依托具体硬件电路的实现,才能完成实际的触发判选。

针对核与粒子物理实验中的数字NHit 触发处理需求,本文设计了一种高性能数字触发判选电路。该电路支持多个通道的光纤数据传输与千兆网络通信,使用大容量高速DDR4 缓存与高性能FPGA 支持高速数据缓存与实时硬件数字触发处理。该电路灵活可扩展,可应用在不同的物理实验场景中,通过多块该电路组合可实现灵活的触发处理;同时具有一定兼容性,可作为机箱标准插卡并入某些物理实验电子学系统。通过对数字触发硬件电路的数据传输与缓存接口的测试,结果表明数字硬件电路可以实现与多个硬件间的光纤数据传输,以及与上位机间的千兆网络通信,同时支持高带宽的DDR4 数据缓存,满足电路设计需求。

1 数字触发方案

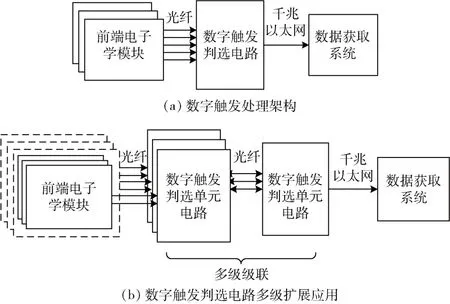

在核与粒子物理实验中,基于光纤的数据传输是一种高效的远距离数据传输方式,被广泛应用在各个物理实验中。数字触发判选电路可通过光纤与前端电子学硬件相连,通过多个光纤链路汇聚前端原始数据,同时在内部通过高速大容量缓存将其缓存在本地等待后续触发处理;在硬件上使用高性能FPGA 运行实时的NHit触发算法,通过分析原始数据的时间信息得到NHit 统计结果并进行全局触发判选;在得到触发结果后,数字触发判选电路挑选读出本地缓存中的有效物理事例数据,并通过千兆网络发送给后级数据获取系统,其触发处理架构如图1(a)所示。

由于物理实验通道数众多,在某些多通道高事例率的物理实验中,单块数字触发判选电路难以实现对所有前端数据的汇聚、读出以及触发处理。该情况下可根据物理实验的前端通道数、原始事例率、有效事例数据率等具体情况,使用多块数字触发判选单元电路进行级联扩展,从而实现灵活的触发处理操作,图1(b)展示了多块数字触发判选电路扩展的应用方式。

图1 数字触发判选电路

数字触发判选电路具备多通道光纤数据传输与千兆网络通信、大容量高带宽数据缓存、实时数据处理与触发判选能力,该电路实现不依赖具体的机箱平台,出于兼容性考虑,将数字触发判选电路设计成标准的MTCA 机箱插卡[10],实际使用时可作为单独的电子学模块独立运行,也可兼容某些物理实验的电子学系统,可插到MTCA 机箱内实现与其他插卡的数据交互,从而大大增强数字触发判选电路的灵活性与可扩展性。此外,本方法也不完全依赖于光纤技术,当前端原始数据率不高情况下,也可利用电缆技术进行数据的传输收集。

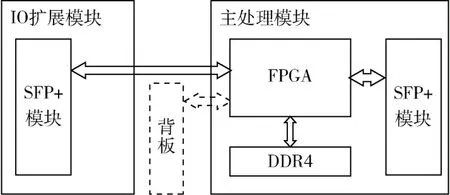

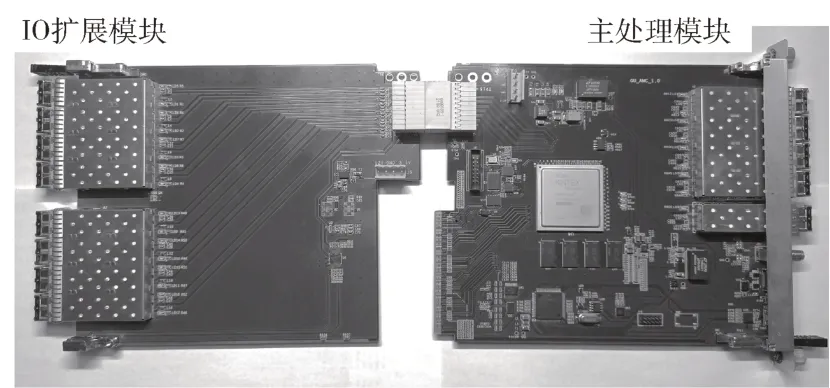

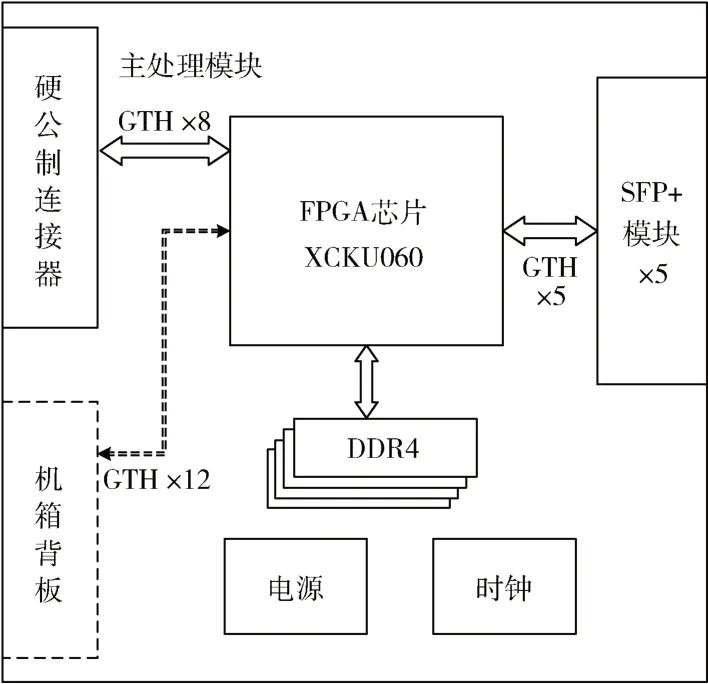

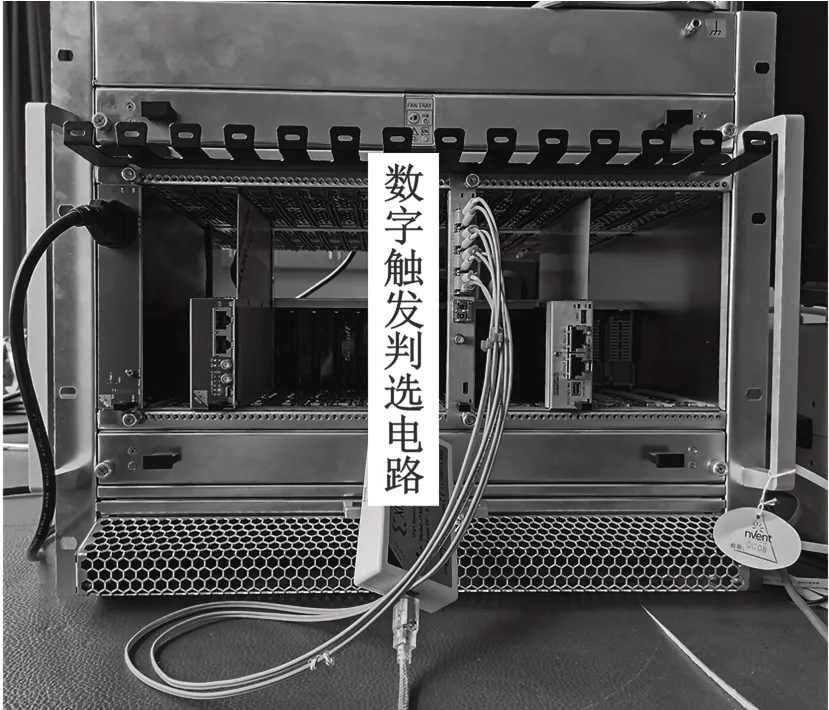

由于光纤数据传输需使用较多数量的SFP+模块,因用户插卡面板空间限制,数字触发判选电路实际上由一个负责数据传输与处理的主处理模块与一个IO 扩展模块组成,其电路结构框图如图2 所示。在主处理模块上使用1 颗高性能FPGA 芯片负责数据传输与实时处理,多颗DDR4 芯片用作大容量高速数据缓存,同时主处理模块与IO 扩展模块上布有多个SFP+模块用于多个通道的光纤数据传输与千兆网络通信,数字触发判选电路实物如图3 所示。

图2 数字触发判选电路框图

图3 数字触发判选电路实物图

数字触发判选电路基于光纤来进行高速串行数据通信,使用SFP+光模块进行光电转换,并将电信号连接到FPGA 的高速串行收发器上,通过FPGA 逻辑配置可以使各个高速串行收发器工作在不同的高速串行数据通信协议下,例如Aurora、SRIO、PCIe 等协议[11−13]。

在千兆网络通信上数字触发判选电路使用SiTCP 技术[14],SiTCP 是为高能物理实验而开发的一种网络通信技术,搭建了一种可在FPGA 芯片上运行的硬件网络通信处理单元,具有低资源消耗、低功耗等优势。从网络协议层级上来看,SiTCP 用硬件实现了MAC 层及以上层级,可将FPGA 的高速串行收发器用作网络通信的PHY层,数字触发判选电路将以太网SFP 模块插到该路的SFP+通道上,即可将该路SFP+通道用于千兆网络数据传输。

2 数字触发判选电路设计

2.1 主处理模块

主处理模块的具体电路结构框图如图4 所示,可以看到主处理模块主要由FPGA、DDR4、时钟、电源、SFP+接口电路、背板接口电路几部分组成。

到目前为止,对沈从文小说的原型研究主要集中在“少女形象”“水”“湘西世界”这三个方面,还有少数研究成果涉及沈从文小说中其他事物的原型研究。

图4 主处理模块电路结构框图

2.1.1 FPGA 与DDR4 芯 片

为了支持高速数据传输与缓存,主处理模块上使用一颗Xilinx Kintex UltraScale 系列XCKU060 型号的FPGA 芯片,该芯片具有28 个可达16 Gb/s 传输速率的高速串行收发器(GTH),支持最高传输速率达2 400 Mb/s 的DDR4 缓存芯片连接。DDR4 芯片使用Micron公司的MT40A512M16LY-083 产品,单个芯片数据总线位宽为16 bit,该内存颗粒的存储容量为8 Gb,最大时钟频率为1.6 GHz。在本数字触发判选电路中,为了实现高速数据缓存,使用4 片DDR4 芯片合并了数据总线位宽,将数据传输总线宽度扩展为64 位,数据缓存速率理论最高可达153.6 Gb/s。

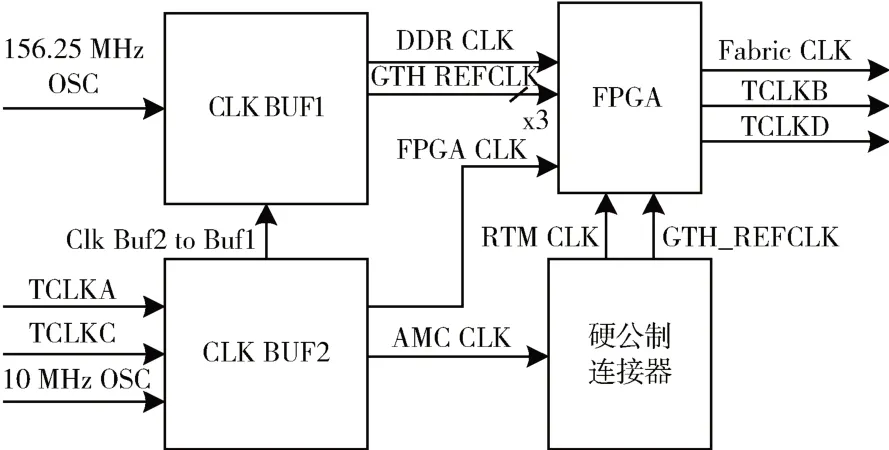

2.1.2 时钟方案

主处理模块的时钟方案如图5 所示,使用了两颗时钟扇出芯片,CLK BUF1 选择接收本地晶振的156.25 MHz 时钟,或者是CLK BUF2 扇出的时钟信号,同时将输入时钟扇出多路,输出时钟作为FPGA 多个GT bank以及DDR 接口的参考时钟。CLK BUF2 接收本地的高品质10 MHz 时钟信号,以及背板送过来的TCLKA 与TCLKC 时钟,选通其中一路并扇出给FPGA、IO 扩展模块以及CLK BUF1。同时FPGA 芯片接收IO 扩展模块通过硬公制连接器送过来的时钟,并输出两路时钟信号作为TCLKB 与TLKD 时钟送给机箱背板。通过以上的时钟电路设计可以实现灵活的时钟分配方案。

图5 主处理模块的时钟方案

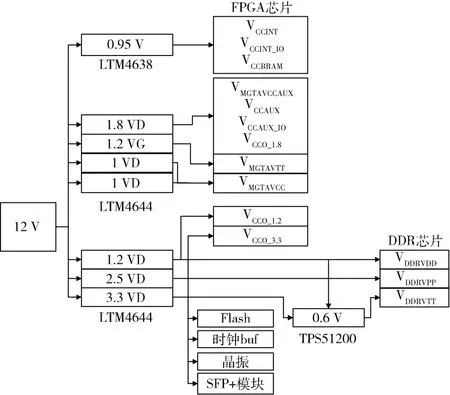

2.1.3 电源方案

图6 主处理模块的电源方案

2.1.4 SFP+接口电路

数字触发判选电路使用SFP+模块来实现光纤链路数据传输与网络通信,在主处理模块上载有5 路SFP+连接器插座与对应的屏蔽罩,将不同功能以及传输速率的商用SFP+光纤收发器安装到板卡上,即可实现不同功能与速率的高速串行数据通信。光纤链路的高速串行数据传输使用最高传输速率为8.5 Gb/s 的FTLF8528P3 BCV 光纤收发器;而千兆网络通信使用FCLF8521P2 BTL 型号以太网SFP 模块,该模块使用RJ45 接口,通过寻常网线即可连接到其他网络设备上。

2.1.5 背板接口电路

主处理模块基于兼容性考虑,保留了MTCA 机箱平台的背板总线连接,以便实现更灵活的数据传输与处理功能。机箱背板共有20 个Port,每个Port 都有一收一发两对高速差分线,不同Port 可用于实现不同功能。主处理模块卡将12 个GTH 连到了Port0~11 上面,其中Port0、1 分别连接到两块交换卡上,可实现千兆网络通信;Port2、3 可用于相邻槽位插卡间的数据通信;Port4~7与Port8~11 分别与交换卡1、2 相连,可实现×4 链路的PCIe 或者SRIO 总线通信。

2.2 IO 扩展模块设计

IO 扩展模块电路结构如图7 所示,IO 扩展模块使用MPS 公司的MPM3630GQV-Z 型号DC-DC 直流降压芯片,将主处理模块通过硬公制连接器提供的12 V 电源转为3.3 V,供8 路SFP+模块使用;板上有8 路SFP+模块与2 路156.25 MHz 频率的本地晶振,通过硬公制连接器将相应信号送至主处理模块上的FPGA 以实现光纤链路数据通信。

图7 IO 扩展模块电路结构框图

3 硬件电路测试

为验证数字触发判选电路的实测性能是否符合设计时的指标,在实验室环境下对电路逻辑的数据传输与缓存接口进行相应测试。

3.1 高速串行数据传输测试

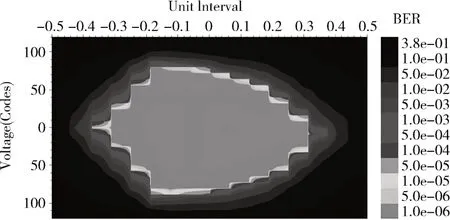

为验证高速串行数据传输的稳定性,对高速串行收发器进行误码率测试[15],在FPGA 逻辑里例化Xilinx 提供的专用于高速串行收发器误码率测试的IBERT IP 核,通过IBERT 工具得到误码率与眼图测试结果。测试时相邻两对收发器互相通过光纤传输数据,IBERT IP 核产生PRBS-7 伪随机码对传输链路进行测试,现场照片如图8 所示。经过约10 小时的测试得到如图9 所示的误码率测试结果,光纤链路传输了约3.79×1014bit 大小的数据量,通道误码数为0,在99%的置信度下小于2.645×10-15。其中一条链路眼图测试结果如图10 所示,眼图睁开范围较大,具有较好信号完整性。

图8 现场测试照片

图9 IBERT 测试误码率结果

图10 IBERT 测试眼图

3.2 SiTCP 上行网络通信测速

SiTCP 使用TCP 连接实现硬件电路与上位机之间的数据通信,硬件内逻辑持续通过SiTCP 上传数据。在上位机编写测速程序测试其上行网速,上位机作为客户端与数字触发判选电路建立TCP 连接,持续接收数字触发判选电路上传的数据,并对其上行网络数据通信速率进行测试。实测的网络通信速率如图11 所示,上行的平均网络通信速率最高可达949.3 Mb/s左右。

图11 SiTCP 上行网络传输测速

3.3 DDR4 数据读写测试

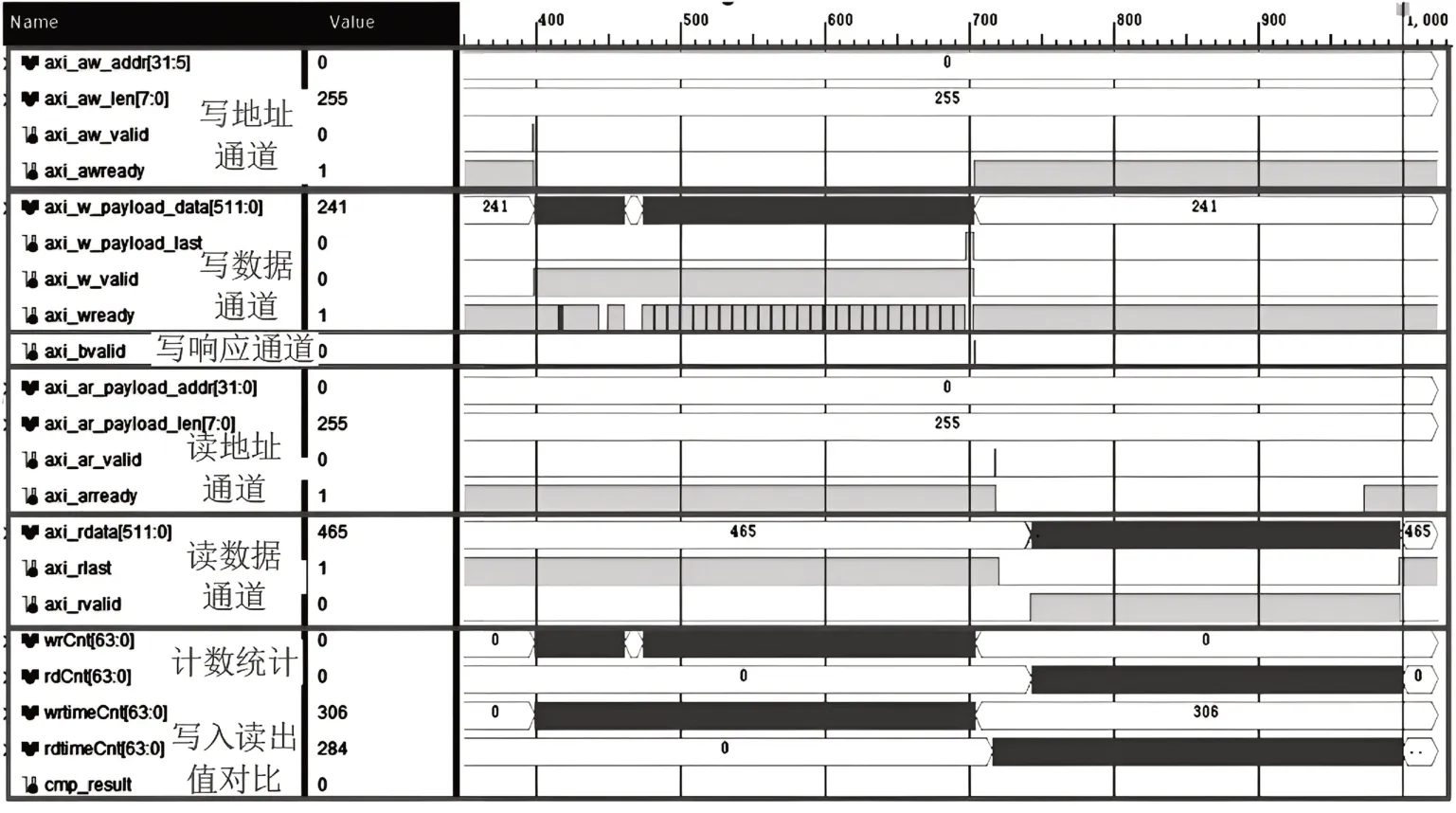

为验证DDR4 芯片的高速数据缓存是否能够正常工作,编写了数据缓存接口的测试逻辑,例化了Xilinx 提供的AXI4 总线接口的DDR4 MIG IP 核[16],DDR 传输速率设定为2 000 MT/s,理论传输带宽为128 Gb/s。测试逻辑持续产生数据递增码,并通过AXI4 接口依次向DDR 地址单元中写入数据,随后再读出数据检测是否符合预期,通过多次操作验证DDR 缓存接口功能正确性,并记录运行时间与写入读出的数据量进行读写测速。

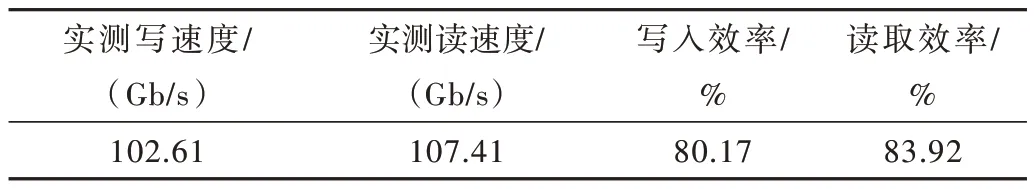

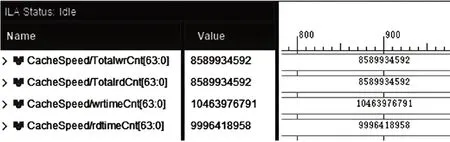

某次写入读出过程的逻辑波形如图12所示,写入读出功能正常,读出数据与写入数据完全一致。在经过128 次对DDR所有地址单元的写入读出循环操作后得到如图13所示的测速结果,共完成了4 096 Gb 数据量的DDR 数据读写操作,写入读出分别消耗了10 463 976 791、9 996 418 958 个时钟周期,在整个测试过程中写入与读出值完全一致,数据读写无误,DDR写入读出速度如表1所示。

表1 DDR4 实测写入与读出速度

图12 DDR4 读写测速波形

图13 DDR4 读写操作消耗时钟周期计数

4 结论

针对核与粒子物理实验中的数字NHit 触发判选需求,本文设计实现了一种高性能数字触发判选电路,可支持多通道的光纤数据传输与千兆网络通信、高速大容量数据存储以及实时FPGA 数字触发处理。在实验室条件下进行了数据传输与缓存接口测试,测试结果表明板卡可实现8.125 Gb/s 光纤链路的高速串行数据传输速率,SiTCP 上行网络传输速率达949.3 Mb/s,DDR 数据读写速率可达102.6 Gb/s,满足电路设计需求。该硬件电路具有较强的扩展性与灵活性,可通过多个该模块的扩展,灵活应用在各个物理实验中。本文在完成硬件电路的设计实现以及数据传输与缓存接口的性能测试工作基础上,后续将结合数字NHit 触发算法,完成数字触发判选电路的完整逻辑设计工作,并进行多个模块扩展的系统级别综合调试验证。