基于CMOS 阈值电压设计的电压基准源

徐晴昊,奚冬杰

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

电压基准源作为一个基础单元模块被广泛应用于诸如数据传输、随机存储器和射频电路等电子系统。高精度的电压基准源应具有与工艺无关的低温度和低电源电压敏感性,其输出电压精度将限制所在系统的性能上限,因此研究如何设计高精度电压基准源具有重要意义[1−4]。

传统电压基准源基于三极管带隙电压进行设计,采取一阶补偿方案,输出为三极管基极与发射极间压差(VBE)和热电压(VT)的加权和。由于VBE的展开式中存在温度的非线性高阶分量,因此传统电压基准源如需提升输出精度则需采取高阶曲率补偿方案。针对一阶补偿因固有缺陷所导致基准输出电压精度受限问题,业内提出了电阻温度系数补偿、亚阈值区MOS 补偿、指数型电流补偿和分段线性曲率补偿等高阶温度补偿方案,但综合考虑功耗、面积、噪声、模型精度、良率和工艺兼容性等问题上述方案应用场景受限[5−7]。

针对传统带隙结构基准所存在的问题,本文采用两个具有线性互补温度系数的电压项加权求和方案,提出了一种基于CMOS 阈值电压设计的电压基准源。其中基础线性正温度系数单元由与温度成正比的电压VPTAT实现,基础线性负温度系数单元由MOS 管阈值电压Vth实现,电路中所有MOS 管均工作于强反型区,可实现更高的仿真模型精度。采用具有PSRR 提高技术的自偏置电流源为无电阻Vth产生模块提供电流偏置,其通过减小电流镜像误差,可提升电压基准输出抗电源噪声干扰能力。考虑自偏置电流源中输出电流温度特性,利用一个非对称差分运放即可同时实现VPTAT的产生和VPTAT与Vth的加权求和。最终所设计电压基准源在2.5 V~5 V 电源电压下,以及-55 ℃~125 ℃温度范围内温度系数低至4.5 ppm/℃,由于未采用电阻且所有MOS 管均工作于强反型区,因此本文所提出基准电路具有更高的输出精度和更广的应用范围[8−10]。

1 电路补偿原理

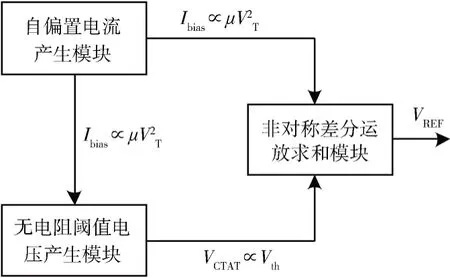

为避免VBE中高阶非线性温度分量影响电压基准输出精度,本文基于具有线性负温度系数的Vth设计了一种新型无电阻电压基准源,其系统架构如图1 所示。

图1 本文中电压基准源系统框图

图1 中具有PSRR 提高技术的自偏置电流产生模块为其他模块提供大小正比于µV2T 的偏置电流Ibias,其中µ为电子迁移率。将偏置电流Ibias施加于非对称差分运放求和模块,利用MOS 管工作于饱和区时其过驱动电压和输出电流的关系,可迫使运放两个输入端之间电压差(失调电压)与温度成正比,从而获得温度补偿时所需的线性正温电压VPTAT。用于基准输出补偿的线性负温电压VCTAT与Vth成正比,其通过本文所设计无电阻阈值电压产生模块获得。将VCTAT注入非对称差分运放正输入端,因运放正负端间压差为VPTAT且运放处于单位负反馈环路时运放输出端电压为正端电压与失调电压之和,则此时运放输出端电压即为所需电压基准。本文所设计电压基准中VPTAT的产生和其与VCTAT的加权求和均由非对称差分运放模块完成,且未采用高阶补偿方案,电路结构被大幅简化。

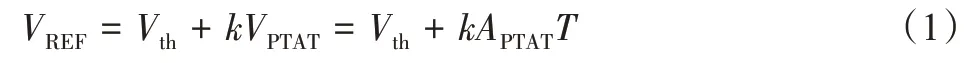

结合上述分析可知,最终基准电压表现为Vth与VPTAT的加权求和,具体表达式如式(1)所示:

其中k为一固定常数,与工艺参数无关,仅由电路中MOS 管尺寸比值决定。APTAT为固定正值,典型值为0.086 7 mV/℃,其代表VPTAT温度系数。

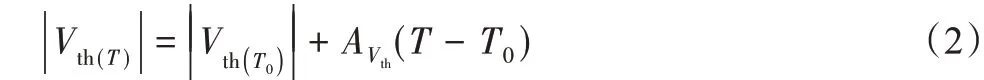

Vth详细表达式如式(2)所示:

其中T代表绝对温度;T0代表参考温度点;Vth(T0)代表在参考温度处MOS 管阈值电压大小;AVth为一固定负值,与具体选用工艺相关,其代表Vth温度系数。

结合式(1)、式(2)可知,Vth与VPTAT均具有线性温度系数,当取kAPTAT=-AVth时,即有∂VREF/∂T=0,此时电压基准输出中不包含非线性温度分量,具有近似零温特性,且常温下VREF值由所选用设计工艺中MOS 管Vth决定。

2 具体电路实现

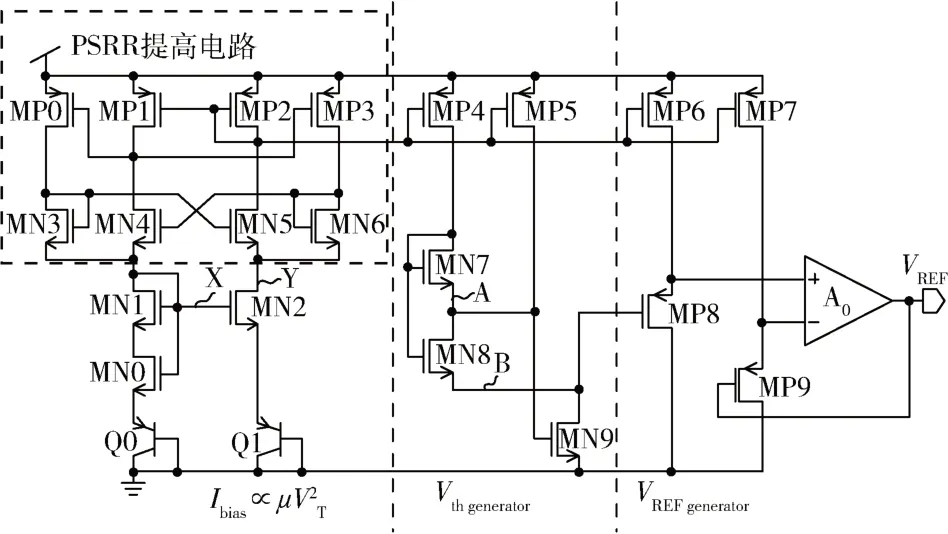

本文所提出基于CMOS 阈值电压设计的电压基准源具体电路实现如图2 所示。整体电路由自偏置电流产生模块(Ibias∝µV2T)、无电阻阈值电压产生模块和非对称差分运放求和模块共三部分组成。

图2 基于CMOS 阈值电压设计的电压基准源

2.1 自偏置电流产生模块(Ibias∝µV2T)

该模块为自偏置结构,MOS 管均工作于强反型区,具有较高的仿真模型精度,(W/L)MP0=(W/L)MP1=(W/L)MP2=(W/L)MP3。其中PSRR 提高电路具有电流镜箝位功能,可通过控制MP1 与MP2 漏端电压相等且VX=VY来确保电流镜镜像精度,以最终减小电源噪声对输出偏置电流的影响,整体负反馈环路增益为2gm(MP2)gm(MN5)(rdsMP2||rdsMN5)2。

假设电源存在扰动,使得VX≠VY。设VY相对于稳态时增大了+∆V,VX相对于稳态时减小了+∆V。由于(1/gMN6)≪ro(MP3),因此MN4管的栅极相对于稳态时增大了+∆V。此时,MN4 管的栅源电压VGS(MN4)相对于稳态时增大了+2∆V。VGS(MN4)上升,则MP1 漏端电压下降,MP0 管的输出电流增大,最终调整为VX=VY。

在VX=VY下,设置三极管Q0 与Q1 面积比为N且(W/L)MN1=(W/L)MN2,则对MN0 和MN1 存在如下关系:

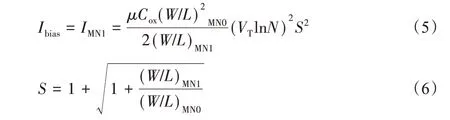

MN0 工作于三极管区,MN1 工作于饱和区,且两者电流相等。考虑MOS 管在相应工作区域电流表达式,则自偏置电流产生模块输出Ibias∝µV2T,表达式如(5)式所示:

其中Cox代表MOS 管单位面积栅氧化层电容,IMN1代表MN1 中电流。

2.2 无电阻阈值电压产生模块

无电阻阈值电压产生模块(Vthgenerator),用于产生具有线性负温系数的Vth,其中MN8 作为可调线性电阻工作于三级管区。调节MP4、MP5 电流镜像比例和MN7~MN9 尺寸,即可使得Vds(MN8)与MN9 过驱动电压VOV(MN9)相等,从而在MN9 漏端输出所需Vth。

电路中器件尺寸一种有效设置的方式为:(W/L)MP5=2(W/L)MP4,(W/L)MN9=3(W/L)MN8=3(W/L)MN7。此时MN7、MN9具有相同的过驱动电压,Vds(MN8)=VOV(MN9)且Vgs(MN8)=2Vgs(MN9)-Vth(MN9)。

2.3 非对称差分运放求和模块(VREF generator)

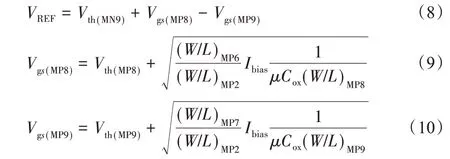

通过在运放A0 的输入端增加MP6~MP8 可构成非对称差分运放,该模块可实现将施加在MP8 栅端的Vth(MN9)(具有线性负温系数)与MP8 和MP9 间栅源压差(具有线性正温系数)的加权求和。

考虑闭环时运放两个输入端之间虚短的箝位特性,此时MP8 和MP9 源端电压相等。

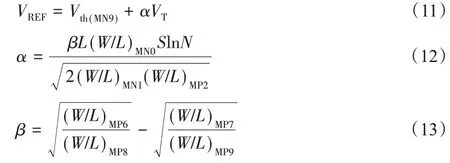

Vth(MP8)与Vth(MP9)相等,将式(9)、式(10)代入式(8)可知:

α与β为固定常数,与工艺参数无关,仅由电路中器件尺寸比决定。结合式(11)~(13)可知最终VREF仅由具有线性温度系数的分量构成,合理设置电路中器件尺寸以调整α大小,即可使得VREF具有近似零温特性,从而实现VREF高精度输出。

3 电路仿真结果和分析

采用TSMC 0.18 µm CMOS工艺,在电源电压2.5 V~5 V和温度-55 ℃~125 ℃范围内,对本文所设计基于CMOS 阈值电压设计的电压基准源进行了Specture 仿真验证。

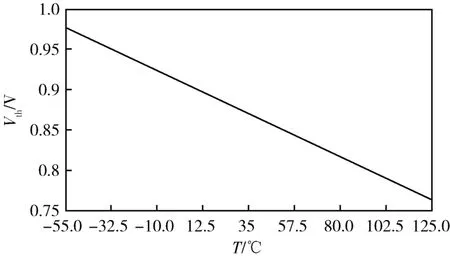

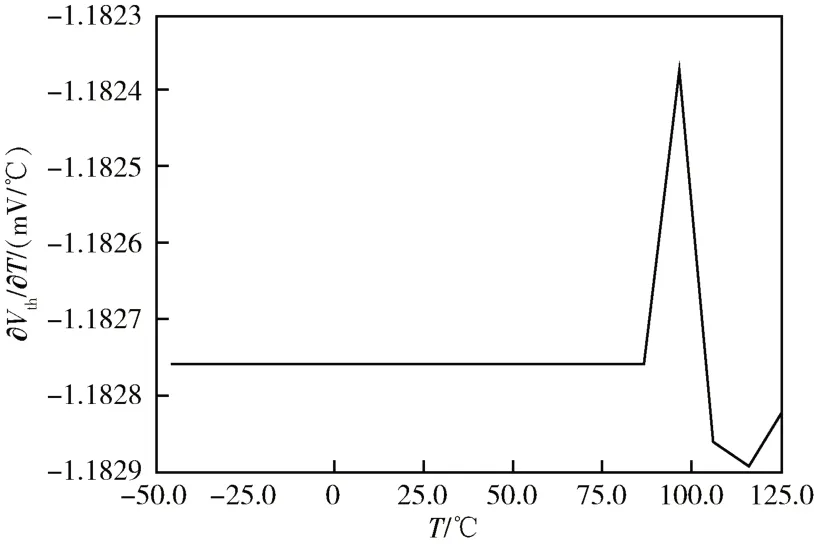

本文所选用设计工艺中Vth(MN9)温度系数为-1.182 7 mV/℃,仿真波形如图3、图4所示。VT温度系数为0.086 7 mV/℃,因此式(12)中选取α=13.64 作为仿真优化的初始迭代点。

图3 Vth(MN9)温度特性曲线

图4 Vth(MN9)温度系数曲线

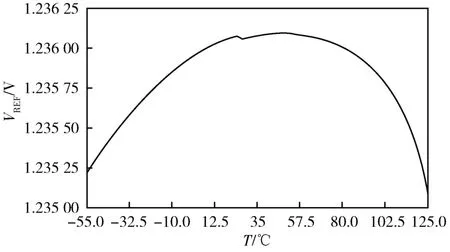

图5 所示VREF温度特性曲线仿真结果与理论分析一致,VREF的温度特性曲线呈现一阶补偿效果,典型值为1.235 7 V。在-55 ℃~125 ℃范围内,温度系数小于3.5 ppm/℃。

图5 VREF 温度特性曲线

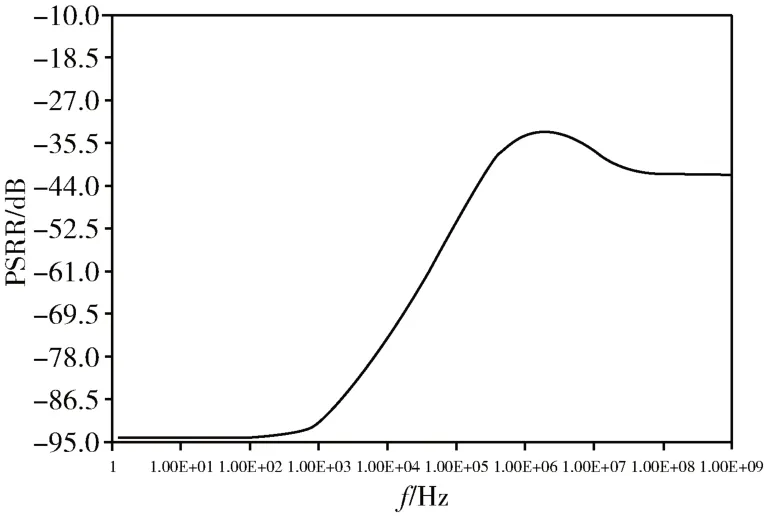

图6 所示为该VREF的PSRR 在电源电压5 V 下仿真结果。可以看出低频段PSRR 低于-93 dB,电路具有较强的抗电源噪声干扰能力。

图6 基准电路PSRR 曲线

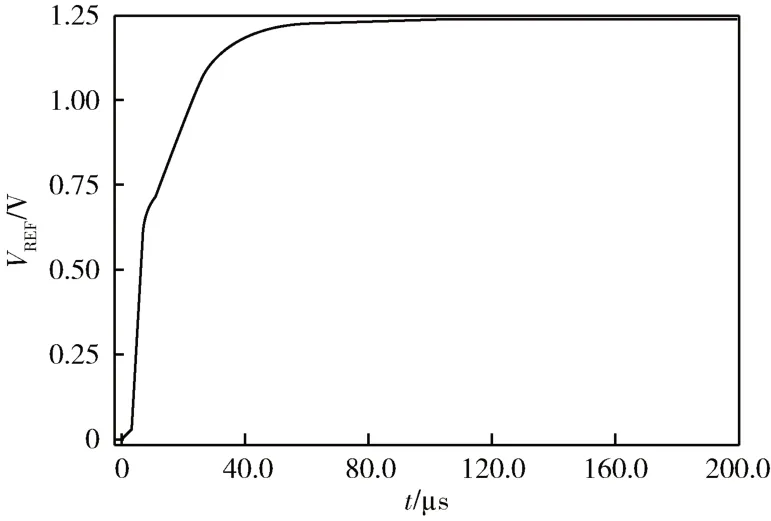

图7所示为VREF上电启动波形仿真。由图7可知当电源电压有效后VREF建立时间约为80 µs,且建立过程平稳不存在过冲。

图7 VREF 随电源电压变化曲线

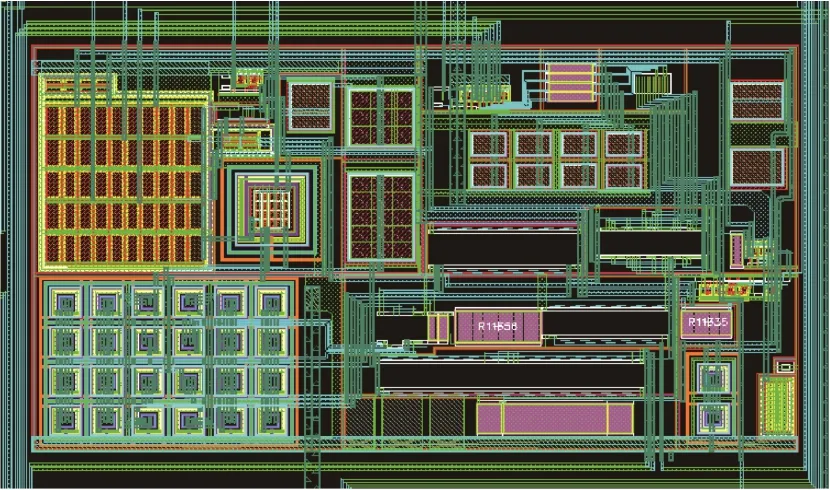

本文所提出基于CMOS 阈值电压设计的电压基准源已应用于一款汽车电子LDO 电路,图8 为该电压基准版图布局,模块面积为0.017 mm2。

图8 VREF 版图照片

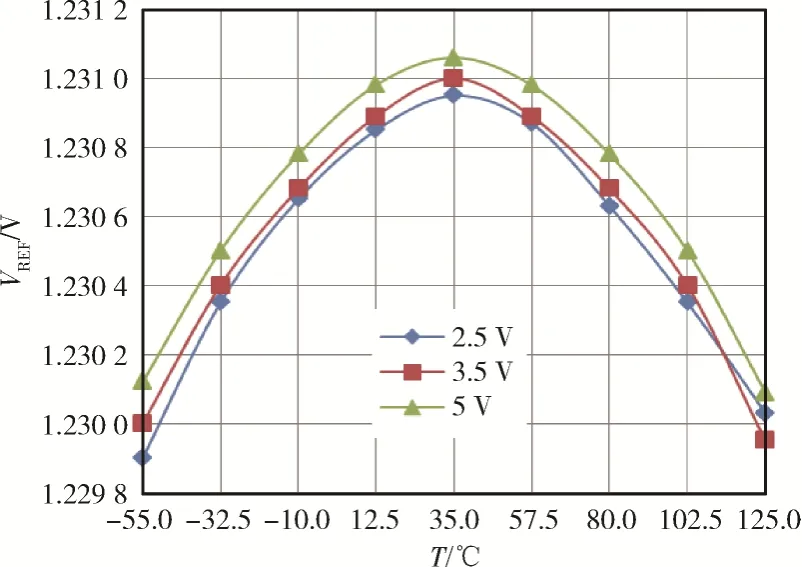

图9 为基准温漂在不同电源下实测结果,拟合曲线表明基准最大温漂为4.5 ppm/℃。测试结果与仿真值较为接近,偏差由器件匹配精度和版图寄生参数等引起。

图9 VREF 实测波形拟合

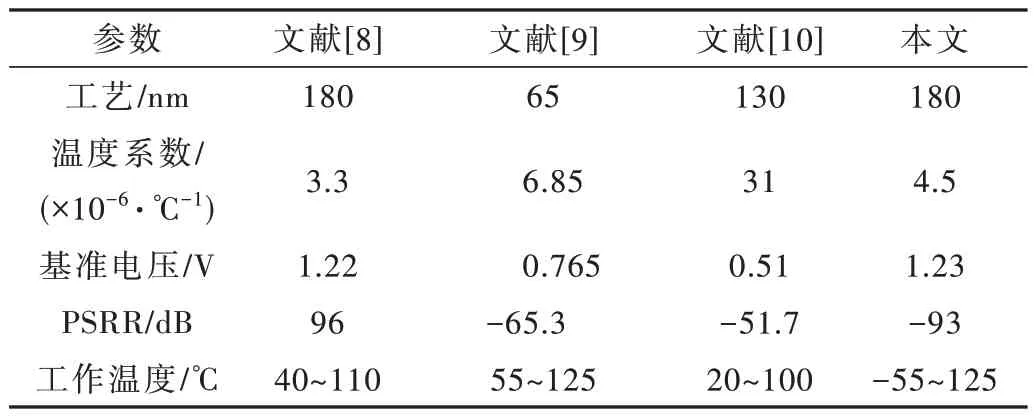

表1 为本文与其他文献中所提出CMOS 电压基准源的性能对比。除因未采用高阶补偿方案导致温度系数高于文献[8]外,相比于其他文献,本文所设计电压基准电路结构更为简单且在温度系数、电源抑制比和工作温度范围方面具有更优性能,适合于工况恶劣的汽车电子芯片应用。

表1 本文与其他文献中基准电压源的参数对比

4 结论

采用TSMC 0.18 µm CMOS 工艺提出了一种基于CMOS 阈值电压设计的电压基准源。在未采用高阶补偿情况下,通过基础线性互补温度单元Vth和VPTAT加权求和的方式即可获得高精度基准输出,具有PSRR 提高技术的自偏置电流源通过增强基准抗电源噪声干扰能力进一步提升其输出精度。Vth由无电阻结构产生,VPTAT的产生和与Vth的加权求和均由非对称差分运放完成,因此电路具有结构简单可与标准CMOS 工艺兼容等优点。验证结果表明该电压基准源在-55 ℃~125 ℃温度范围内,温度系数为4.5ppm/℃,低频电源抑制比为-93 dB,适用于要求具有宽工作温度范围的汽车电子芯片。