eFuse 失效分析与可靠性电路设计

晏 颖,曹玉升,张 睿

(1.上海飞聚微电子有限公司,上海 201316;2.浙江大学 微纳电子学院,浙江 杭州 310014)

0 引言

eFuse(Electrically Programmable Fuse)技术于2004年由IBM 公司首次发布,它基于电子迁移原理工作,即通过电流流过导体时产生的质量输运现象使得导体的电阻属性发生变化[1]。具体来说,eFuse 就是在其熔丝两端加上电压,在电流流过时发生电子迁移导致其电阻值增大或者产生焦耳热使其发生热断裂。eFuse 用作存储器时,数据存储是通过保持或改变熔丝的电阻值实现的,读出数据则是基于将熔丝的电阻值转换成电压值、再判别输出的过程。可见,熔丝电阻特性的变化以及电阻电压转换过程的稳定性直接影响eFuse 的可靠性。其中,熔丝电阻特性与工艺状态、材质属性、编程条件、电迁移过程等存在关联,影响因素很多。而电阻电压转换稳定性则和电路及版图设计、工作环境、工艺器件特性等有强相关性[2−4]。本研究基于系统及电路优化的策略,通过完善功能电路设计、增加针对性的控制模块和电路等来提高eFuse 可靠性。

1 失效模式

eFuse 可靠性降低的特征是其读出或存储的数据呈现不稳定或者出现失效状态,表现为eFuse 在特定条件下不能正常编程或者熔丝本身随机发生非期待的改变,以熔丝电阻值来衡量可分为两类现象,第一类是熔丝电阻值变大也就是熔丝被意外编程,比如,ESD 静电打坏熔丝,上电过程产生的耦合电流流过熔丝,控制功能失效等。第二类是熔丝阻值变小,即熔断后的熔丝存在短接或虚接等未完全断开现象,比如多晶硅熔丝发生过烧现象后(熔断区域过大,位置偏离熔断区等)容易出现金属硅化物层没有完全熔断使得熔丝电阻值不稳定。其中,第二类失效现象和熔丝材质及特性、尺寸和工作条件等有直接关系,主要从工艺或器件物理特性、编程环境等方面的优化加以改进。本研究专注于通过优化电路设计来抑制熔丝被意外编程导致电阻值变大的失效现象发生,从而提高eFuse 可靠性。

总体上,影响eFuse 可靠性包含人为、系统和器件的三方面因素,具体失效模式可归纳为三类:电路与版图设计、系统工况和器件特性,如图1 所示。

第一类失效归纳为电路设计原因(包括版图设计)。其现象为由于功能模块工作或电路设计原因,导致正常熔丝不能编程、被误编程或熔丝状态被误读,eFuse 呈现失效位增多或有规律分布。针对这类原因引起的可靠性问题,可以从优化电路设计和器件参数设置入手,使得eFuse 功能模块在各种条件及工艺角下都正常工作;在版图设计时,通过优化布局和线形、线宽等手段,避免由于电压压降等问题给eFuse 可靠性带来影响。

第二类失效是属于系统工况原因,其特点是熔丝在非正常工作状态下发生意外变化。通过分析发现很多eFuse 失效现象和系统状态相关,比如上电过程或者与编程电源的工作状态等。因为熔丝电阻特性变化主要是由其上的电流引起的,很多与编程电压的状态相关,特别是在系统启动过程中编程电压上电速度过快,其在eFuse 内部的感应电压使得熔丝出现意外电流或eFuse控制逻辑失效。

第三类失效模式与器件特性有关。eFuse 编程是熔丝发生电迁移或熔断等物理现象的过程,由于编程所需电流较大(金属熔丝熔断电流可达几十毫安),编程电源控制管的尺寸相应较大。当eFuse 编程开启电源控制管对被选中的位线充电时,后者会瞬间出现浪涌电流(Surge Current),这是由于编程电压要对位线及其连接的所有eFuse 单元的对地寄生电容进行充电,形成的大电流流过电源控制管。如果开启次数频繁,电流的累积冲击(热载流子效应)容易对器件造成损伤[5],最终影响整个系统的可靠性。

2 失效机理分析

在eFuse 的失效模式中,电路设计原因导致的失效属于人为因素,但源自系统和器件的失效因素在实际使用中是难以避免的,除了从工艺器件和工作环境等方面进行完善外,也可以通过增加人为因素(即优化电路设计和控制方案等)进行干预,对它们给eFuse 可靠性带来的影响进行抑制或消除。下面对系统和器件方面的失效原因进行初步归纳,相关电路优化设计也围绕这些问题的解决展开。

2.1 电源上电过快

芯片内部的互连线之间存在寄生电容(又称互容),电容大小与线间距、形状以及位置、隔离层介电常数等相关。eFuse 编程电源的金属线和控制信号线之间存在交错或平行等现象,这些线间寄生电容对可靠性的影响须在电路、版图设计和制定应用规则时加以考虑或规避。比如,编程电压从上电到稳定过程中的上电速度(Slew rate 或Transition time)须控制在一定范围内,即dv/dt不能太大[6]。因为从频域分析,编程电压上升过程经过傅里叶变换呈现为一个固定频率的脉冲信号。上电速度越快则对应的频率越高。由于电容的通高频阻低频特性,快速上升的编程电压通过线间寄生电容在信号线上感应出电压变化。如图2 所示,编程电压(VDDQ)所在金属线处于Mx 层,信号线(Signal)金属线处在My 层,Cxy为线间寄生电容,VDDQ 的上升过程通过电容Cxy在信号线上产生一个电压脉冲。

图2 不同层线间的寄生电容及产生感应电压现象

图3 描述了电源上电在eFuse 内部产生的感应现象。编程电压(VDDQ)在上电过程中不仅通过金属线间电容C2 在熔丝端(A 点)产生感应电压,还通过寄生电容C1 在字线(WL)上感应出电压,后者会导致eFuse 单元编程控制管MN 开启,使得A点感应电压在熔丝上产生对地电流,eFuse 单元被意外编程。

图3 上电过程感应现象

2.2 电源上电顺序

由于熔丝熔断电流较大,eFuse 编程通常需要较高工作电压。因此eFuse 多采用双电源(电压)体系:工作电压(VDD)和编程电压(VDDQ)。系统逻辑和控制部分采用VDD,而与编程相关的模块和电路则工作在VDDQ 域下。从可靠性上考虑,双电源系统一般要求固定的上下电顺序[7],即VDD 先上电到稳定后,VDDQ 再开始上电或者在eFuse 控制逻辑信号电位稳定后,编程电源再开始上电。而下电过程则相反,VDDQ 先下电,再VDD 下电。设置上电顺序是为了防止在系统未上电或没到达指定电平时,eFuse 出现逻辑混乱或不定状态。

但在实际应用中,eFuse 可能会面临编程电压早于工作电压上电或者两者上电间隔非常接近的状况。一旦eFuse 的内部控制逻辑处于非正常状态,其熔丝发生意外熔断几率大大增加。如图4 所示,当VDDQ 上电时,VDD 仍处于未上电的低电平。在两者上电间隔时间t以内,正确WL 信号还没有建立,反相器输出端(C点)会处于浮空状态,使得eFuse 单元编程管MN 可能被意外打开,存在熔丝到地出现感应电流导致熔丝电阻增大甚至eFuse 单元被意外编程的风险。

图4 eFuse 电源电压上电顺序的影响

2.3 浪涌电流冲击

eFuse 编程电流是由熔丝的熔断电流决定的,金属熔丝要比多晶硅熔丝更大,前者超过30 mA,后者小于10 mA。为了保证足够电流通过熔丝,eFuse 单元的编程控制管都采用很大宽长比。在eFuse 单元阵列中每条位线(BL)的编程电源控制管采用更大尺寸,而且位线采用较大的线宽以减少电压降,因此位线上存在较大的等效负载电容。eFuse 在编程模式下,其编程电源VDDQ通过电源控制管对被选定的位线进行充电,如图5所示。

图5 位线充电瞬间出现的浪涌电流

在图5 中,当电源控制管P1 在开启瞬间有很大的浪涌电流流过,这是由于VDDQ 要对BL 上所有eFuse 单元的寄生电容以及位线本身负载电容进行充电,充电电流汇积形成大电流脉冲(百毫安级)。位于同一位线上eFuse 单元越多,编程模式下充电开启次数也越多,电流不断冲击易对器件造成损伤,降低系统可靠性。

2.4 控制时序失配

eFuse 读取模块把熔丝电阻值转换为逻辑数据,输出模块用于保持和输出逻辑数据。这两个模块都受到读操作启动信号控制,如图6 所示。图中的启动信号(Strobe)控制两个模块,当Strobe 为高电平时,读取模块处于转化阶段,输出模块为采样阶段;信号为低电平时,读取模块为准备阶段,输出模块则处于保持阶段。Strobe 到读取模块和输出模块的延时时间分别为t1和t2,读取模块的输出信号到输出模块输入端的时间为td,即模块之间信号的延时时间。

图6 读取电路和输出电路的启动控制及延时

在实际工作中有两种控制时序失配会导致eFuse 读出数据不可靠。第一种情形是,如果td较大,而启动信号到输出模块的时间t2较到读取电路的时间t1更小,输出模块可能在读取模块转化阶段结束前就进入保持阶段,使得读取模块的信号转化(td延时前)还没有产生正确结果,输出模块已经将非最终正确值保持住并输出。第二种情形是,如果td较小,而启动信号到输出模块的时间t2较到读取模块的时间t1更大,输出模块可能在读取电路转化结束并且进入下一轮数据准备(采样)阶段后才进入到保持阶段,其结果是将读取模块在新一轮的非最终结果保持住并作为输出。显然,这两类失配导致的失效都和时序控制相关。

3 可靠性电路设计

3.1 隔离编程电源

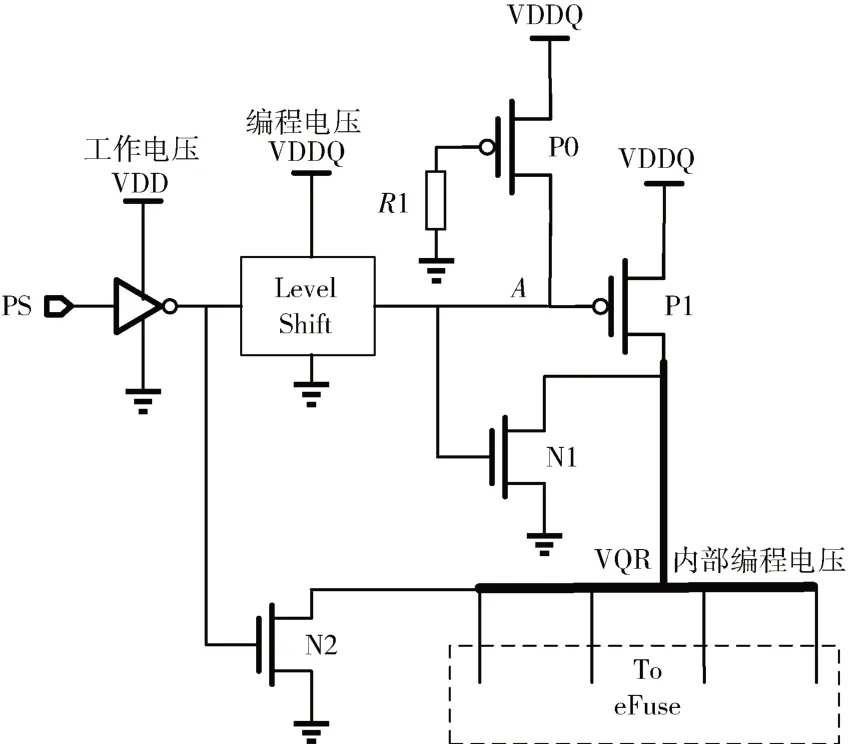

基于失效机理分析,编程电压早于工作电压上电是要避免的。基本思路是对编程电压进入eFuse 内部进行控制,消除其上电过程对于内部电路的影响。图7 所示方案是设置一路专门电源切换信号(Power Switch,PS)并增加控制电路。它将编程电源VDDQ 和eFuse 内部进行隔断,并通过逻辑控制VDDQ 进入eFuse 内部,确保后者不会出现编程电压比工作电压更早上电的情况。具体做法是:在VDD 上电完成且VDDQ 处于上电过程时,PS 置低电平,关断控制管以阻断VDDQ 进入eFuse 内部;如果VDD 还未上电或未稳定,PS 不起作用,VDDQ已经开始上电,则通过上拉管关断控制管,阻断前者进入eFuse 内部;在编程时,PS 置高电平,控制管打开,VDDQ 进入系统内部。

图7 eFuse 编程电源的隔断控制电路

图7 电路中虚框表示eFuse 内部电路。隔断控制电路由反相器、电平转换(Level Shift,LS)模块、下拉电阻R1、PMOS 上拉管P0、PMOS 电源控制管P1、NMOS 放电管N1 和N2 组成。P1 管将VDDQ 和eFuse 内部编程电源(VQR)隔开。N1 管在VDDQ 存在时对VQR 放电,N2 管在VDDQ 为悬空状态时对VQR 放电。输入信号PS 为VDD 域,PS 通过电平转换模块LS 转换到编程电压域VDDQ,并控制P1 管开启或关闭,连通或阻断VDDQ 和VQR 之间的通路;上拉P0 管和接地电阻R1 配合使得在VDDQ 上电而VDD 未上电时,保证P1 管处于关断状态,阻断VDDQ 进入eFuse 内部,即VQR 浮空。

3.2 阻断电流通路

针对编程电源可能存在的上电速度过快现象,一种电路解决方案是在编程电源上电过程中将eFuse 单元和地进行隔断,使得熔丝和地之间没有电流通路。具体办法是把eFuse 接地(VSS)分成内部地(VSSI)和外部地(VSS)两个系统。当编程电源上电时,VSSI 和VSS 之间是隔断状态,保证eFuse 单元不会出现经过熔丝到VSS的通路,即没有电流通过熔丝。而当编程电压进入稳定状态后,VSS 和VSSI 导通,使得eFuse 进行编程和读取操作时,从电源经过熔丝到VSS 的通路正常。

图8 所示电路在eFuse 对地通路上(BL to VSS)增加NMOS 管N0,隔开eFuse 单元和地VSS 的直接连接,其栅端接控制电路。后者在编程电压VDDQ 快速上电时,通过控制N0 管来隔断eFuse 单元对地通路。而在正常工作时,VDDQ 完成上电过程并处于稳定状态,N0 管导通使得VSSI 与VSS 同电位。

图8 在上电过程中隔断熔丝编程通路的电路

由于P0 管的接法使其等效于MOS 电容,当VDDQ电压快速上升时,处于电容一端的N1 管栅端(B点)电压也上升,N1 管被打开,A点电压下降导致N0 管关断,阻断VSSI 和外部地VSS 之间的连接,也就防止熔丝出现电流。当VDDQ 处于稳定状态后,作为电容的P0 管隔断VDDQ 与B 点连接,下拉电阻R1 将B点电位被拉到0 电平,N1 管被关闭,A点对地通路断开。采用二极管接法的N2 管将P1 管栅端拉到低电平,P1 管导通,A点电位上升使得N0 管导通,eFuse 内部地VSSI 和外部地VSS 同电位,允许熔丝电流通过到地。总之,在VDDQ上电时,VSSI 和外部地VSS 断开,而在正常工作时,VSSI 连接外部地VSS。

3.3 关断编程控制管

不仅在编程电源上电阶段,eFuse 即使在工作阶段,当编程电源线上出现电压波动甚至静电放电现象(ESD)时,也可能引发熔丝电阻变化或意外熔断。ESD是一种快速的大电压变化过程。由于金属线之间存在寄生电容,ESD 感应出的耦合电压会出现在熔丝一端。如果eFuse 单元的编程控制管不能阻断熔丝对地的通路,熔丝上可能出现感应电流。显然,从可靠性角度,可以通过优化电路结构或控制逻辑使得eFuse 编程控制管在编程电源出现电压波动或ESD 等工况时保持断开状态。一种解决方案是增加专门的控制逻辑和电路,它既在正常操作下不影响编程控制管的工作状态,又能在编程电压波动或发生ESD 时关闭编程控制管,阻断熔丝到地之间电流,如图9 所示。

图9 编程管状态控制逻辑及电路

图9 中的控制电路在VDDQ 发生电压波动或出现ESD 现象时,突变电压导致采用电容接法的P1 管导通,B 点电压上升,下拉管N1 导通,字线WL 电位被拉到地电平,MN 管断开,熔丝不会有电流通过。当eFuse 正常工作时,VDDQ 稳定,由P1 管构成的MOS 电容隔断VDDQ 和B 点。下拉电阻R1 将B 点拉到地电平VSS,N1 断开,WL 信号对MN 管的控制不受影响。

3.4 抑制浪涌电流

2.3节提到eFuse 在编程时会出现大的浪涌电流。为了减小浪涌电流对位线BL 上所连接器件的冲击,一种电路改进方案是采用分步方式开启被选中的位线上电源控制管以减小浪涌电流的幅值,并且将没有选中的位线接地,使得其连接的eFuse 单元无电流。在图10 所示的具体电路中,BLC 为列选择信号,Prog 为编程控制信号。处于并联状态的PMOS 管P1 和NMOS 管N1 用来共同开启电源控制管,但P1 管尺寸远大于N1 管,大部分电流通过P1 管。而PMOS 管P0 和NMOS 管N0 用来确保P1 管状态以及将位线电压下拉到地。电平转换模块(LS)将VDD 域信号提升到VDDQ 电平,其输出Q 和QB 为反相信号。

图10 减小浪涌电流冲击的控制电路示意图

图10 中电路处于编程模式时,Prog 为高电平,BLC为高电平,经过反相器和LS 的Q 端输出低电平将P1 管打开,而QB 端输出高电平并打开N1 管。QB 信号被设计成略快于Q 信号,N1 管先开启对位线寄生电容充电,它的尺寸远小于P1 管,极大限制了浪涌电流。当P1 管紧接着后开启时,由于位线BL 电压已经升高,P1 管源漏端电压差已经减小,使得P1 管上浪涌电流下降很多。由于Prog 为高电平,BLC 反相为低电平,两者与逻辑操作后使得下拉管N0 断开。在BLC 为低电平时,和上述结果相反,P1 管和N1 管都断开,VDDQ 和位线BL 隔断,下拉管N0 导通,位线BL 拉到地电平。当eFuse 处于读模式时,读电流从位线经过被选择单元的熔丝到地,为防止位线的电平状态影响读电流,BLC 设置为低电平断开P1 和N1 管;Prog 信号为低电平,和BLC 的反相进行与逻辑后,输出低电平断开下拉管N0,这样位线处于高阻态,不影响读电流。

3.5 优化控制时序

控制时序失配会导致eFuse 输出失效或者不稳定信息,因此,对eFuse 读取和输出模块的控制顺序进行优化是必须的。根据图6 所示的模块及信号控制流程,优化思路是在采样周期、模块的控制延时以及传输信号延时之间都保证足够的时间裕度。图11 提出了一种控制信号优化电路,输入信号Strobe 为启动信号,RD 为读使能。两信号进行与操作后(与非和非)产生RDST 控制电路信号。

图11 读取和输出时序控制电路

图11 中控制电路包含上下两条支路以及相互之间的反馈控制。由或非门nor2 和反相器inv1~4 构成上支路,由与非门nand2 和反相器inv5~8 构成下支路。上支路输出信号SAE 和SAB 负责读取模块控制,而下支路输出DOE 和DOB 控制输出模块,反相器组合(inv2/3 和inv6/7)调整上下支路各自的延时时间。该控制电路在读取电路开始比较和转换放大后,输出模块进入输出采样状态;读取模块进行转换(电阻值转化成逻辑值),在其工作状态结束前,输出模块从采样阶段进入输出保持状态。

图12 所示的是控制电路工作波形和信号时序。其中,启动信号RDST 由输入信号RD 和Strobe 的与逻辑产生。它与SAE 以及SAE 与DOE 之间的上下沿时间差由时序电路中支路的延时时间决定。在读模式(RD=1)下,读取操作未启动时(Strobe=0),SAE=0 和DOE=0。当读操作启动后(Strobe=1),启动信号RDST=1,在SAE为高电平且延时t1后DOE 变高电平,即输出模块在读模块工作(比较放大阶段)延时Tsd后工作(进入采样阶段),并在SAE 变为低电平(下一个信号采样阶段)提前Tds就对输出值进行保持,防止采到下一个数据。可以看出,图11 中的控制信号的反馈关系使得输出模块状态可以决定读取模块状态,而后者也会影响前者工作状态,具体说,读取模块先动后停,而输出模块是后动先停,以保证输出数据的正确性。

图12 读取和输出时序控制信号波形

4 结论

高可靠性是eFuse 系统和电路优化设计的核心目标。由于eFuse 通过熔断熔丝使其电阻特性改变来实现编程操作,通过熔丝电阻值转换为对应逻辑值来实现数据存储和输出的功能。因此,熔丝电阻特性变化以及电阻电压转换过程中出现任何的干扰因素都直接影响eFuse 可靠性。本研究在分析失效模式的基础上,聚焦于系统和优化电路设计,通过增加专门电路模块和控制逻辑等方式消除外部因素对eFuse 可靠性的影响,针对导致熔丝电阻特性变化的主要机理,设计了相应电路和控制优化方案以防止它们降低可靠性。不过,这些方案也带来诸如逻辑复杂、功耗增加等问题,在实际应用时需要平衡考虑。