可扩展式微处理器总剂量效应在线测试系统研制

陈法国 于伟跃 梁润成 郑智睿 郭 荣

1(中国辐射防护研究院 太原 030006)

2(核药研发转化及精准防护山西省重点实验室 太原 030006)

在智能化发展的大背景下,应用于核工业领域的智能设备在辐射环境条件下的可靠性备受关注;除了核事故应急、反应堆堆芯内部等极端情况,核工业领域的大量电子设备主要工作在Gy·h-1量级以下的中低剂量率γ辐射环境中,通常只需要考虑总剂量效应的影响。综合考虑抗辐射加固器件和商用现货器件(Commercial Off-the-Shelf,COTS)的耐辐射性能、功能丰富性、成本、供货周期等因素,在深入研究COTS器件总剂量效应失效规律和表征方法的基础上,通过COTS器件的耐辐射筛选、受照剂量管理以及定量或定期更换,是优化其应用可靠性的一种可行方式[1-2]。

为了在辐照条件下原位测试器件的总剂量效应,目前针对存储器[3-5]、数字信号处理器[6]、图像传感器[7-8]等功能特定或规模适中的集成芯片[9-11],开发了多种专用在线测试系统。但对于功能丰富、内部结构复杂的大规模微处理器,随着集成电路特征尺寸向深亚微米和纳米级发展[12],微处理器总剂量效应的机理以及宏观功能表现都有新的变化,现有测试方法和测试系统的适用性和通用性都值得关注[13-15]:首先,微处理器由片内存储器、内核、通信、时钟、通用输入/输出接口(Input/Output port,I/O)等多种内置模块组成,其功能失效模式研究需要实时测试各内置模块的运行状态;其次,微处理器失效可能表现为功耗电流等宏观电参数退化、功能失效或者耦合失效,参数退化与功能失效的内在联系研究需要同时获取参数信息与功能状态;最后,耐辐射测试筛选涉及不同厂家、不同系列的微处理器,并且可能需要同时测试多个微处理器以评估其耐辐射性能在批次间、批次内的分散性,也对测试系统的通用性提出了一定的要求。为此,针对微处理器的总剂量效应研究及测试筛选需要,研制了一种可扩展式的在线测试系统,并初步应用于40 nm微处理器的失效模式研究。

1 微处理总剂量失效模式及测试方法分析

1.1 总剂量失效模式

微处理器是由众多晶体管构成的硅半导体器件;电离辐射在其内部沉积能量产生的电子-空穴对,会发生复合、输运、俘获等一系列物理过程,最终造成电学性能参数以及器件功能的瞬态或永久性变化,从而表现为单粒子效应、瞬态剂量率效应、总剂量效应三类辐照效应。

作为核工业领域主要关注的总剂量效应,在晶体管层级主要是器件氧化层内部形成的固定陷阱电荷和Si-SiO2界面态陷阱所造成的,表现为阈值电压漂移、漏电流增大等电学性能参数退化。晶体管的总剂量效应主要取决于器件工艺,随着以互补式金属氧化物半导体工艺(Complementary Metal-Oxide-Semiconductor,CMOS)为代表的集成电路的特征尺寸从微米量级缩小到纳米量级,栅氧化物中沉积陷阱电荷的能力大大降低、阈值电压漂移随之大幅减弱,使得影响总剂量效应的关键损伤部位从栅氧化层变成场氧化层;理论上,随着工艺特征尺寸的减小,器件耐总剂量效应的本征能力随之上升[15]。此外,晶体管总剂量效应还与偏置电压、负载等工作状态以及剂量率、温度、退火等辐照条件有关。

在芯片层级,功能丰富的内部结构决定了微处理器总剂量失效模式的复杂性,可能是模拟量超出额定范围的参数退化,也可能是逻辑电平、时序等数字电路节点变化而造成的功能失效,并且参数退化与功能失效之间是相互关联的。Boychenko等[14]基于大量的实验研究统计发现,简单逻辑单元的总剂量效应主要表现为参数退化,微处理器则兼有参数退化和功能失效,且以功能失效居多;Guertin等[16]在实验中观察到了微处理器的发光二极管(Light-Emitting Diode,LED)控制失效、Flash位错误、堆栈溢出、非受控启动编译、寄存器不可读、程序无法运行等多种功能失效模式。与此同时,微处理器内置模块的辐射敏感性也各有差异,也会在芯片层级表现出不同的失效剂量,不仅与各模块的本征特性有关,还受到偏置条件和工作状态的影响。

1.2 测试方法分析

针对单个晶体管或小规模集成电路,已经有总剂量效应测试的标准方法[17]。对单个晶体管,可以测量其电流-电压(I-V)输出或转移特性曲线,从而详细分析阈值电压漂移、漏电流变化等敏感参数;对小规模集成芯片,可以通过相对简单的测试电路并结合仿真技术,确定芯片的失效模式和失效剂量分布[15]。

由于微处理器功能丰富、内部结构复杂,并且总剂量效应与工作状态、辐照条件有关,通常需要在线原位进行参数和功能测试,但是在具体的测试实现方式和失效模式分析方面,还存在一定的挑战。功耗电流、输出电压等参数测试相对容易,但有限的外部引脚不能全面反映内部结构电学参数的变化,并且参数退化难以直接归因到具体的失效模块。功能测试理论上可以通过微处理器循环运行预载程序来校验所有的预期功能,但需要考虑功能校验方式的代表性和特异性:一方面,内置模块的辐射敏感性存在差异,并且存在多个内置模块共同实现单个功能或者单个模块参与多个功能实现的情况;另一方面,大部分功能失效通常表现为一个突变过程,并且会导致测试系统无法获取预载程序运行状态,在此过程中能够获取的信息比较有限。除此之外,还需要考虑辐照实验中对测试系统远距离控制、屏蔽防护、批量测试等方面的需求。

2 在线测试系统的设计调试

2.1 系统组成

综合考虑测试需要以及相关经验反馈,微处理器总剂量效应测试条件的设计可以参考以下信息或原则[13-14,18]:辐照中在线原位测试且实时上传数据;参数测量与功能校验相结合;功能失效通常会伴随功耗电流的变化、甚至是突变;微处理器内核、片内存储单元通常是最敏感的片内模块;功能校验方式全面且具有互异性,以便归因到失效的片内模块;测试接口尽量考虑不同类型微处理器的兼容性以及批量测试的可扩展性。

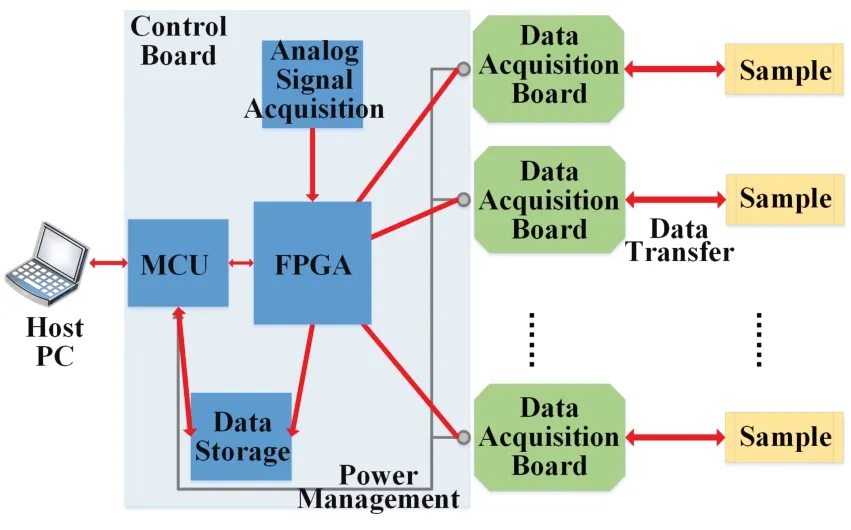

根据微处理器总剂量效应研究及测试筛选需要,研制了一种基于多通道数模信号采集的可扩展式在线测试系统,主要由主控制电路、信号采集电路、被测样品与接口电路、上位机及配套软件组成,其结构和实物分别如图1、2所示。

图1 在线测试系统的示意图Fig.1 Diagram of on-line testing system

被测样品电路除被测微处理器外,只有必要的电容、电阻等分立器件,以避免其他集成芯片对测试结果的影响;在电路板设计上兼容常见微处理器的封装结构,并通过模块化接口和屏蔽电缆与信号采集电路相连,方便更换被测样品。信号采集电路主要由微处理器、被测样品供电及功耗电流测量单元组成,利用微处理器与被测样品进行模拟、数字信号交互,将样品的参数及功能状态信息整合为校验数据包上传至主控制电路;综合考虑处理能力与可扩展性,每个测试通道配置独立的信号采集电路,由主控制电路对多路采集信号进行综合管理,以简化并行采集控制的逻辑复杂度。主控制电路主要由现场可编程门阵列(Field-Programmable Gate Array,FPGA)、微处理器(Microcontroller Unit,MCU)、存储器、模拟采集单元组成,分别实现采集电路校验数据包汇集处理、上位机数据交互、数据就地存储、测试环境条件测量等功能。上位机与主控制电路之间采用适合长距离传输的485模式进行数据交互。

图2 在线测试系统的实物图Fig.2 Practical photo of on-line test system

基于上述设计,可扩展式在线测试系统可兼容当前市场中多种硬件封装、通信方式和特征尺寸的微处理器总剂量。硬件封装兼容性方面,被测样品为可插拔设计,支持小外形封装(Small-Outline Package,SOP)、迷 你 小 外 形 封 装(Mini Small Outline Package,MSOP)、四方扁平式封装(Quad Flat Package,QFP)、无引线四方扁平封装(Quad-Flat No-leads Package,QFN)、球栅阵列封装(Ball Grid Array,BGA)等多种封装形式芯片的载样。通信兼容性方面,测试系统支持通用异步收发传输(Universal Asynchronous Receiver/Transmitter,UART)、集成电路 总 线(Inter-Integrated Circuit,I2C)、串行外设接口(Serial Peripheral Interface,SPI)、安全数字输入输出接口(Secure Digital Input Output,SDIO)、通用串行总线(Universal Serial Bus,USB)、低电压差分信号(Low-Voltage Differential Signaling,LVDS)等主流通信方式,并可以实现最大16通道的多类型器件实时同步测试。特征尺寸兼容性方面,工艺制程的进步主要丰富了微处理器的外设组成和数量,在线测试系统各采集通道配备独立的控制芯片,其片内存储容量为2 MB,足以存储被测样品返回的多帧数据以及复杂的校验算法程序;控制芯片具有168个I/O接口、35个通信外设、11个模拟外设,硬件资源基本满足市场中不同特征尺寸微处理器的硬件功能校验需求。

与此同时,基于在线测试系统丰富的硬件配置,其校验功能的可扩展性和测试样品种类的可扩展性也得到了保障。校验功能层面,首先,采集电路尚有部分硬件资源未被调用,后续可开发诸如I/O驱动能力、I/O开关特性、图像解码/编码能力、循环运算能力等新的校验功能;其次,也可以进一步升级原有校验功能,例如替换存储功能校验的测试图形(Testing Pattern)、或者改变被测样品预载程序的运行主频等;此外,采集电路主控芯片的主频为400 MHz,算力达2.14 DMIPS·MHz-1,在总剂量效应测试中可实现最大20 Hz的通信频率,该通信频率可复现微处理器在采集、传感、控制等应用中的实际运行状态,可获取不同工况下各功能及硬件单元的辐照损伤情况。测试样品种类方面,除微处理器外,测试系统可实现片上系统(System-on-a-Chip,SoC)、可编程片上系统(Programmable System-on-a-Chip,PSoC),复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)和FPGA等大多数主动器件,以及只读存储器(Read-Only Memory,ROM)、随机存取存储器(Random Access Memory,RAM)、闪存(Flash memory,Flash)、接口芯片和模拟芯片等被动器件的总剂量效应测试。

2.2 设计调试

测试系统的基本运行流程为:上位机发送测试启动指令,主控制电路、信号采集电路、被测样品功耗电流依次自检正常后,被测样品开始循环运行预载功能校验程序并与信号采集电路进行信息交互;信号采集电路则按照一定的编码方式,定时将采集到的样品参数和功能状态信息整合为校验数据包;所有样品的校验数据包经主控电路汇集后上传,由上位机进行解码和分析处理。

针对微处理器的片内存储器、通信、直接存储器访问(Direct Memory Access,DMA)、模数转换或数模转换(Analog-to-Digital Converter/Digital-to-Analog Converter,ADC/DAC)、时钟、输入/输出等主要片内模块或功能,设计了参数或功能校验实现方式,如表1所示。其中,功耗电流和时钟信号的校验不需要微处理器内核直接参与,有助于在微处理器功能失效时获取更多状态信息。

表1 微处理器典型参数或功能校验实现方式Table 1 Method for typical parametric or functional verification of microprocessor

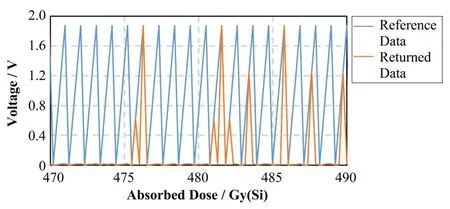

在完成在线测试系统的硬件设计调试及配套软件开发后,利用市售集成芯片分别在常规条件和60Co源辐照条件下,逐一对比验证了所有校验方式的可行性。图3是ADC校验对周期性模拟信号采集处理后的返回值与参考值的对比结果,校验频率为5 Hz,测得ADC功能损伤剂量为384.34 Gy(Si)。受电离辐射影响,ADC中PMOS管扩散区附近的场氧化层出现大量的陷阱电荷,造成CMOS带隙基准电路电压漂移加剧,器件噪声显著上升,出现失码(Missing Code)错误,进而造成被测器件ADC校验返回值出现漏发、错发现象。

图3 ADC采样返回值与参考值的对比Fig.3 Comparison of ADC sampled and reference values

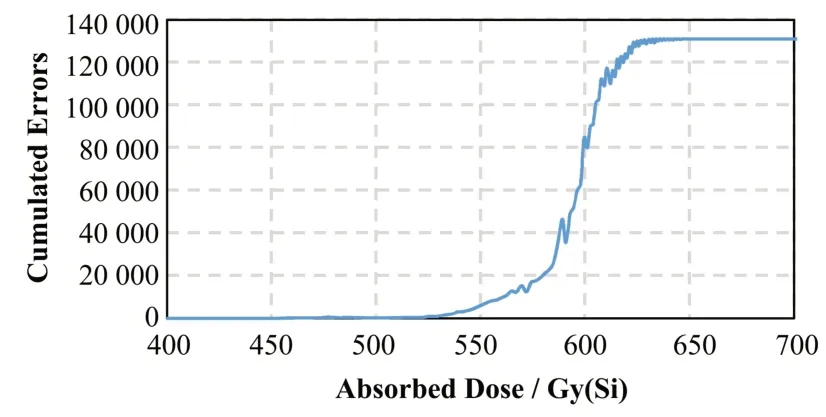

图4是Flash存储器失效过程中校验位错数量随受照剂量的变化情况,校验频率为5 Hz,测得样品的校验错误剂量为438.39 Gy(Si)。校验错误的逐步累积,体现了辐照期间由于辐射导致器件浮栅中载流子出现复合和光电发射,浮栅阈值电压逐渐降低,进而引发存储器读取功能的逐步失效。校验错误曲线存在一定波动性,体现了辐照期间存储器外围电路中灵敏放大器的电气性能退化,以及行列译码器出现随机性地址读出错误,对器件读取功能的叠加影响。

图4 存储器累积校验错误随受照剂量的变化Fig.4 Change of cumulative verification errors of memory with irradiation dose

3 在线测试系统的初步应用

利用研制的在线测试系统,初步开展了40 nm微处理器的总剂量失效模式实验研究。

3.1 实验条件

实验样品选用意法半导体公司的STM32H743型微处理器。该微处理器为40 nm制程,采用400 MHz的Arm Cortex-M7核心,内置2 MB Flash和1 MB RAM存储器,包含两个12位DAC、3个16位快速ADC以及22个16位/32位定时器,配备6个SPI、4个UART、4个I2C、2个SDIO通信接口,具有4路内部数据传输DMA。总剂量失效表征采用Flash校验、RAM校验、ADC校验、DMA校验、DAC校验、时钟采样、定时器采样、串口通信校验、SPI通信校验、I2C通信校验、SDIO通信校验、功耗电流采集等12项综合校验方式,其与微处理器内部布局的对应关系如图5所示。

图5 校验方式与微处理器布局的对应关系Fig.5 Corresponding relationship between verification mode and microprocessor layout

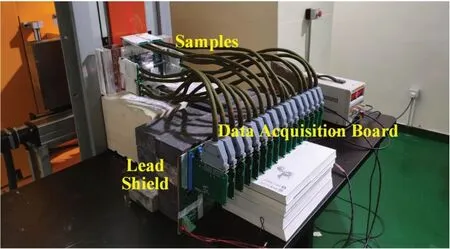

利用中国辐射防护研究院计量站60Co参考辐射装置开展辐照实验。实验样品共16个,每4个一组,吸收剂量率为48.85 Gy(Si)·h-1、33.81 Gy(Si)·h-1、32.97 Gy(Si)·h-1和24.12 Gy(Si)·h-1,累积辐照时间16 h。实验过程中,仅有被测样品电路直接暴露在辐射野中,测试系统其余部分利用铅屏蔽进行防护,如图6所示。

图6 辐照实验布局图Fig.6 Layout of irradiation experiment

3.2 实验结果

在辐照过程中,16个样品的参数和功能状态的变化趋势总体一致:刚开始所有校验功能状态均正常,除功耗电流略有变化外,其他采集参数均保持稳定;当吸收剂量达到一定值后(16个样品的平均值为(377.44±20.34)Gy(Si)),信号采集电路与样品之间数字信号交互突然中断,只有ADC校验、DMA校验、DAC校验、时钟采样、定时器采样、功耗电流测量仍能返回数据;停止辐照后,样品断电重启仍无法正常运行预载程序,并且不能重新编译。

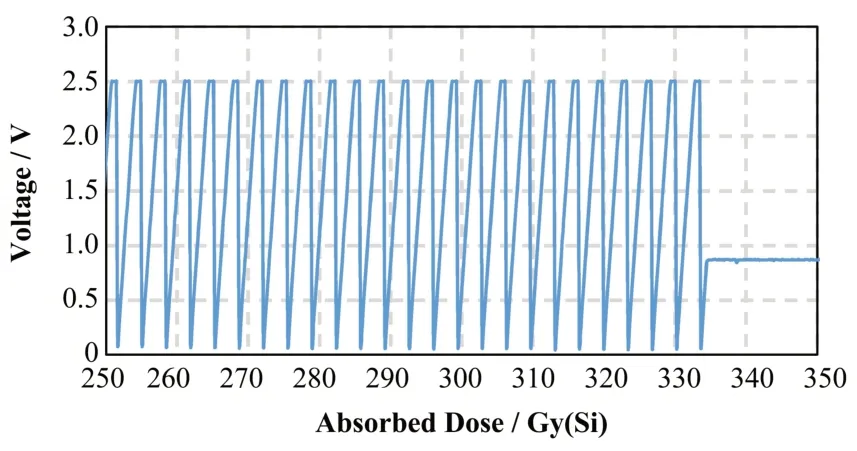

以第16号被测样品为例,受照334.69 Gy(Si)后数字通信中断,12项参数测量或功能校验的具体情况 如 下。UART、SPI、I2C、SDIO通 信 校 验 以 及Flash、RAM存储校验在中断前未出现任何数据校验错误,中断后4种通信校验结果同时报错、存储校验停止回传数据;定时器和时钟采集信号未受到影响,整个实验过程中的校验结果均保持正常;ADC校验、DMA校验、DAC校验在中断前正常,中断后ADC和DMA的输出值变为0,DAC则持续回传通信中断前的最后一个电压值,如图7、8所示。

图7 ADC校验结果Fig.7 Result of ADC verification

图8 DAC校验结果Fig.8 Result of DAC verification

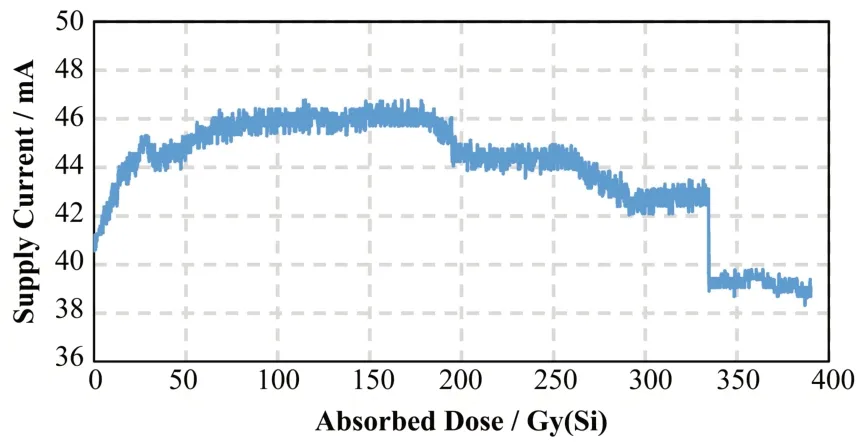

对于功耗电流,在整个实验过程中呈现“先上升后下降”的变化趋势,在数字通信中断后出现“跳变式下降”,如图9所示;初始功耗电流为39.8 mA,受照期间的最大值为46.2 mA,信号中断前平均值为39.2 mA,中断后平均值为37.7 mA。而非辐照条件正常运行预载程序时,被测样品功耗电流的变化幅度小于±1 mA。

图9 功耗电流监测结果Fig.9 Measurement results of current consumption

4 讨论

首先,定时器和时钟校验信号的通路为“内核(初始化)-晶振-通用IO”,在实验中始终正常可以确定通用I/O、晶振模块未失效。

其次,存储器失效通常是图4中存储位错数量逐渐增加的一个过程,而通信中断前Flash、RAM都未出现存储位错。CMOS器件的γ辐照失效主要由晶体管阈值电压漂移导致的沟道通断控制失调引起的,不同模块的总剂量失效阈值通常会因各晶体管阈值电压呈正态分布而表现一定的个体差异;实验中4个相互之间无数据交换、并行工作的数字通信接口在同一时间停止工作,大概率不是由通信接口硬件的辐照失效引起。因此,大概率推断片内RAM、Flash存储模块和UART、SPI、I2C、SDIO通信模块未失效。

再次,片内DAC是一种可独立工作的被动模块,其输出值来自内核预设输出公式的计算结果;DAC校验信号未中断回传说明硬件未失效,而输出非零固定值推断是内核中DAC输出计算相关模块失效导则无法更新输出值。此外,DAC校验的信号通路为“内核-DMA-DAC-通用I/O”,并且ADC与DMA的输出变化一致,推断芯片内部数据传输模块DMA未失效。故DAC、DMA模块应该是正常的。

最后,考虑到通信功能是由内核相关模块、内部数据传输、通信接口硬件共同实现的,由通信中断推测样品的辐照最敏感单元为内核,失效模式很可能是内核的部分指令无法执行所引起的。

上述推断与功耗电流变化趋势的分析如下:受照初期,样品中各晶体管漏电流增加,沟道通断控制未失效,所以功耗电流逐步上升但功能正常;随着受照剂量增加,沟道通断控制失效会使片内模块停止工作,从而使功耗电流突然下降。被测样品在所有外设关闭、仅有内核与总线工作时的典型动态功耗为36 mA(运行频率为200 MHz);通信中断前后由39.2 mA突然下降至37.7 mA,与内核及时钟、DAC等模块仍在运行、但部分模块(RAM、Flash、ADC、数字通信接口等)因内核指令无法执行而停止工作的推测是相符的。

随着CMOS器件特征尺寸达到纳米尺度,晶体管两侧的场氧化层成为总剂量效应等最敏感区域[19]。对 于 采 用 浅 沟 槽 隔 离(Shallow Trench Isolation,STI)技术的器件,当覆盖在P型表面的场氧化层中不断积累正电性的陷阱电荷时,表面会出现反转,场氧层下形成一个N型区域。随着反转的发生,导通路径出现,这将大大增加泄漏电流。一方面,源极和漏极之间的沟道边缘会出现寄生漏电通路,另一方面,N型金属氧化物半导体晶体管(NMOS)源漏极和相邻P型金属氧化物半导体晶体管(PMOS)的N井之间也可能出现漏电通路,这会显著提升器件的功耗。因此随着累积剂量的增长,被测样品的功耗电流从39.8 mA增长到了最高46.2 mA。

除此之外,总剂量效应在场氧中产生的界面态和氧化层陷阱电荷会引起晶体管的阈值电压漂移。对于PMOS管,界面态和氧化层陷阱电荷均会引起晶体管阈值电压的负向漂移;对于NMOS管,氧化层陷阱电荷会引起阈值电压的负向漂移,而界面态会引起正向漂移。随着累积剂量的增加,被测器件的晶体管阈值电压漂移加剧,栅极电压逐渐失去对沟道通断的正常控制,从而引起器件内核错误,程序执行错误陷入死机状态,进而导致依赖内核工作的外设停止工作,器件功耗电流骤降至37.7 mA。

5 结语

首先,与辐照后离线测试或者功能校验相比,耦合芯片参数测量及互异性功能校验的在线原位测试方法,实现了对器件内核、模拟外设、通信外设、数据访问、片内存储、时钟等功能及硬件单元辐照失效的准确定位,提升了对微处理器辐照失效模式表征的精细程度。其次,总剂量效应可扩展式在线测试系统具有较好的兼容性,可用于不同硬件封装、不同通信方式和不同特征尺寸的微处理器及其他一系列主动/被动器件的总剂量效应测试。与此同时,在线测试系统较丰富的硬件配置,确保其后续可以增加新的功能校验方式,或对已有校验算法进行升级,从而实现校验功能的扩展。然而,由于微处理器集成度高、功能丰富、内部结构复杂并且存在功能状态突然失效的情况,通过外部引脚测量或功能校验获取的信息仍然有限,在必要的情况下可以考虑在线测试、器件局部准直辐照、芯片功能级辐照失效仿真相结合的失效模式分析方法。

作者贡献声明陈法国:负责在线测试系统的总体设计、文章的起草和修订;于伟跃:负责测试方法的设计;梁润成:负责辐照实验设计、数据采集和分析;郑智睿:负责测试系统软件开发;郭荣:负责测试系统硬件开发。