实用计数器的VHDL与Verilog HDL行为建模对比研究

杨云海,章芬芬

(韶关学院 信息工程学院,广东 韶关 512005)

0 引 言

硬件描述语言(以下简称为HDL)在电子设计自动化(以下简称EDA)过程中,可以用于数字电路的建模和仿真。计数器是一种常用的数字电路模块,在设计的过程经常会被设计、调用。使用目前最为常用的两种HDL(即VHDL与Verilog HDL)对实用计数器进行行为建模,并对比两种语言的建模结果,对实用数字电路的设计有一定的指导作用,有一定的研究意义。

1 实用计数器功能规划

考虑到计数器模块的实用性,能更方便地引入到更高层级的设计中,计数器模块的控制接口要比较丰富。除了要有时钟(clk)输入以外,还要包含的控制信号有:异步清零(rst)、时钟使能(en)、同步装载(ld),等等;需要留有4位的装载数据输入端口(din);需要安排4位的计数输出端口(dout)和1位的进位(计满)输出端口(cout)。

2 实用计数器的VHDL行为建模

按照功能规划,使用VHDL行为描述语句对电路进行建模。电路模型的VHDL代码如下:

在程序中,由于需要使用了标准逻辑矢量(STD_LOGIC_VECTOR)与整形数据的加法操作,对“+”运算符进行了重载,并且使用了数据类型转换函数,在整形与标准逻辑矢量之间进行数据类型转换。因此,需要打开IEEE库中相应的包。

在结构体中定义了一个“q”信号,在“reg”进程中定义了一个“q1”变量。其中,“q1”变量用于暂存计数的结果,“q”信号用于把“q1”的计数结果传递出进程以外。这样的设置,层次分明,结构清晰,提高了代码的可读性,为以后对模块的修改提供了方便。

在代码中,使用了2个进程(Process)表达电路的行为,进程的标号分别为:“reg”和“com”。其中,“reg”进程表达了电路的时序逻辑,在时钟信号“CLK”的推动下,计数器进行计数;“com”进程表达了电路的组合逻辑,根据“q”信号的取值情况,对计数输出“dout”和进位输出“cout”进行了驱动,把计数结果和进位结果传递出模块。

在时序进程“reg”中,由于需要对各种控制信号进行判断,使用了多层次嵌套的“if”语句。进程敏感信号列表与“if”语句的嵌套,实现了电路的异步复位、时钟使能和同步装载的控制功能。

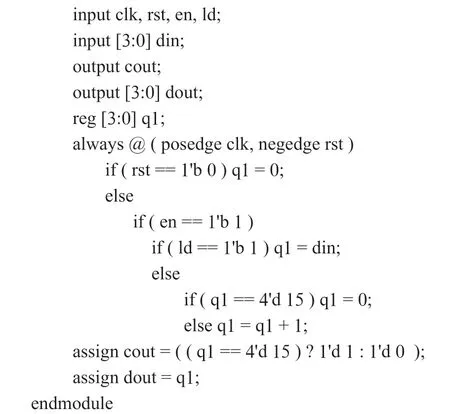

3 实用计数器的Verilog HDL行为建模

按照功能规划,使用Verilog HDL行为描述语句对电路进行建模。电路模型的Verilog HDL代码如下:

在代码中,先是对电路的输入、输出端口进行了定义,并定义了一个名为“q1”的寄存器类型变量(reg),用于计数结果的保存和累加。由于使用了“q1”寄存器,输出端口不需要在过程之内进行赋值操作,所以保持了输出端口“dout”和“cout”的网线(net)类型属性。

在“always”过程中,由“q1”变量实现对计数结果的暂存。敏感信号列表与嵌套的“if”语句实现了电路的异步复位、时钟使能和同步装载的控制功能。

“q1”的计数结果由并行的连续赋值语句传递给输出端口“dout”,并通过条件赋值语句对计数结果进行判断后,决定进位输出端口“cout”的值。

4 VHDL与Verilog HDL综合结果比较

为了方便对比实用计数器的两次电路建模,在2次的设计中,均采用了相同的输入、输出端口名称,模块内需要用到的信号、变量等标识符,也采用了相同的名称。完成电路的行为建模以后,采用了Quartus Prime平台,选择使用Intel公司的FPGA,Cyclone 10 LP系列,10CL006YU256C8G 型号的PLD器件,对电路分别进行了实现(全程编译,即各层级的综合),并进行了功能仿真。

在Quartus Prime平台上完成全程编译以后,VHDL与Verilog HDL两次设计的编译报告内容都是一样的,如图1所示。

图1 实用计数器VHDL与Verilog HDL设计的编译报告

编译报告显示,2次的设计,均使用了器件上的8个逻辑单元(LE),使用了4个寄存器(Register),和13个引脚(Pin)。由编译报告可知, 2次设计所使用的PLD器件上的逻辑资源数量,是一样的。

通过查看2个设计的所产生的RTL网表,对比2次设计所形成的电路结构。图2显示了2次设计所形成的RTL网表的对比。

由于2次设计所使用的输出、输出端口,以及设计中用到的其他标识符都尽量统一了名称,所以,两次设计形成的RTL网表结构相同,大部分元件的名称也一致(不一致的位置,只有4位寄存器元件的名称)。由RTL网表可知,两次设计形成的结果应该是一致的。

为了验证设计的正确性,以及验证2次设计所形成的结果,功能是否达到要求,功能是否一致,分别对2次设计进行了功能仿真。图3显示了2个设计的功能仿真结果。

图2 实用计数器VHDL与Verilog HDL设计结果的RTL网表对比

图3 实用计数器VHDL与Verilog HDL设计结果的功能仿真结果对比

为了比较直观地对比2次设计的仿真波形,把2个设计的仿真输入信号设置为完全一样。通过对比两次仿真的输出结果,得到的结论是——功能仿真结果完全一致。功能仿真结果的一致,也验证了2个设计RTL网表基本一致的情况。

对于2次设计的功能仿真进行分析,考查设计结果是否满足设计需求。从图3的仿真波形可以看出:异步复位(rst)、时钟使能(en)、同步装载(ld)的控制功能均已实现;计数输出端口“dout”的范围是0—15,计满时(计数到达15的时候),进位输出“cout”拉高。

因此,2次设计的结果是样同的,并且都是符合功能规划的。

5 VHDL与Verilog HDL建模方法对比

通过对比实用计数器的VHDL与Verilog HDL行为建模,比较两种硬件描述语言在使用上的异同点。

5.1 相同的方面

使用两种不同的HDL,在EDA流程上是相同的,即都是采用:文本设计输入、全程编译、设置矢量波形文件、仿真,这几个步骤开展电路的设计与验证。当然,使用不同的HDL,可能要在平台上对于仿真所使用的语言进行设置,但并非是所有平台都需要这一设置,早期版本的Quartus就不需要作这一设置。所以,使用不同HDL进行设计输入,基本不会影响EDA的各个流程。

5.2 不同的方面

使用不同的HDL进行电路建模,最大的不同在于——不同HDL对于电路功能的描述方法。以本文实用计数器的2次建模为例,虽然2次设计所实现的内容完全一样,但不同的HDL的描述方式区别很大。经过对比与总结,得出以下使用VHDL与Verilog HDL进行电路建模的不同之处:

(1)在程序结构方面的不同。VHDL结构严谨,代码的层次清晰,但要写的代码较多。

Verilog HDL结构则较为自由,语句的组织比较松散,但需要写的代码比较少。

(2)在数据类型要求方面的不同。VHDL对于数据类型有严格的要求,需要引入库、包,对运算符进行重载,才能实现不同数据类型对象之间的运算(算术运算、比较运算、逻辑运算,等等)。禁止不同类型数据的对象之间的赋值。要完成赋值,必须要先进行数据类型的转换,因此需要引用一些包含数据类型转换函数的包。

Verilog HDL中的数据都被看作为“矢量”,在运算和赋值时能自动转换,设计者不需要区分数据类型,程序中不需要进行数据类型的转换,即可对数据对象进行运算和赋值等操作。

(3)与电路的映像方式不同。可综合的HDL语句都要变成逻辑电路结构,因此,HDL可综合语句都会和一些电路元件实现相应的映射。但不同的HDL,语句与电路元件映射的方式和风格,是有所差别的。

VHDL对于电路的行为描述能力较好,行为描述结构清晰,逻辑清楚,易于为人们所理解,但对于电路的映射,显得层级较高,并不能达到一一对应的关系。

Verilog HDL的行为描述语句则与电路结构有着较好的映射关系,比如:在本例中创建寄存器类型(reg)的变量,在综合后会形成电路中的寄存器;语句中的各种条件判断,也会映射为电路中相应位置的各个比较器。

总之,两种硬件描述语言各有特点,各有优势,无所谓孰优孰劣。

6 结 论

本文通过对比VHDL与Verilog HDL对于实用计数器的行为模型,能得到两种语言的不同特点,对于今后开展数字电路的建模和设计,有一定的帮助。