电气设备剩余电压的可靠性研究与方案设计

韩书磊,张威,周月飞,王艳飞

(空调设备及系统运行节能国家重点实验室,珠海 519070)

引言

剩余电压是电气设备断电之后常见的现象之一,为保证用户在使用过程中的人身安全,在设计时会将剩余电压限制在一个安全的范围之内,对此,从安全角度出发GB 4706.1《家用或类似用途电器的安全通用要求》[1]、GB 4943《设备技术信息(电气事务设备)的安全》[2]、GB8898《音频、视频及类似电子设备安全要求》[3]等都对剩余电压在不同角度提出了限制要求。

曹俐[4]等研究了一种过零检测电路,与可调延时设计配合能使设备在交流峰值处准确断电,陈永强[5]等研究了剩余电压在电磁干扰和人体安全电能方面影响,何勇[6]等从测试标准的角度分析了电气设备的测试方法,庞聪[7]等研究了标准限值的由来和对测试设备的要求。

目前行业内虽然对剩余电压的产生和检测方法有了一定的研究,但对降低剩余电压的方法并没有完善的理论依据和具体的设计方案。本文通过将设备电路简化,推导剩余电压的计算公式为降低剩余电压方案提供理论依据,然后根据公式设计降低剩余电压的方案并通过实际案例验证不同方案的可靠性。

1 剩余电压的产生机理

在常见的设备电路中,为了实现各种功能常会在电路中添加电感、电容等元器件,此类元器件具有一定的储能作用,在设备通电时会存储一定的电能。设备断开电源连接后,这些元器件会释放出内部储存的电能,使得断电之后电路中的电压并不是立即消失,而是随着时间逐渐衰减归零。因此电气设备断电之后会存在剩余电压,而过高的剩余电压在使用过程中可能会对用户造成电击伤害,影响使用安全。将电路中的剩余电压短时间内快速消耗是所有厂商必需关注的问题。

2 剩余电压理论模型

当电气设备与外部电源线路断开连接时,由于电路中电感的储能远小于电容,可以将内部电路总电容和总电阻简化为简单的RC电路,此时电路内部的电能消耗等效于一般RC电路的零输入响应状态由此建立剩余电压理论模型。

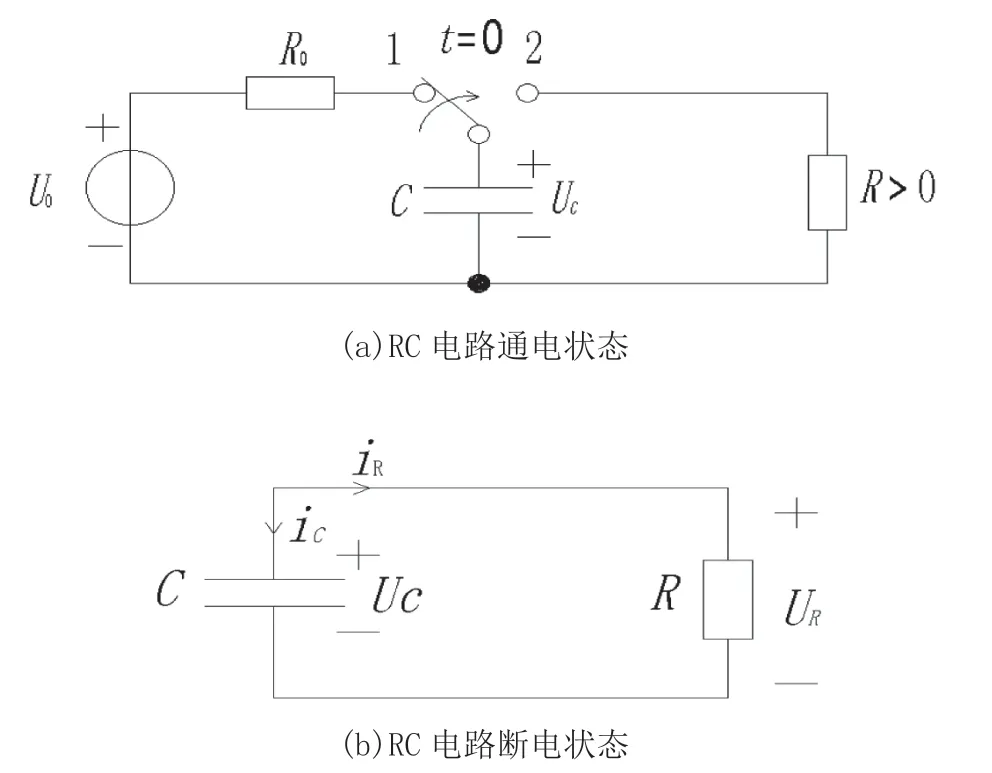

在电路断电之前(t≤0时)电容电压与电源电压相等,断电后由电容C提供电流如图1所示,也即:

图1 RC电路图

剩余电压以相同的指数规律衰减,衰减的快慢取决于R和C的乘积。在电气邻域中研究人员取τ=RC,以此观察当时间t=0,τ,2τ,3τ...情况下内部电路剩余电压的衰减情况。

以上剩余电压计算公式的是基于理论模型推导出的,剩余电压Ut的衰减主要取决于RC,在实际应用中由于电路内部元器件的设计偏差等因素影响,实际测试值会有一定的偏差。

3 剩余电压优化方案与可靠性验证

基于上述剩余电压理论计算公式可知,当时间t一定时,剩余电压与RC的值呈正相关,R和C的乘积越小,电路中剩余电压的衰减速度越快,剩余电压值越小。所以降低剩余电压的多通过调整电路中的电容C和电阻R而制定的。下述方案使用EMI接收机、功率吸收钳、V型人工电源网络、峰值断电器、示波器以及100 MΩ探头在电磁屏蔽室中验证各方案的效果与影响。

3.1 优化放电电阻

设计电路的阻性负载多种多样,为了实现各种功能在电路中用以减小通过元器件电压的串联电阻,减小元器件电流的并联电阻以及各种非纯电阻负载元件。更改此类电阻影响因素复杂多变,因此大多数厂家会专门设计放电电阻与后端负载电路并联,然后利用放电电阻进行放电,根据并联电阻计算公式设计的放电电阻越小,实际电路的等效电阻值也越小,相应的剩余电压衰减越快。

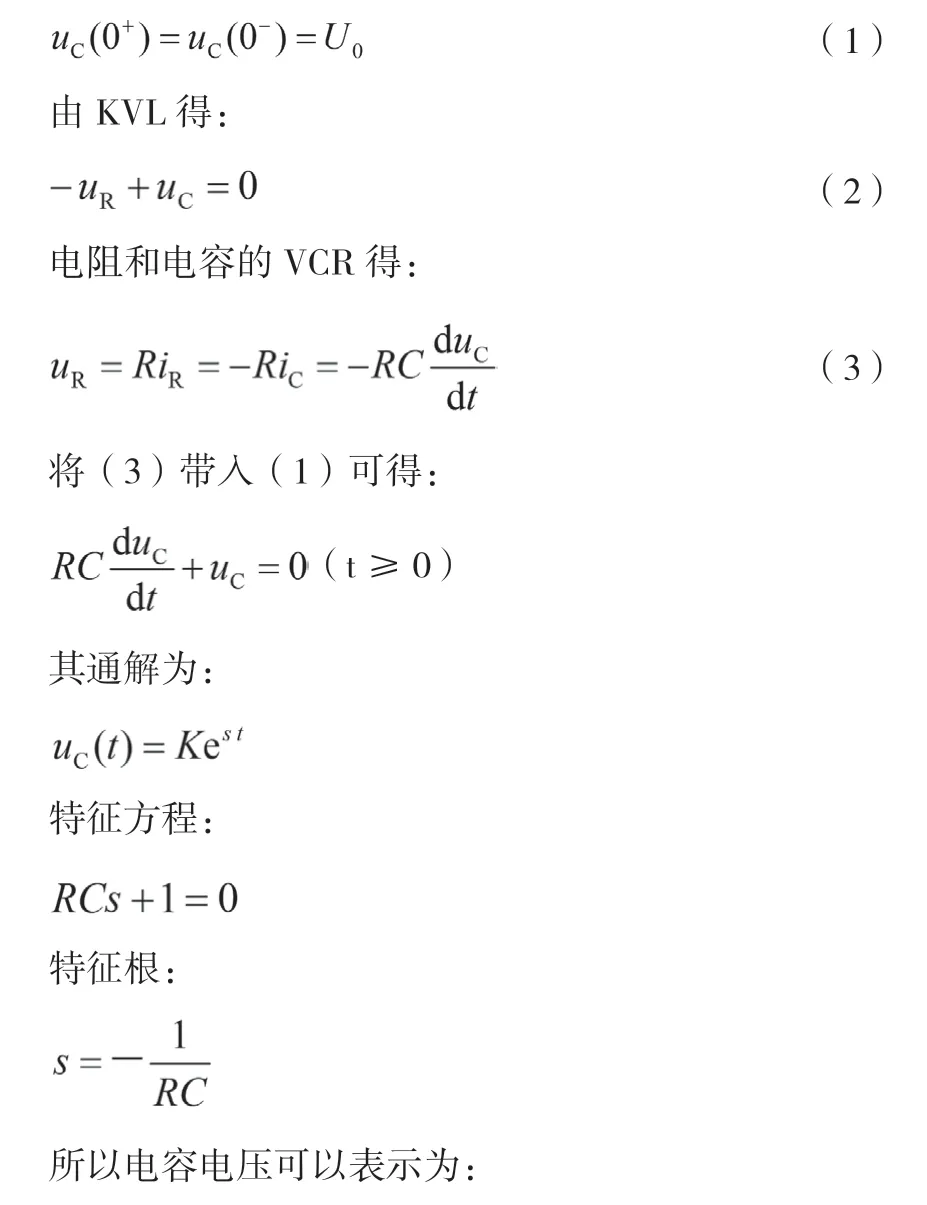

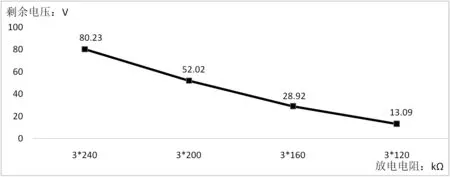

图2为某电气设备AC输入端滤波设计电路图,原设计电路中放电电阻值R为3*240 kΩ,实测断电1 s后的剩余电压Ut最大值为80.23 V,为了降低剩余电压调整放电电阻并进行实测验证,测试数据如图3所示。

图2 更改放电电阻前输入端滤波电路与剩余电压实测图

图3 降低放电电阻时剩余电压变化趋势图

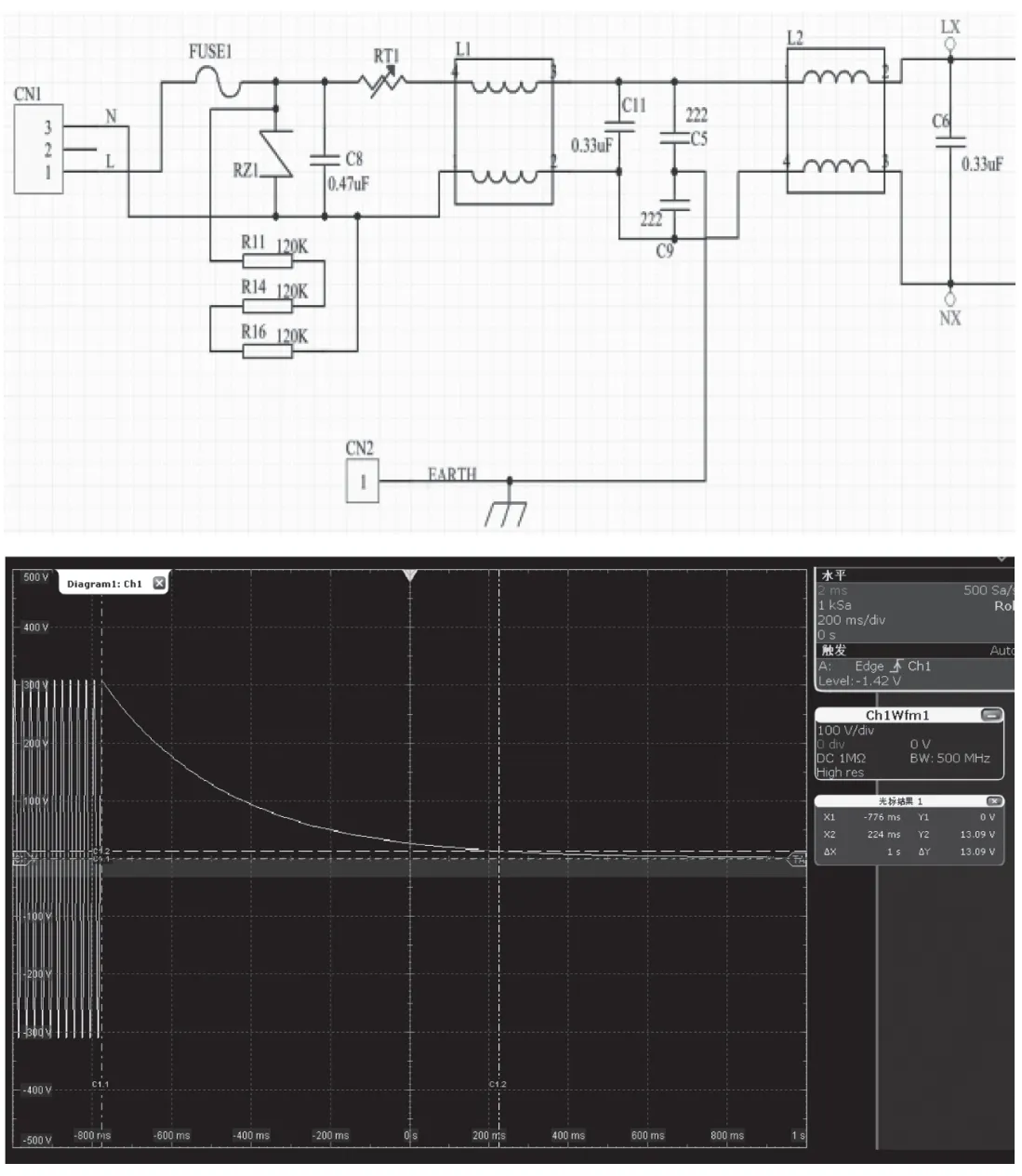

考虑到受测设备的一致性剩余电压实测数据可能存在一定的波动,最终决定将放电电阻值降低为3*120 kΩ,此时测试断电1 s后最大剩余电压值为13.09 V,如图4所示。

图4 更改放电电阻后输入端滤波电路与剩余电压实测图

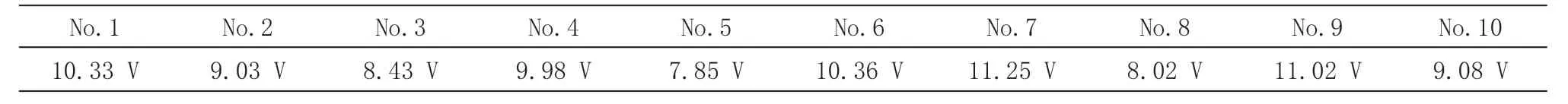

为确保方案可靠性,针对上述方案随机抽取10台设备测试剩余电压,实测数据如表1。

表1 更改放电电阻可靠性验证数据表

从测试数据可以看出方案效果稳定,调整放电电阻可以有效的降低剩余电压,但设备待机时纯电阻元件消耗功率为P=U2/R,额定220 V电压下放电电阻的待机功耗0.134 W,相当于增加了设备的功耗降低了设备能效利用率,降低放电电阻R会导致电气设备的功耗进一步上升。在节能减排的国际背景下,欧美等国对电气设备待机功耗都有严格限制,一般要求遵从国际“1 W”的倡议,这对设备的待机功耗影响极大,我国暂时对待机功耗没有明确要求,但也有能效等级要求。所以在降低放电电阻方案时,需要考虑对待机功耗、耗电量、能效等方面的影响。

3.2 优化X电容

电容在电路中的作用很多,除了常见的电解电容之外还有用以抑制电路电磁干扰、对电源整流滤波的X电容和Y电容。其中Y电容主要用于抑制电路中的共模干扰,使用的电容量较小,一般为pF级,由于其一端连接L/N线路一端连接功能地上,所以设计容量不能过大,否则可能导致设备的泄漏电流超过相关的安全标准。X电容用以抑制电路中的差模干扰,单个X电容通常设计在(0.1~0.47)μF,但一般设备的滤波电路会使用多个X电容与电感并联来达到更好的滤波效果,客观上电源输入端的滤波电路设计中为了达到更好的滤波效果,X电容越大效果越好。

在基准时间要求较高的振荡电路或定时、延时电路中,若电解电容容量减小,可能造成振荡频率偏高,定时周期变短,造成时间误差。这可能导致许多系统功能不稳定甚至无法运行的现象。同时由于Y电容容量小,调整Y电容对剩余电压影响远小于X电容,且对共模干扰影响较大,所以常通过调整X电容的方式来达到降低剩余电压的目的。

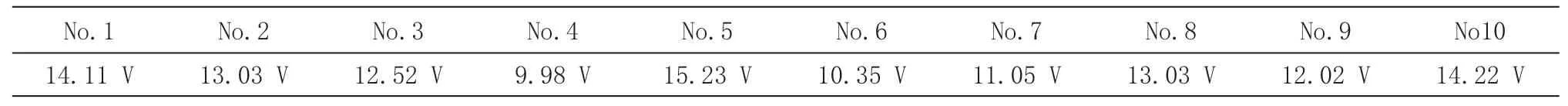

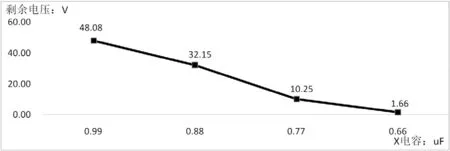

在某设备AC输入滤波电路中,L、N线路上并联3个电容量为0.33 uF的X电容,此电路断电1 s后的最大剩余电压实测值为48.08 V如图5。为了降低剩余电压调整电路中的X电容并进行实测验证,测试数据图6所示。

图5 更改X电容前输入端滤波电路与剩余电压实测图

图6 降低X电容剩余电压变化趋势图

考虑到受测设备的一致性剩余电压实测数据可能存在的波动以及电路的抗干扰能力,最终决定将X电容值调整为0.33+0.22+0.22μF,此时测试断电1 s后最大剩余电压值为10.25 V。

对设定的方案进行可靠性验证,针对方案随机抽取10台设备测试剩余电压,实测数据如表2所示。

表2 更改X电容可靠性验证数据表

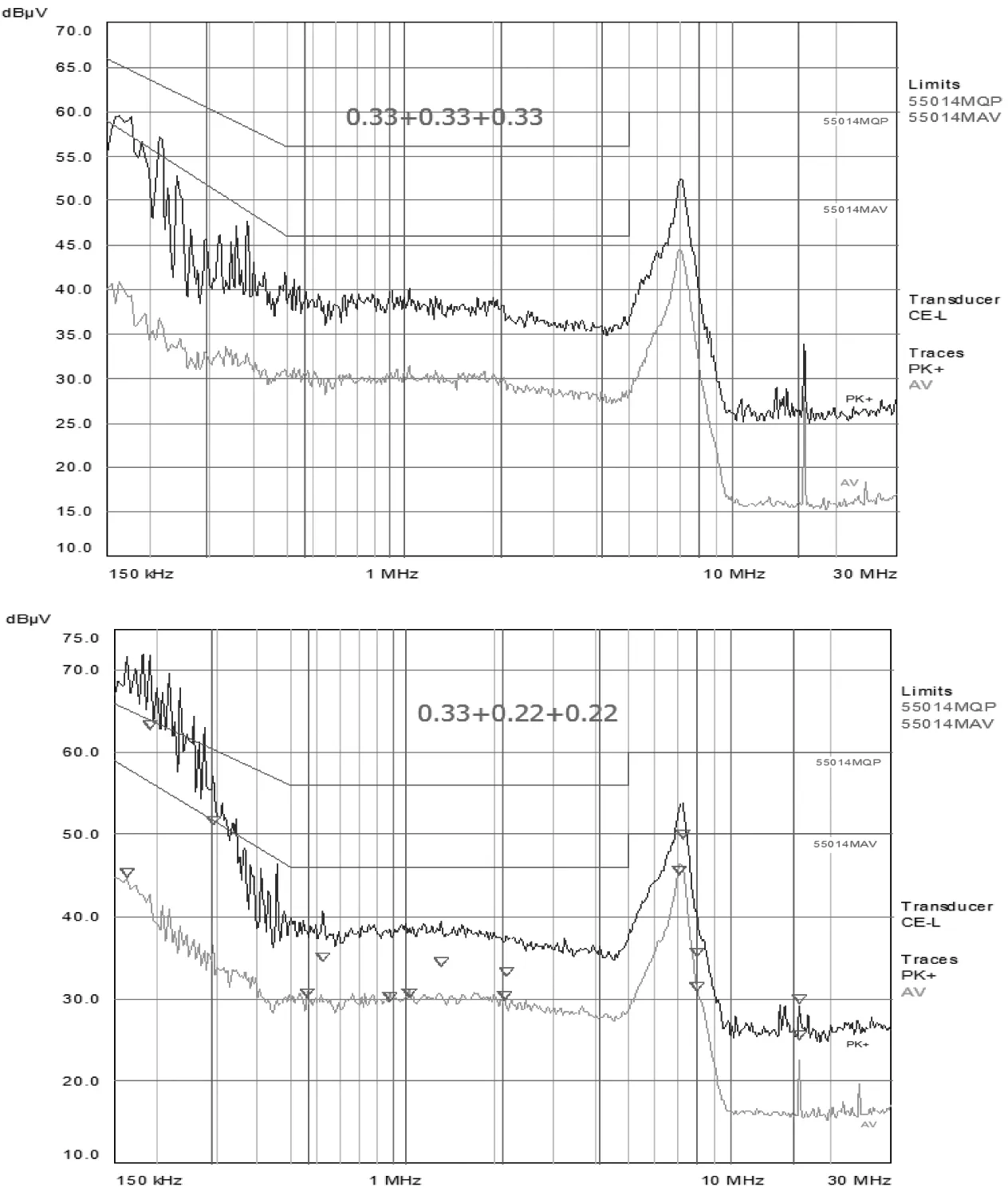

从测试数据可以看出方案对降低剩余电压效果稳定,但是降低X电容会影响电路的抗干扰能力,设备更改电容之后骚扰电压在150 kHz~1 MHz频段时干扰信号明显上升见图7,但仍在限值之内。

图7 更改X电容前后设备骚扰电压测试图

在电源滤波、交流(音频)耦合、交流旁路退偶、低频振荡等类似电路中的电容容量减小,理论上对系统不会造成太大影响,但实际上会影响电路的稳定性。如滤波不好,会造成电压波动影响元器件使用寿命和可靠性;耦合不好,会影响信息传输;旁路不好,会造成电路自激干扰等。上述更改X电容方案中,虽然实测EMI骚扰电压均值仍在限值内,但也存在150 kHz~1 MHZ范围余量较小的情况,这也意味着电路的抗干扰能力下降。

3.3 同时调整放电电阻和X电容

实际上设计电路时也会出现单独调整电阻R或电容C无法达成降低剩余电压至目标值, 或者调整后影响电路稳定性导致方案无法被接受,这种情况可以同时调整电阻和电容来达成预定降低剩余电压的目标。

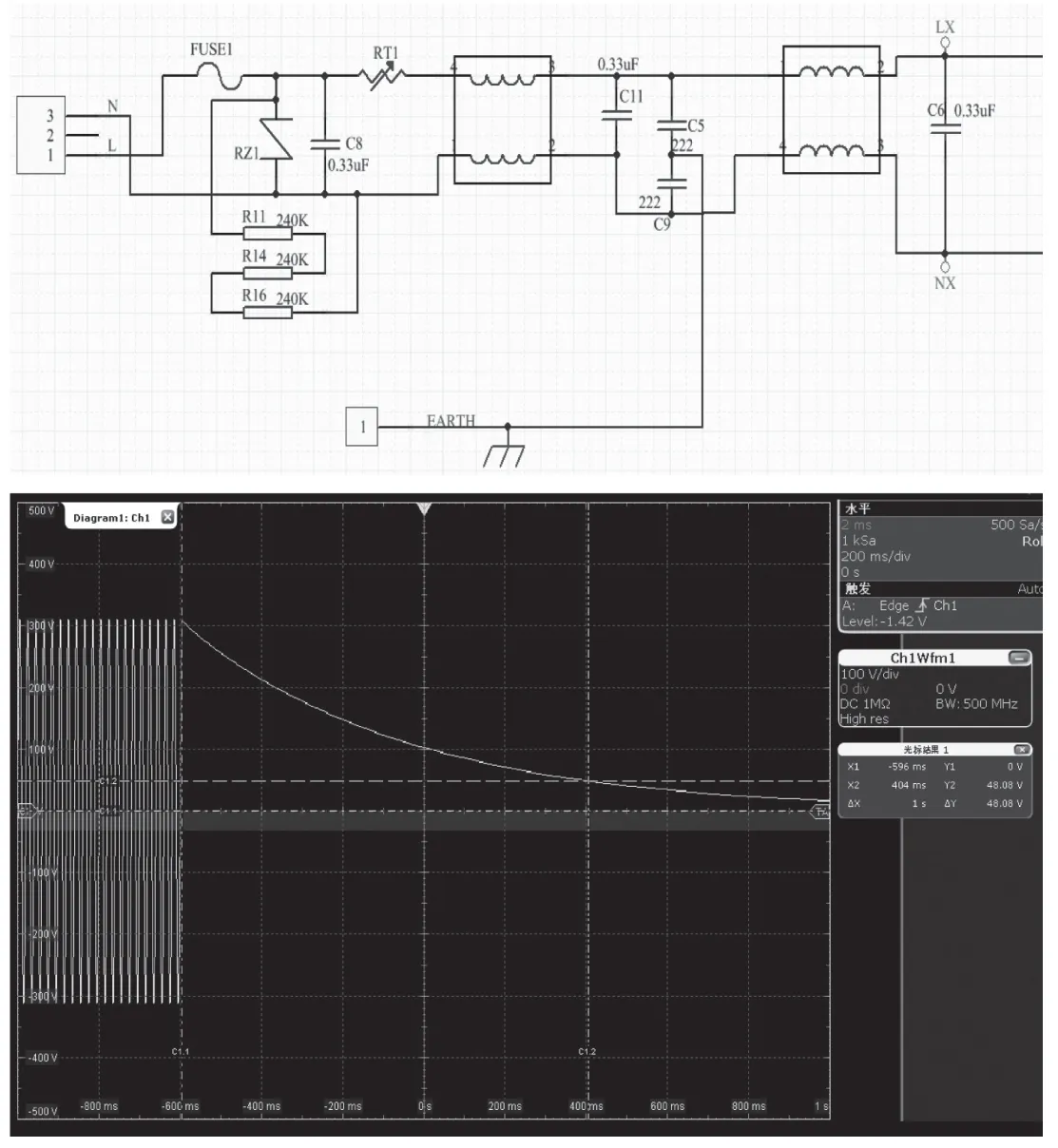

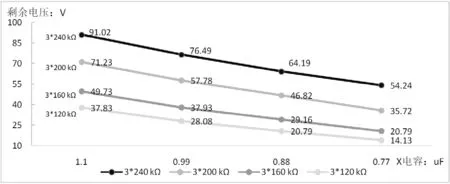

在某设备电路设计中初始方案电路采用3*240 kΩ放电电阻和0.47+0.33+0.33 uF的X电容,实测断电1 s后最大剩余电压值91.02 V。为了降低剩余电压调整X电容并进行实测验证,测试数据如图8所示。

图8 降低RC时实测剩余电压变化趋势

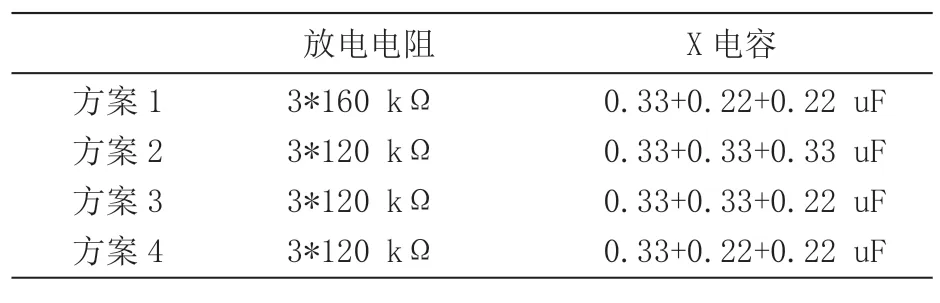

考虑到受测设备的一致性,实测数据可能存在波动,初步设定方案如表3。

表3 初步设定方案

对设定的方案进行可靠性验证,针对设定的四种方案随机抽取10台设备测试剩余电压,实测数据如图9所示。

图9 方案可靠性验证数据图

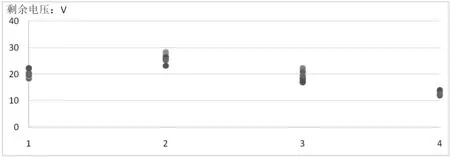

四种方案实测均能降低剩余电压且效果稳定,验证更改后的待机功率发现:方案1的待机功率最低,方案2、3、4的待机功率相同,但均在限值范围内。对X电容的改动可能影响电路抗干扰能力,四种方案EMI骚扰电压测试如图10。

图10 四种方案骚扰电压测试图

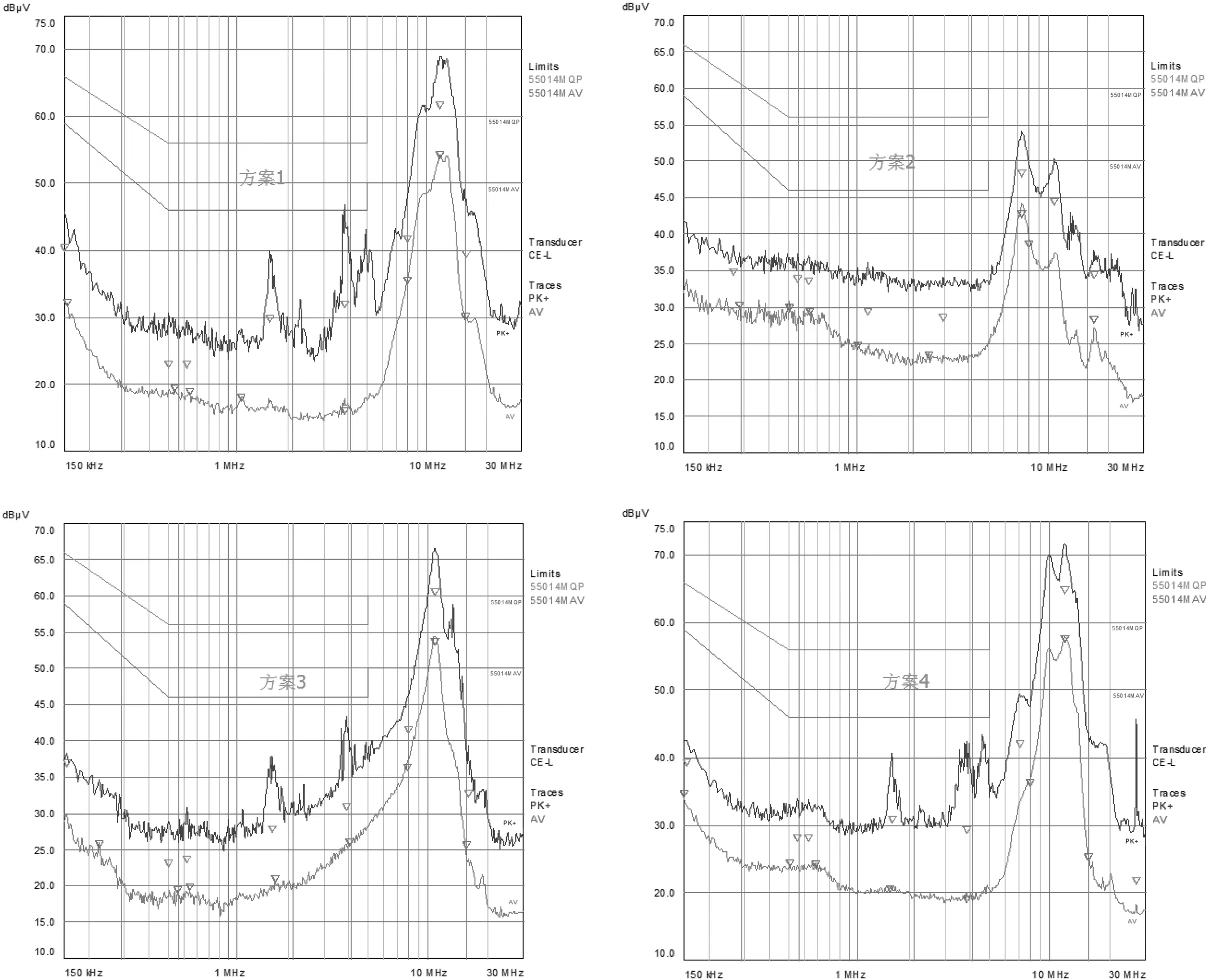

从方案的骚扰电压测试结果可以看出选用方案2电路抗干扰能力最好,由此确定方案:将电路中的放电电阻R改为3*120 kΩ,X电容改为3*0.33 uF如图11所示。

图11 更改方案后输入端滤波电路图

相较于单纯的降低放电电阻或X电容,同时调整两者在多数情况下对降低剩余电压的效果更好,这从理论计算公式也能看出,但是在实际电路设计时同时调整两者相对更复杂,需要同时考虑待机功耗和电路稳定性。

4 结论

更改放电电阻、X电容的方案对降低电路剩余电压效果显著,理论上放电电阻与X电容设计的越低电路的剩余电压衰减越快,但是在调整RC之后需要对相关电路重新评估和试验验证。为此总结降低剩余电压的设计方案与影响分析为广大设计者提供参考:

1)单独调整放电电阻是一种简单直接降低剩余电压的方法,对后续电路功能与稳定性的影响较小,但是会增加设备的无用功耗,特别是对设备的待机功率影响极为明显,设备能效利用率降低,在不考虑设备功耗或者设计功耗余量较大时可以尝试选用;

2)单独调整X电容也是一种直接降低剩余电压的方法,缺点是可能影响到电路的抗干扰能力造成设备抗干扰阈值降低,在一些电源电压波动大、工作环境恶劣等设备电路中需要谨慎选用;

3)同步调整放电电阻和X电容对降低剩余电压的效果最好,对设备待机功耗和电路的抗干扰能力影响最小,缺点是方案周期较长需要不断验证试错,多用于一些成熟产品的拓展开发上。