基于DDR3的高速低功耗通用图像缓存设计

姜牟旬, 钟国强, 杨浩正, 邱继军, 常玉春

(大连理工大学, 辽宁 大连 116620)

0 引 言

在图像传感器的实际应用领域,存在很多亮度动态范围巨大的场景[1],例如卫星夜景图、室外直射太阳光等,这导致图像的亮暗部分无法在一张图上显示所有细节。高动态互补金属氧化物半导体(CMOS)图像传感器应运而生,并且不断发展,已经成为遥感卫星、科学研究、特种设备、民用消费等诸多领域不可或缺的重要部件[2]。

随着高动态CMOS图像传感器的像素分辨率提高,动态范围扩大,导致需要实时传输以及处理的图像数据量越来越大,给图像采集和传输系统带来更大的带宽压力。为保证图像的实时采集和传输处理,需要高带宽、高速率、大容量的缓存。双倍速率同步动态随机存储器(DDR SDRAM)可以满足高动态CMOS图像传感器的高速缓存需求,可广泛应用在图像数据的高速实时存储系统中[3]。

1 总体设计

1.1 系统设计

系统级测试框图如图1所示,使用XC7A100TFGG484-2型号的现场可编程门阵列(FPGA),设计DDR3核心控制模块以及驱动模块等,驱动DDR3芯片(MT41K128M16JT)和自研高动态CMOS图像传感器(CIS),并通过以太网接口与上位机通信,实现测试系统。

图1 系统级测试框图

DDR3核心控制模块管控数据流,前端承接CIS的高速图像数据流并按照像素阵列格式缓存,后端匹配相对低速的,传输过程不稳定的传输接口和上位机,确保能够完整地读取并显示每帧图像数据。上位机获取数据时,发送数据请求命令,包含帧数、行数、包数等信息,由DDR3核心控制模块解码并且映射到地址空间依次读出,数据流独立于命令流,依次经过写入缓冲区、DDR3芯片、读出缓冲区,最终由传输接口按数据包格式发送到上位机显示[4]。

验证方案使用分辨率为512×512的CIS,内部模数转换器(ADC)分辨率为12 bit,数据输出为4对低电压差分信号(LVDS)接口,数据采样时钟为1对LVDS接口,帧率为190 fps@150 MHz,带宽达1.12 Gbps。所用DDR3的工作频率为800 MHz,数据位宽为16 bit,理论带宽达12.5 Gbps。上位机灌包测试带宽小于100 Mbps。

1.2 DDR3核心控制模块设计

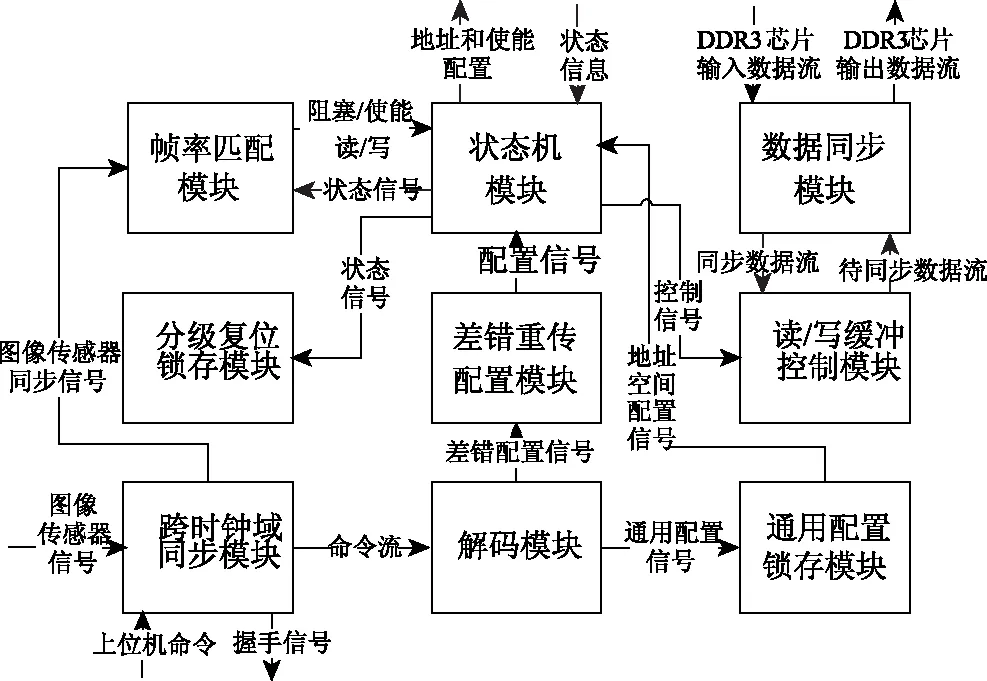

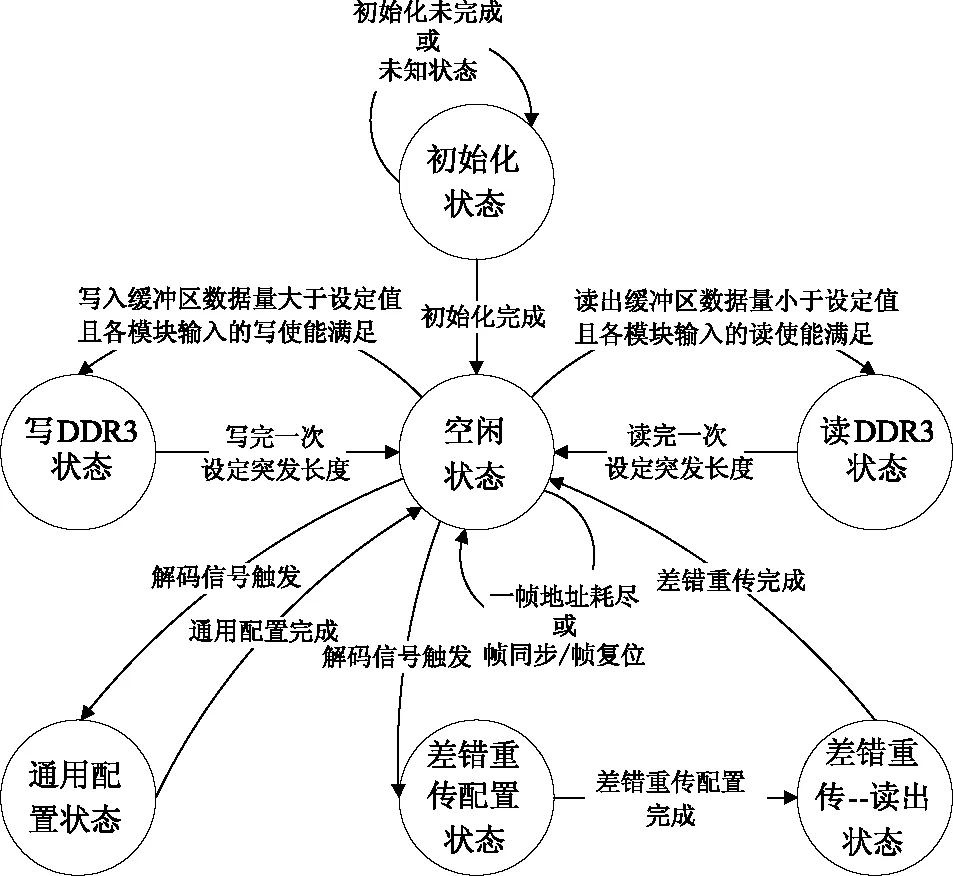

上述DDR3核心控制模块按功能划分为如图2所示的9个模块,其中的状态机模块如图3所示。

图2 DDR3核心控制框架

图3 状态机模块

跨时钟域同步模块对CIS输入的固定宽度脉冲信号延拓并打拍抓取;对上位机输入的命令信号做握手同步处理。帧率匹配模块输出阻塞/使能的读/写信号到状态机模块,实现从恒定速率写入DDR3。解码模块对命令信号判断、解析、计算,输出差错、通用配置信号。解码输出信号分别触发差错重传配置模块、通用配置锁存模块,处理并输出状态标志、起始地址、读取长度等配置信号到状态机。分级复位锁存模块由状态机模块触发,确保各级模块正常复位和使能,防止数据错位。读/写缓冲控制模块例化异步先进先出存储器(FIFO)为缓冲区,控制数据写入和读出FIFO。数据同步模块按通用配置锁存模块定义的突发长度读/写DDR3[5],做数据拼接及握手同步处理。

图3中,未知状态进入初始化状态,初始化完成进入空闲状态。为确保配置命令即时响应,防止缓冲区和DDR3地址溢出,空闲状态优先判断帧复位/帧同步信号,状态切换优先级为:通用配置状态、差错重传配置状态、写DDR3状态、读DDR3状态。

1.3 数据流管控基本计算

图像帧地址计算,帧管理的物理实现是BANK动态管理,每个BANK可寻址行数为16 k,列数Ncol为1 k,一个BANK的最大寻址空间Amax为

Amax=Nrow×Ncol

则Amax=16 777 216个。

测试所用CIS的ADC分辨率为12 bit,高位补零Pwidth到16 bit,共4个输出通道。考虑每行64 bit校验信号,则单通道数据量Nchannel为4 227 072 bit,CIS单帧图像寻址空间Faddress为

因此,CIS单帧图像寻址空间应小于1 056 768。

突发长度Lburst,是自定义每次写入/读出DDR3芯片的地址长度。为避免掩码降低读出速度和保证传输接口正常输出数据,突发长度需能被一帧图像的地址整除且能整除传输接口一个数据包的数据量[6]。一个数据包Dpack为8 256 bit,内部突发长度Linside为8,突发长度最小应为

因此,突发长度最小为129,为提高通用配置模块的容错性,突发长度固定为2个数据包的长度,因此可设置为129的整数倍。

读/写缓冲区最小容量计算。写入缓冲区的CIS写入时钟Cwrite为150 MHz,每6个时钟周期写1次数据,数据位宽Wdata为64 bit(4个像素数据组合),DDR3读出的时钟CDDR为100 MHz,每个时钟周期读1次数据,数据位宽WDDR为128 bit。突发长度Lburst定义为129,一次突发长度写入的数据量D1为

(4)

计算写入的数据量D1=2 064 bit。

一次突发长度从写入缓冲区读出的数据量D2为

D2=Lbrust×Linside×Pwidth

(5)

计算读出的数据量D2=16 512 bit。

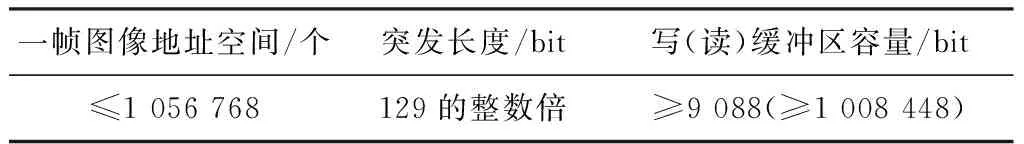

显然D2>D1,考虑缓冲区计数量的稳定需要70个慢时钟周期,写缓冲区理论最小容量9 088 bit。同理,读缓冲区最小容量应为1 008 448 bit。表1列出了数据流管控基本计算的参数要求。

表1 数据流管控基本计算表

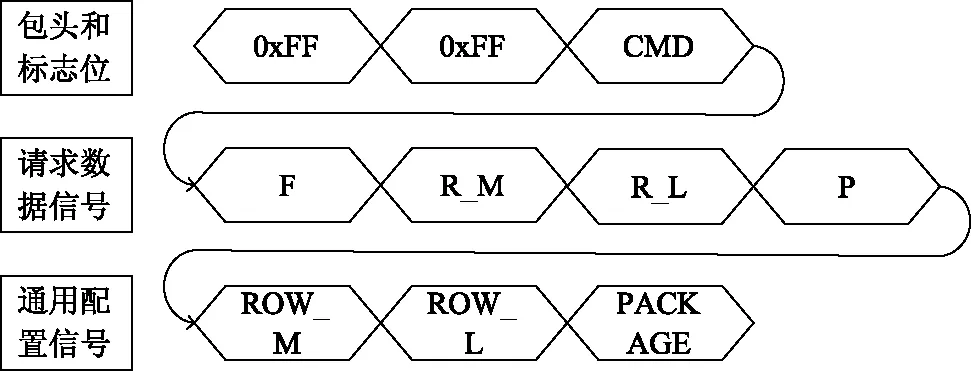

1.4 命令格式

上位机与DDR3核心控制模块通信命令格式如图4所示。第1、2字节包头固定为FF、FF,检验命令有效,第3字节CMD为命令标志信号,判断命令类型:0x00为数据请求,0x0A为差错重传,0x0B为通用配置。第4字节F为请求数据时的帧数,第5、6字节R_H、R_L(H代表高位,L代表低位)为请求数据时的行数,第7字节P代表请求数据时的包数。第8、9字节ROW_H、ROW_L为通用配置时一帧图像总的行数,第10字节PACKAGE为通用配置一行总包数[7]。

图4 命令格式

2 关键技术

2.1 高速缓存的分支预测设计

DDR3核心控制模块读出数据流程:上位机发送数据请求命令,该核心对命令解码,切换到读出状态,数据写入读缓冲区,经数据同步模块和传输接口输出到上位机。流水线操作使上位机从发出命令到接收数据的响应时间过长,因此采用分支预测设计实现数据高速缓存和即时响应[8]。

分支指的是顺序读出数据和差错重传读出数据。与中央处理器(Central Processing Unit,CPU)分支预测不同,该分支概率集中在顺序读取状态,触发错误重传概率低,测试平均出错概率为5%,为节省电路面积,不采用动态分支预测管理,固定将分支预测为顺序读出数据。

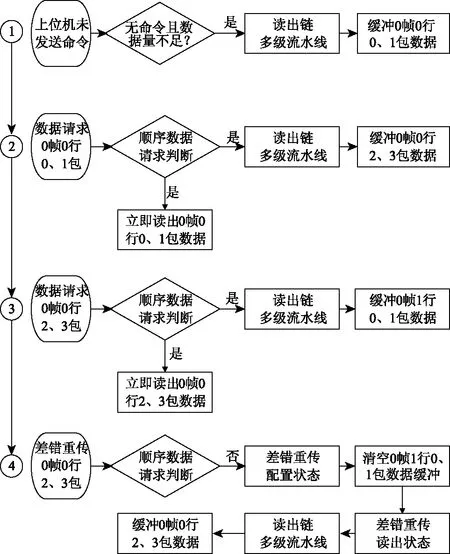

图5为分支预测设计示意图,编号①、②、③、④为上位机依次发出的4条命令,即4次流水线过程。①、②、③为顺序读出,命令到达后立即从缓冲区读出数据,且②读出的数据在①过程提前缓存;④命令触发差错重传,流水线冲刷并临时执行一次完整的读出流程。

图5 分支预测设计示意图

2.2 可配置的通用性设计

CIS改变分辨率或更换CIS时,需修改存储核心的存储格式。若采用修改源代码,烧录到FPGA的方式,效率低且不利于保持连续两种状态拍摄的对照环境。本文提出一种通用配置方法,上位机发送配置命令,DDR3存储核心在运行过程中任意时刻中断执行,在线配置,完成后正常运行。

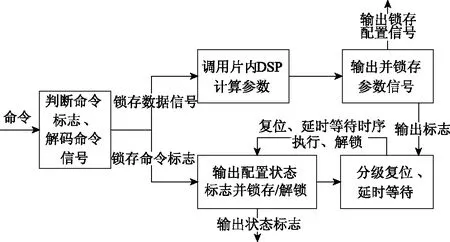

图6为通用配置流程图,上位机发送配置命令,解码模块判断是否为两次相同命令且CMD是否为0x0B,若是,解码第8~12字节的配置信号,通用配置模块锁存解码信号并输出到计算模块,计算模块调用片内DSP计算参数;同时输出命令标志到图3所示状态机,进入通用配置状态,触发分级复位延时等待,退出通用配置状态后,解锁上述模块,发送握手信号到跨时钟域同步模块,反馈到上位机,则配置完成且各级模块恢复运行。

图6 通用配置流程图

2.3 低功耗设计

低功耗设计两个优化方法为解码模块选择性触发、帧率匹配。

解码模块选择性触发的判断条件:上位机发送数据请求命令(0x00)时,帧、行、包信号递增。进入解码模块前判断前后命令是否一致,若不一致,判断为数据请求命令,命令不解码;若前后命令一致,且为配置命令(0x0A、0x0B),则触发解码过程。选择性触发解码模块可防止解码操作干扰有规律的读写操作,降低解码模块的计算和配置等功耗[9]。

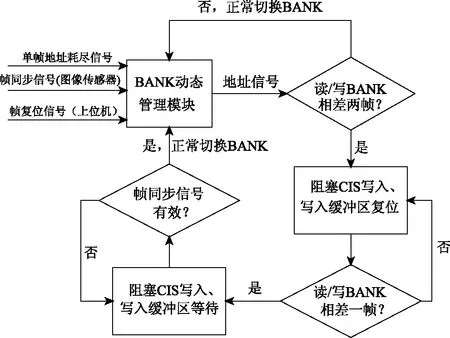

帧率匹配模块通过图7所示的判断逻辑,若写和读地址相差两个BANK,触发分级复位、延时等待流程,根据BANK地址信号和帧同步信号决定复位和使能的切换节点,保证开始写入DDR3数据为下一帧图像的第一个数据。

图7 帧间速率匹配流程图

帧率匹配是在BANK(帧)动态管理的基础上降低CIS端写入DDR3的速率,使其等于慢速的上位机端读出DDR3的速率,以兼容带宽低的上位机,保证显示图像的实时性和连续性。选择性的复位、阻塞CIS端写入DDR3,而不是持续写入并刷新DDR3,降低了写入链功耗。

3 实验验证及分析

3.1 系统运行效果验证及分析

高动态图像传感器的存储设计,基础功能是准确还原CIS采集的图像。图8(a)为系统效果图,图8(b)为反向拍摄的印刷电路板(PCB)及板上部件。测试系统由KEITHLEY公司的2450型号源表供电,并实时测量电源的电流波动;搭载联合光科(60017)镜头的系统板卡固定位置实时采集图像;电脑运行上位机,实时接收并显示图像;拍摄环境为风扇和黑色背景板。

图8 测试系统

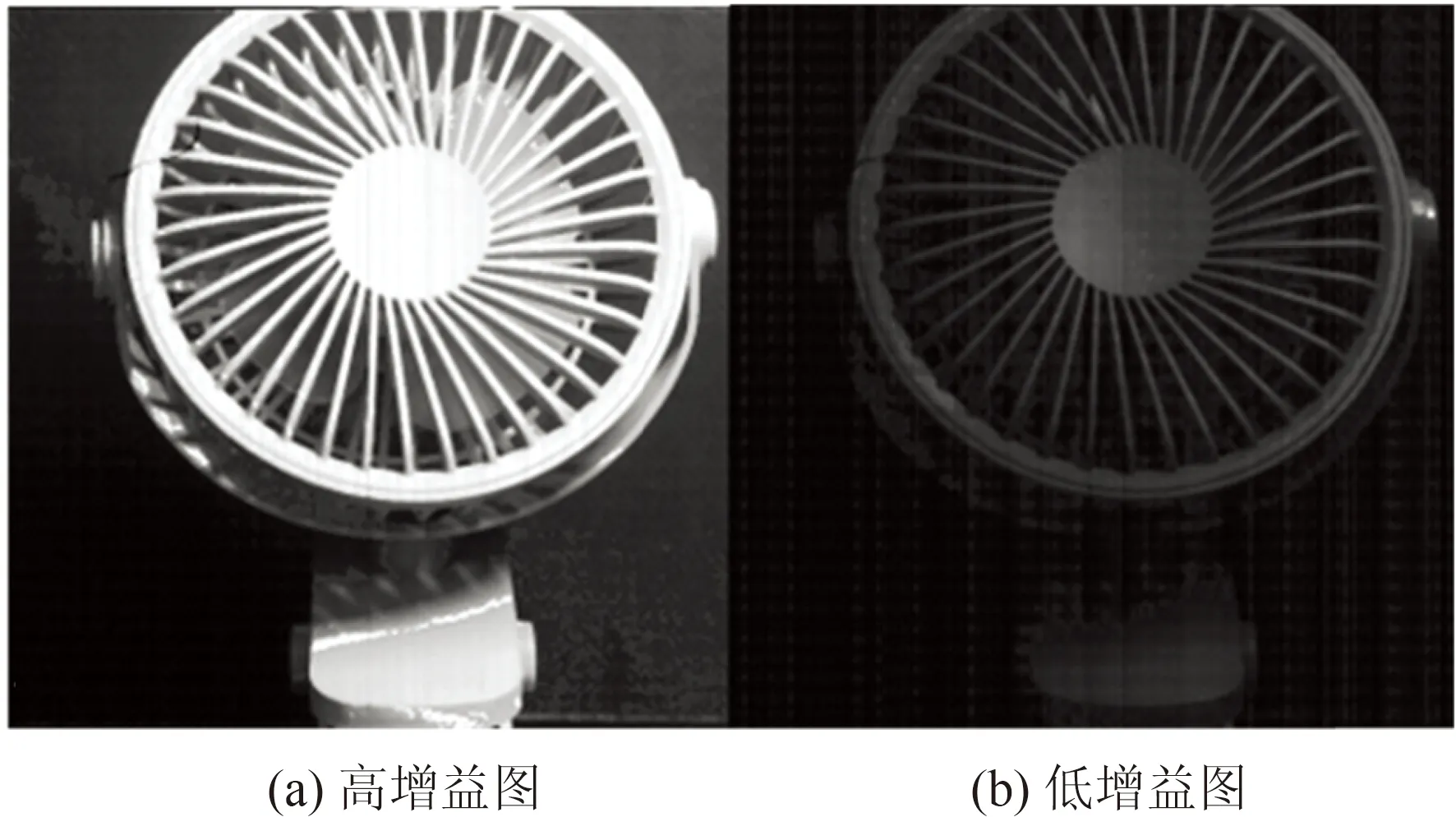

图9是通过DDR3存储核心管控数据流输出并实时显示的图像。高、低增益两幅图准确还原了风扇,证明数据流管控准确稳定。

图9 实时显示图像

3.2 分支预测的高速性能验证及分析

分支预测的高速性能测试基于上述系统测试环境。测试的对照条件为是/否采用分支预测设计,表现为是/否每一条上位机命令都经过解码、计算、映射、同步、读出的流水线操作。采用分支预测设计的测试:上位机总是发送数据请求命令,若为连续且不同的命令,直接从缓冲区读出;反之则触发解码模块,执行一遍完整的读出流程。未采用分支预测设计的测试:上位机发送数据请求命令,每次都需要执行一遍完整的读出流程。分支预测对于上位机读出速度的测试结果如表2所示,可以看出,分支预测设计对于上位机的读出速度提升了115倍。理论分析该情况,DDR3接口的理论带宽为12.5 Gbps[10],该测试结果的速度受慢速上位机制约,在上位机速度达到12.5 Gbps之前,是/否采用分支预测设计,对上位机的读出速度同样应提升115倍。

3.3 低功耗设计验证及分析

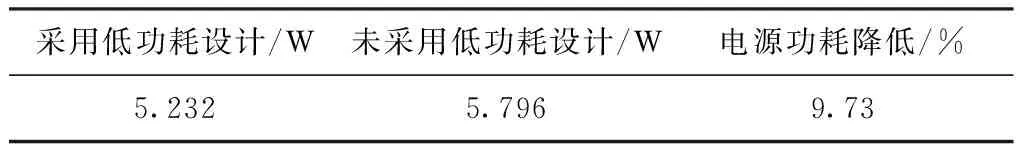

低功耗设计的测试基于上述系统测试环境。该测试的对照条件为是/否采用选择性触发解码,即分支预测,和帧率匹配。测试时多次上电,稳定运行后通过源表测出平均电流值,乘恒压12 V计算得到平均的电源功耗,测试结果如表3所示,低功耗设计使整体电源功耗降低0.564 W,降低比例为9.73%。理论分析该情况,整体电源功耗除了DDR3芯片及其核心控制模块,还包括了CIS运行功耗、传输接口等部分功耗,实际对于DDR3整体的功耗优化应超过9.73%。

表3 电源功耗测试表

3.4 通用配置验证及分析

通用配置的参数无法从外部观测到实际效果,因此通用配置设计的验证采用Xilinx的ILA工具,测试仍基于上述系统测试环境。

通过上位机发送配置命令为“FF_FF_0B_00_00_00_00_01_11_03”,判断CMD标志为0x0B,一帧图像总行数Trow为“01 11”,一行总的数据包Tpack的个数为“03”,理论计算该16进制的配置信息计算公式为

因此,理论上一帧图像大小的地址空间应配置为422 604。图10是实际测试的ILA截图,在红线触发时刻,一帧图像的地址空间从默认的1 056 768配置为422 604,且配置完成后正常运行。

图10 地址空间配置截图

4 结 语

本文提出一种高速低功耗通用图像缓存设计,测试系统实时显示的图像证明了数据流控制准确,系统结构稳定。设计提出三个关键技术:分支预测;帧率匹配、优化解码;通用配置。实际验证上位机读取速度提升115倍,电源功耗降低9.73%,在线配置存储格式准确。该设计为高动态CMOS图像传感器的数据流管控和缓存设计提供了可靠的解决方案,并且已经得到了实际应用。该设计可封装为数字IP,并应用在更高带宽的系统结构中,在数据流缓存稳定的情况下,可获得更为高速的数据率。