3D电子封装侧壁布线的互连界面处理工艺研究

杨繁,吴蕴雯,高立明,张文龙,李明

(上海交通大学材料科学与工程学院,上海 200240)

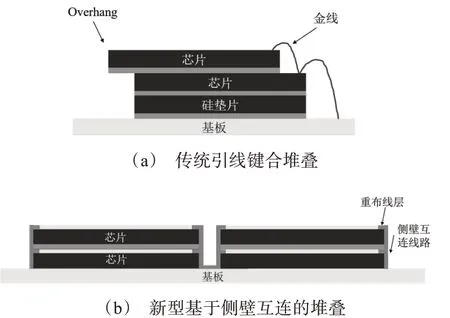

半个世纪以来,集成电路工艺技术不断进步,遵循摩尔定律朝小型化,轻薄化,高性能和多功能化方向持续发展。然而,晶体管的特征尺寸目前已逐渐趋近物理极限,通过缩小晶体管尺寸提升芯片的集成度变得越来越困难。由于3D电子封装技术可以进一步提高封装密度,实现系统化集成,因此受到了极大的关注。在众多3D封装形式中,叠层型3D封装体积小,功耗小并且对不同类型芯片兼容性高,具有显著优势[1]。目前主流的芯片叠层工艺有两种:硅通孔(TSV)[2]和引线键合(WB)[3]。二者对比,TSV技术集成度高,但制程涉及前道工艺,成本高,投入大。WB技术成熟,且与传统封装制程兼容度高,开发容易,但互连密度受到键合工艺限制。多年来,金线直径难以突破15 μm,相应的焊盘间距也未能降低到75 μm以下。近年,又一种基于芯片侧壁布线实现上下层互连的3D封装新技术得到了发展[4-7]。图1对比了这种侧壁布线和WB两种堆叠结构。该封装形式不仅与传统WB封装制程具有很好的兼容性,而且相比WB堆叠具有明显优势:1)上部芯片不需要Overhang,堆叠底层不需要裸硅垫片,空间利用率更高;2)侧壁线路使用图形化工艺制做,密度更高。

图1 对比金线键合和侧面布线两种互连形式Fig.1 Comparison of WB stacking and sidewall in‐terconnect stacking structures

早在1992年,IBM[8]和Irvine Sense[9-11]已开发出基于侧壁布线的T-connect工艺,但该工艺涉及硅刻蚀和介电材料沉积工艺,一般封装厂难以实现。2012年前后,Kim等[12-13]在晶圆设计和图形化工艺上做出改良,将介电材料在晶圆制造阶段填入切割道,在晶圆减薄和切割后,芯片侧壁已存在布线所需的介电材料,封装阶段不涉及前道工艺,工艺路线更为合理。Infineon于2020年发布了基于侧壁布线的芯 片尺 寸封 装技 术(chip scale package)[14],相比TSV工艺,该技术将电路经由侧壁引到芯片背面,避开了成本高昂的硅刻蚀。除了晶圆设计和芯片堆叠,侧壁布线需解决的核心问题是在堆叠体的侧面制作线路。Cubic Memory公司使用喷墨打印导电树脂的方式制作线路[15];Kim Sun-Rak等使用图形化蒸镀[12-13],研发提出了一种先在载体上制作线路,再键合到侧面的方法[16];学术界还有使用激光加工对物理气相沉积(PVD)镀层进行减法操作来制作侧壁线路的方法[17-18],以及使用特殊的掩模版进行侧壁光刻的工艺[19]。一般先制作出芯片的重新布线层(RDL)端头,再制作侧壁互连线路,但RDL端头的铜氧化膜会影响互连界面的导通性[20]。塑封前的芯片不适合湿法清洗去除氧化膜,优先选择干法工艺。一般认为干法清洁通过对表面进行溅射刻蚀去除氧化膜,方向性强,对侧壁清洁能力弱,故侧壁互连界面氧化膜去除存在一定难度,在这方面已发表的学术研究也比较少。对此本研究基于离子轰击的物理方法探索了侧壁互连界面氧化膜的去除工艺,并借助高分辨透射电镜观察、小角度X射线衍射及纳米束电子衍射分析等手段对侧壁互连界面氧化膜的去除机制进行了深入解析。

1 实验与表征

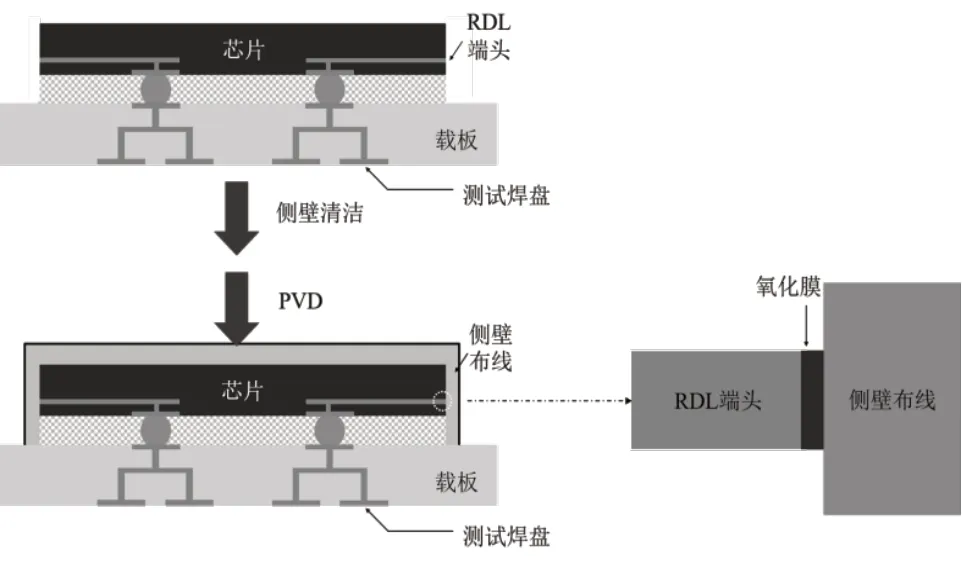

研究中所用的样品结构示意图如图2左侧所示,画圈处为芯片RDL端头与侧壁布线接触位置,芯片RDL端头暴露在芯片侧壁,并且RDL经锡球与基板表面的测试焊盘(Pad)导通,Pad上电镀镍金防氧化层。对样品首先进行了烘烤除湿处理,条件为120℃,9 h,N2保护(99.9%工业纯)。烘烤后的芯片使用离子轰击进行表面处理(激发功率:200 W,压力:13.3 Pa,气体流量:35 SCCM,时间:110 s,工作气体:氧气及氩气)。改变处理条件进行了三组实验:未处理、氧离子轰击处理以及氩离子轰击处理(见表1)。处理后的样品立刻用PVD法制作金属导电层,沉积时样品的基板面使用紫外光敏性胶带进行保护。PVD之后去除胶带,此时芯片侧壁上的RDL端头之间借助PVD镀层导通。使用万用表(是德科技,型号34470A)在基板的焊盘处(见图2左侧中标注)量测RDL端头和侧壁布线之间的接触电阻(Rcont)。

图2 样品结构和实验步骤示意图(左)以及RDL端头与侧壁布线的互连界面示意图(右)Fig.2 Structure of the sample and procedures of the exper‐iment(left)and the interface of the RDL edge and the sidewall interconnect(right)

烘烤过程中,保护气氛中极微量的氧气会氧化线路端头表面,在互连界面形成大约20 nm的氧化膜,如图2右侧的示意图所示。实验对处理前后的氧化膜电阻,成分和结构进行了表征。电阻量测采用的是四探针法,氧化膜成分、结构的表征采用高分辨透射电镜(HR-TEM,型号FEI Talos 200X,200 KV,1.5 nA),纳米束电子衍射(NBD),X射线能谱(EDS)以及小角度掠射X射线衍射(GA-XRD)。使用公式ρ=RcontA/L计算电阻率(其中:ρ为电阻率,Rcont为接触电阻值;A为接触面的面积,25 μm×250 μm;L为氧化膜厚度),氧化膜厚度由TEM表征获取。由于氧化膜为混合物,因此计算的电阻率为该层物质平均电阻率。

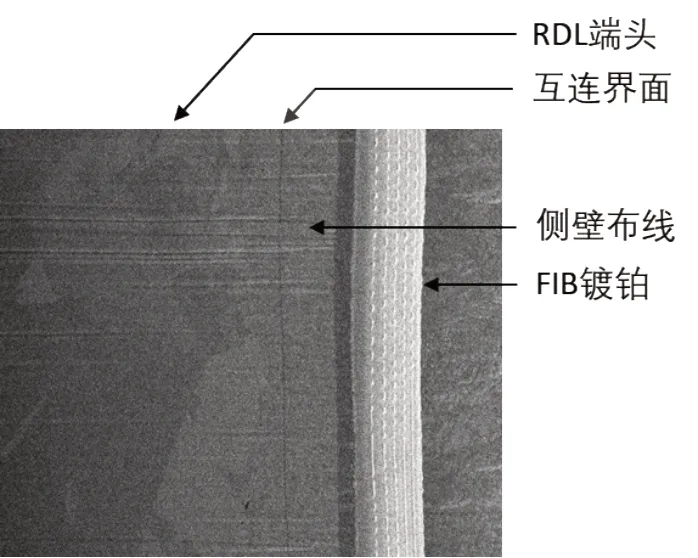

TEM制样使用了聚焦离子束(FIB)加工。图3是FIB所制做样品的扫描电镜照片,图中标出了RDL端头和侧壁布线之间的互连界面(包括氧化膜)位置。切片被FIB减薄至100 nm厚度,然后使用HR-TEM观察氧化膜截面,并采集氧化膜的EDS和NBD谱图。由于测试芯片的尺寸太小,因此在镀铜玻璃片上做GA-XRD表征。镀铜玻璃片与同组芯片一同经过除湿和离子轰击处理后立刻使用GAXRD采集其极表层的氧化物衍射光谱,离子轰击时镀铜玻璃片在腔室内保持侧向直立。

图3 使用聚焦离子束制做的TEM样品Fig.3 TEM sample prepared by FIB

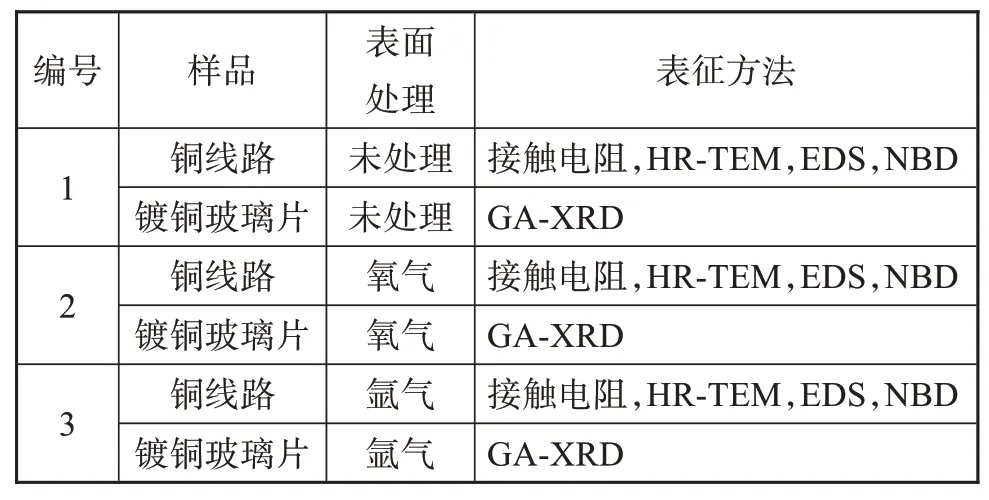

表1总结了该研究的实验设计和每个实验所进行的表征。三组实验分别为未处理的对照组,氧离子及氩离子轰击组。后两组除了工作气体不同,其他工艺参数完全相同。

表1 离子轰击表面处理实验设计Tab.1 Experimental design of ion bombardment surface treatment

2 结果与讨论

2.1 互连界面接触电阻

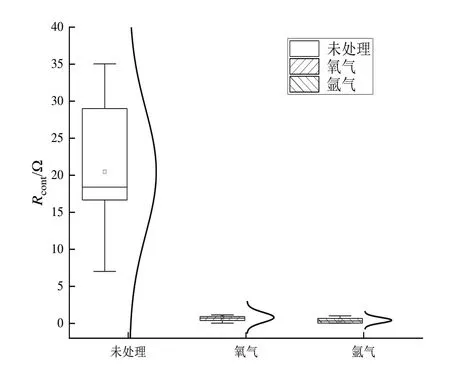

图4为三组实验(未处理,氧离子及氩离子处理)的接触电阻(Rcont)量测结果。对照组样品在PVD之前就存在肉眼可见的氧化现象,PVD后接触电阻值大约为20 Ω左右。两个测试组先进行离子轰击,再PVD镀膜,接触电阻基本分布在0.1~1.0 Ω之间,比对照组低1~2个数量级。因此确认离子轰击可大幅降低接触电阻。

图4 接触电阻量测结果Fig.4 Contact resistance measurement results

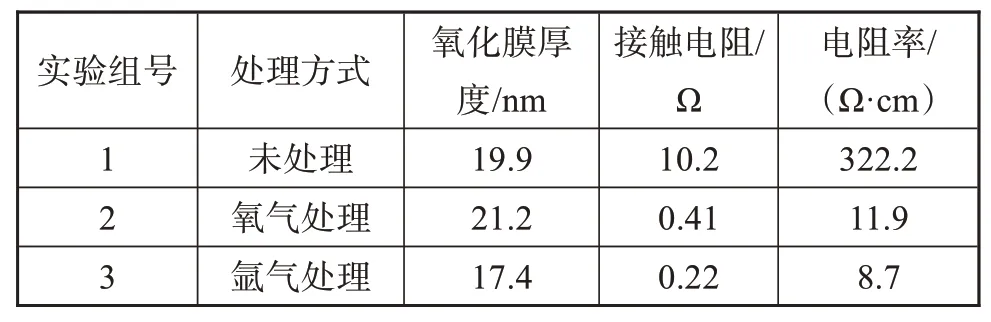

从每一组样品中抽取一个制作TEM样品,在TEM表征中测量氧化膜厚度,并且计算平均电阻率,结果如表2所示。由于每次量测电阻的回路中包含两层氧化膜(芯片内电路示意图见图2左侧),表2中的电阻值已经做了减半处理。三组样品的氧化物厚度相近,但未处理的样品平均电阻率为322.2 Ω·cm,该数值为典型的热氧化形成的铜氧化物电阻率[21-23]。另外两组样品尽管电阻率大幅降低,但是透射电镜下观察氧化物厚度未发生明显下降。使用氩气处理的样品接触界面电阻率最低,但比较特殊的是具有氧化性的氧离子轰击处理之后的样品氧化膜电阻率也大幅下降。

表2 平均接触电阻值和氧化膜电阻率计算结果Tab.2 Calculation results of average contact resistance and resistivity of oxide film

2.2 互连界面观察及成分分析

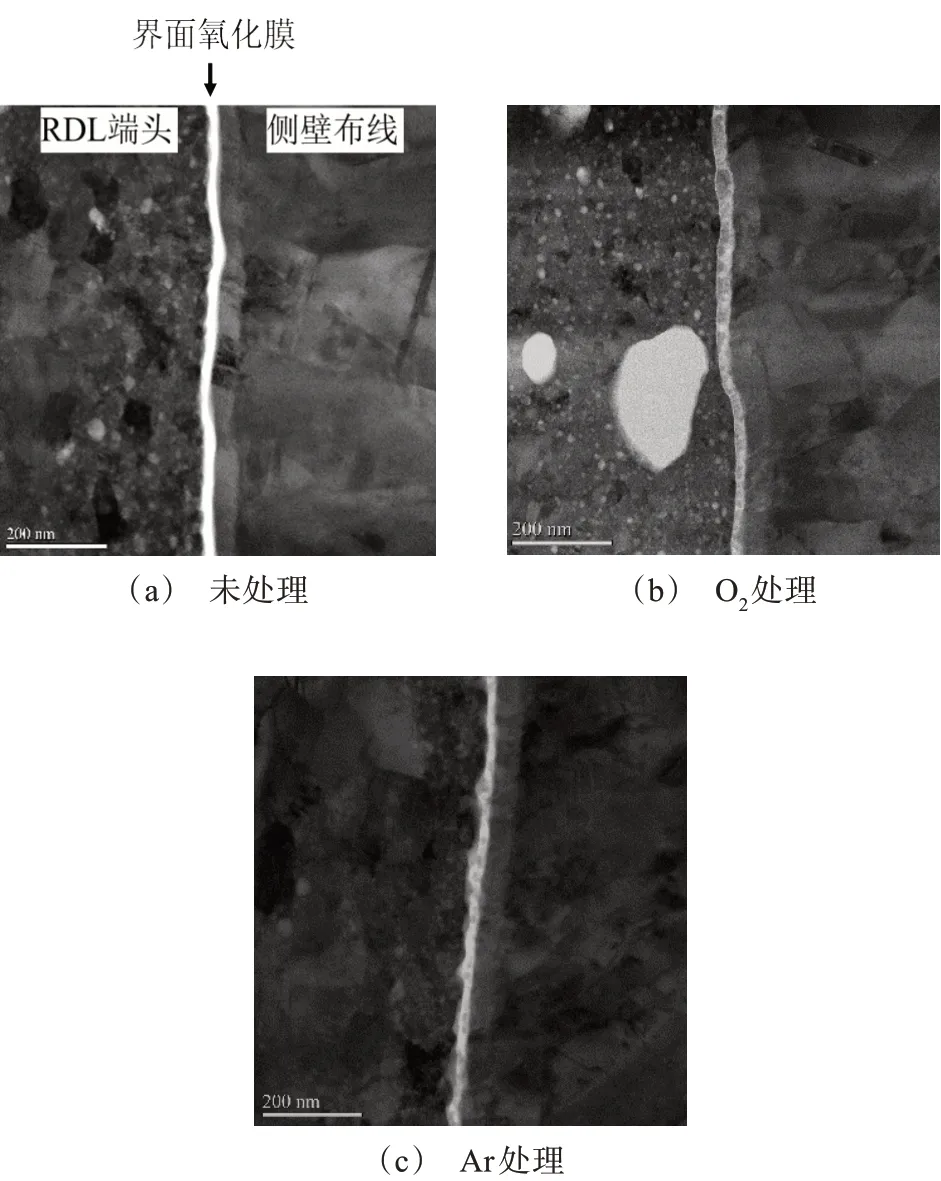

在切片界面氧化物位置拍摄了TEM图像。图5中标注了夹在PVD镀层和RDL端头间的氧化膜。在TEM明场模式下,氧化物比金属亮。在未处理的样品中可明显看到一条大约20 nm宽的白色条带,为铜的氧化膜。离子轰击处理后的两个样品中也可以观察到氧化膜,但处理过的样品氧化膜内部分布有细小的黑色斑块,其在后续的NBD表征中被标定为金属铜。三个样品的氧化物膜厚度介于17~21 nm之间(见表2),后两个样品在离子轰击处理中氧化膜未被刻蚀。2007年Wang等团队[24]发表了氧化物在氩气等离子体处理中被还原为金属的理论[24-26],并观察到这种还原反应的转化率存在上限,依据该理论可知氩离子轰击后氧化膜内铜晶粒为还原产物。氩气为惰性气体,但氧气化学性质活泼,目前学术界对氧离子轰击是否也能产生还原效果的研究较少。

图5 样品横截面的TEM图Fig.5 TEM images of the interface layers

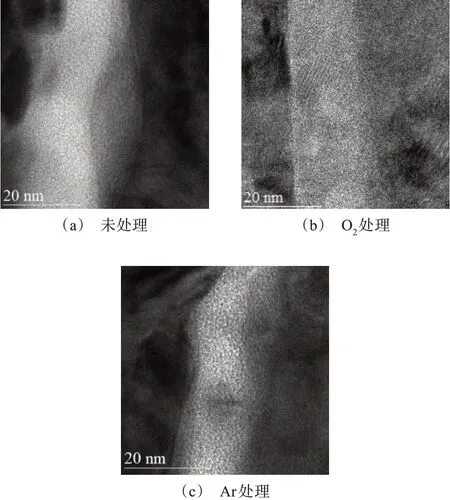

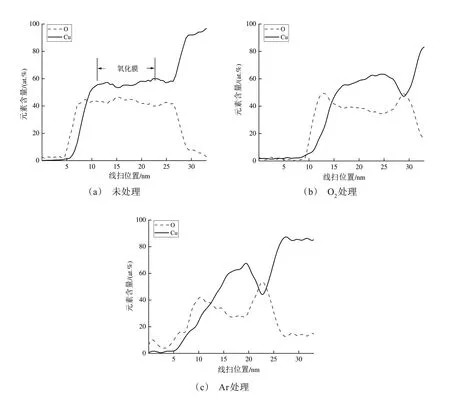

图6和图7是氧化物的HR-TEM照片和EDS线扫原子比分析结果,EDS线扫方向为从侧壁布线(左侧)至RDL(右侧)穿过界面氧化膜。

图6 界面氧化膜的高分辨电镜成像Fig.6 HR-TEM images of the interface layers

图6(b)和(c)中两个样品在氧化膜的黑色斑块内部存在晶格条纹。晶格条纹的间距分别为0.205和0.216 nm,接近铜的(111)晶面间距,佐证了TEM下的黑色斑块为金属铜晶粒。图6中未处理样品的氧化膜内部未出现晶格条纹,并且处理过的样品氧化膜在铜晶粒之外的区域也不存在晶格条纹,故烘烤过程中形成了非晶相的铜氧化物,后续的离子轰击处理使部分非晶相的氧化物被还原为晶相的铜。在图7的EDS线扫结果中,根据氧元素的原子百分比可确定氧化膜在线扫结果中的位置,截取线扫结果中氧化膜的横向中点分析,三个样品氧化膜的铜氧比为1.17、1.56和1.85。虽然从成分上无法分辨氧化铜、氧化亚铜和铜三种物质。但未处理的样品氧化膜铜氧比显著低于处理后的样品,相对而言氧气和氩气处理的两个样品之间铜氧比差异较小。

图7 氧化膜切片EDS线扫图(从左到右结构依次为侧壁布线→氧化膜→RDL)Fig.7 EDS line scan of oxide layers(the structure from left to right is sidewall intercon‐nect→oxide layer→RDL)

图8为氧化膜的纳米束电子衍射花样,束斑直径为10 nm。图8(a)中未出现明显的斑点,氧化膜物质为非晶相。图8(b)和(c)的选区为氧化膜中的黑色晶体颗粒,即图中圈出位置。图中分散在氧化膜中的大部分晶体颗粒的直径小于束斑直径,NBD无法获得整套的衍射斑点。图8(b)和(c)为明显的晶体衍射花样,标定结果符合铜的衍射花样。其中图8(c)标定为铜<013>晶带轴衍射花样,图8(b)中花样未能确认晶带轴但依据衍射斑点对应的晶面间距可标定为铜的衍射花样。

图8 氧化膜的NBD花样(光斑位置由虚线圈出)Fig.8 NBD pattern of the oxide layer(spot position is circled by dotted line)

2.3 GA-XRD衍射表征镀铜玻璃片样品.

图9为镀铜玻璃片样品的GA-XRD谱图,入射角度为0.1°,穿透深度在25 nm以下[27]。其中,氧化后未做表面处理的样品的谱图中未出现任何晶相衍射峰,只有一个宽的非晶相峰。而两个处理后的样品的谱图中除了非晶相峰,还有金属铜的峰。GAXRD结果说明镀铜玻璃片表面也产生非晶相氧化物,且0.1°X射线掠射无法穿透该氧化膜。离子轰击后其表面也产生金属铜,呈现出金属铜与非晶相氧化物的混合相。GA-XRD结果与TEM表征结果一致,均显示未处理的氧化膜与处理后的样品在成分和结构上有显著差异,而且氧离子处理和氩离子处理后的氧化膜成分和结构相似。

图9 镀铜玻璃片表面的小角度掠射X射线衍射表征Fig.9 GA-XRD spectra of the Cu on glass samples

2.4 处理结果和处理机理的讨论。

图5和图6的TEM图像中铜的晶相颗粒分布较为密集且有的互相接触,具有形成贯穿20 nm氧化膜导电通道的条件,导电通道使接触电阻大幅降低。考虑到工业生产中铜线路表面自然氧化膜厚度通常低于5 nm[20],本研究可解决一般侧壁布线工艺的表面清洁需求。

对比未处理的样品和氩气处理的两个样品表征结果并结合文献理论[24-26]得出,氩离子轰击使氧化膜发生还原反应生成金属。而对比氧气处理和氩气处理的两个样品表征结果发现,二者在成份和结构上非常相似,足以证明氧离子轰击也具有还原作用。一般认为等离子体的还原剂为自由电子,但本研究前期探索时曾使用没有离子轰击效果的等离子体清洁设备(PE设备)处理样品,但在PE设备上处理无法降低接触电阻,据此认为除自由电子之外,离子轰击也是该还原反应的必要条件。综合分析得到如下还原机理:如图10所示,电子被氧化膜吸收,并与带正电的铜离子结合。但自由电子无法提供足够的能量使离子脱离表面。氧化膜晶格吸收电子后,内部铜氧之间的结合力下降。较轻的氧原子可以吸收离子轰击的能量成为气态,并被真空系统抽走。铜原子与基体结合力强,离子侧向轰击的能量不足以溅射铜原子,铜原子富集形成纳米晶粒。结果离子轰击整体表现为氧原子被选择性刻蚀,产生了还原效应。

图10 离子轰击还原机理示意图Fig.10 Illustration of the plasma reduction mechanism

实验中发现,离子的物理轰击效果起主导作用,即使工作气体为氧气也具有还原能力。但实验2和实验3中的两种气体分子量相近,二者对比,后者的电阻率更低,EDS分析中后者氧化膜的氧含量更低,说明尽管气体离子主要起到物理轰击作用,但氧气本身的氧化性使其处理效果低于氩气。

3 结论

本研究针对侧壁布线3D封装中现有工艺存在的互连界面导电性差的问题,采用离子轰击处理手段,较系统地研究了侧壁清洁降低互连界面接触电阻的工艺,并通过微观解析,探讨了离子轰击大幅降低互连界面电阻的内在机制。本研究主要结论如下:

(1)离子轰击处理可将位于侧壁的互连界面接触电阻降低1~2个数量级,是有效的氧化膜清洁处理手段。

(2)离子轰击前后对比氧化膜的厚度未发生改变,但处理后氧化膜内部产生密集分布的铜晶粒,尺寸在5~10 nm之间,证明接触电阻大幅降低是源于氧化膜中密集铜晶粒存在,且互相接触形成贯穿的导电通道所致。

(3)结合理论分析进一步研究表明,离子轰击处理后的氧化膜中出现铜晶粒是由于氧化膜在处理过程中铜离子被还原,即氧化膜氧离子在离子轰击下吸收能量,成为气态,而铜离子吸收电子后被还原成铜原子,并聚集形成晶粒。