基于FPGA的图像双边滤波器系统设计

严 飞,陈佳宇,张华西,刘银萍,刘 佳

(1.南京信息工程大学自动化学院,江苏南京 210044;2.南京信息工程大学大气物理学院,江苏南京 210044;3.江苏省大气环境与装备技术协同创新中心,江苏南京 210044)

0 引言

数字图像在传输或者采集的过程中,会因为传输接口、传输距离、传输环境等因素引入各种不同的噪声[1]。噪声带来的误差会累计传递,因此需要对数字图像进行去噪,方便后期应用。常用的图像去噪方式有均值滤波、中值滤波以及高斯滤波等[2-5]。图像存在的噪声大多数为高斯噪声,所以高斯滤波在图像去噪中应用广泛。而高斯滤波只考虑了像素点空间分布,没有考虑到像素值的差异,会将图像边缘模糊。在1998年,文献[6]在高斯滤波算法的基础上提出了双边滤波算法。双边滤波区别于高斯滤波,它在去除噪声的同时可以使图像边缘保持清晰[7]。双边滤波等算法需要经过大量的计算,在许多实时性要求比较高的场合采用传统ARM、DSP等串行架构处理器进行处理难以保证实时性。文献[8-9]采用GPU对算法实现硬件加速,但是GPU功耗太大,不利于嵌入式场景。

从图像去噪实时性与低功耗为目的出发,从20世纪90年代开始,国外陆续有学者将FPGA用于图像传输[10-13]。到21世纪初,使用者对于视频图像画面质量的要求不断提高,催促视频技术的飞速发展[14]。在国内,文献[15-17]开始研究使用FPGA对图像做预处理。近年来,文献[18]采用FPGA对双边滤波进行设计,未对算法进行优化。文献[19]将双边滤波值域核算法进行拆分,对算法进行加速的同时,减少了值域核计算资源浪费。

本文深入研究了双边滤波算法[20],对算法中的空域核计算部分进行剪枝并使用离散化[21]采样方法对值域核进行计算。因传统3×3卷积核覆盖像素特征点范围小,本文综合计算量考虑后用5×3卷积核设计了基于FPGA的图像双边滤波系统[22]。实验结果表明该系统在保证图像去噪快速性的同时,去噪质量也得到保证。

1 系统设计

本设计采用的FPGA芯片是SPARTAN-7系列XC-7S50FGGA484-1,主要用来接收图像、处理图像以及驱动显示器实时输出显示。

图1为Verilog程序模块框图,系统的工作流程分为如下几个步骤:上位机通过串口将图片为RGB888格式数据发送给FPGA,FPGA接收图片数据并拼接完成后经过FIFO缓存器存放于DDR3存储器。待接收完整幅图片数据后,FPGA将数据从DDR3存储器中循环读出[23],经过FIFO缓存器给双边滤波模块进行处理。双边滤波模块处理数据并实时输出,最后生成视频时序并将数据依照视频显示时序同时经过TMDS编码模块实时HDMI输出显示。

图1 Verilog程序模块框图

本图像双边滤波系统采用了参数化的设计方式,可以支持任意分辨率的图像滤波处理。本次使用800×600分辨率图像对双边滤波系统进行实现。

2 数据接收预处理

前期采用Matlab将24位BMP图像转化为RGB888格式,通过上位机进行传输。上位机依次传输8 bit数据,在FPGA端接收3次8 bit数据拼接为单个像素点数据。每次接收完8 bit数据时拉高一个时钟Rx_done完成信号,接下来用Rx_done信号对接收数据进行打拍操作,对数据拼接。

与其他的滤波原理一样,双边滤波所采用的是加权平均的方法。对周边领域像素点的亮度值加权平均来表示像素点的强度。考虑到滤波处理时数据循环从DDR中读取,因此在存储数据时将RGB888格式的图像数据信息转化为YCbCr格式,为最后经过双边滤波模块处理时减少数据量与时钟延时。

RGB转换为YCbCr的公式如下:

Y=0.29R+0.587G+0.114B

(1)

Cb=-0.172R+0.511B+128

(2)

Cr=0.511R-0.428G-0.083B+128

(3)

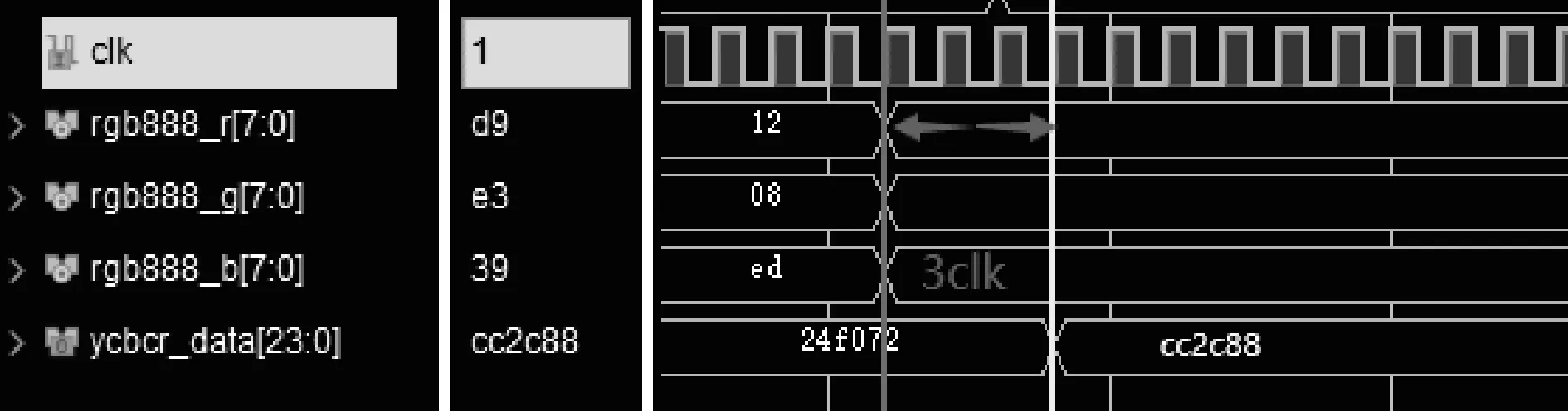

图2为RGB转YCbCr仿真图,本设计在FPGA内部采用流水线的设计思想对YCbCr进行计算。分3步进行,分别是乘法、加减法与除法。只需3个时钟周期便可输出结果。由于FPGA不适合进行浮点数的运算。所以在对数据进行计算时,将所有数据进行左移8位扩大256倍进行计算,在最终的计算结果右移8位进行结果输出。最小化减少计算过程中数据的精度损失。

图2 RGB转YCbCr仿真图

3 双边滤波模块设计

3.1 双边滤波算法原理

双边滤波算法于1988年由文献[6]基于高斯滤波方法提出。传统的高斯滤波方法直接将高斯权重系数与图像信息直接做卷积运算,只考虑了像素点间的空间距离关系,得到的图像不清晰。双边滤波算法将高斯滤波权系数优化成高斯函数和图像亮度信息的乘积,优化后的权系数再与图像信息作卷积运算,这样就考虑到了像素点间的相似程度,使得到的图像边缘更加平滑。此方法对于彩色和灰度图像的滤波均适用,具有很强的实用性。

双边滤波的公式为

(4)

(5)

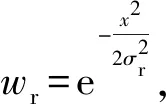

在本设计中分别用ws与wr表示空间域核二维高斯滤波函数Gσs和图像像素值域核Gσr,其计算公式为:

(6)

(7)

式中:I(i,j)与I(m,n)分别为中心点与滑动窗口中某个点像素亮度值;σs为空域标准差;σr为值域标准差。

σs和σr均是已知的权重值,而i,j,m,n都是需要在窗口中遍历确定的值。

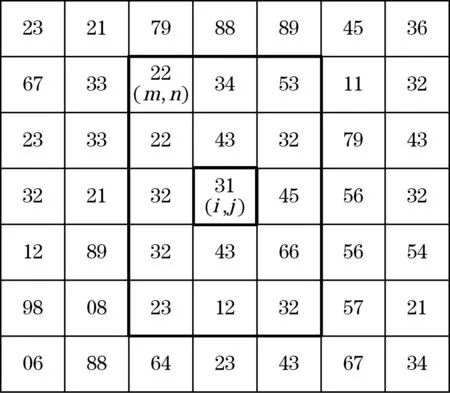

图3为本系统设计选用的5×3滑动窗口,它相比于传统3×3与5×5窗口,获得的特征像素点多,计算量适中。其中(i,j)为窗口的中心点坐标值,(m,n)为滑动窗口中的某个点坐标值。

图3 5×3滑动窗口

在ws的计算中,ws只与σs和所选取的矩阵有关,当两者都给定后,ws便是固定值。而wr所反映的是像素范围域的辐射差异(例如卷积核中像素域中心像素之间相似程度、颜色深度、深度距离等),因此wr不仅与σr选取有关,而且还与滑动窗口中心点周围像素点有关。

3.2 双边滤波算法硬件加速实现

区别于传统设计方式将式(6)结果存入ROM,本文在对双边滤波模块进行设计时确定好σs,采用Matlab计算出ws值,由于浮点数不利于FPGA计算,因此将结果值扩大211(2 048)倍取整变为12位数据直接进行赋值并在最终结果去掉低11位。可以节省FPGA内部存储资源,减少计算带来的时钟延时。

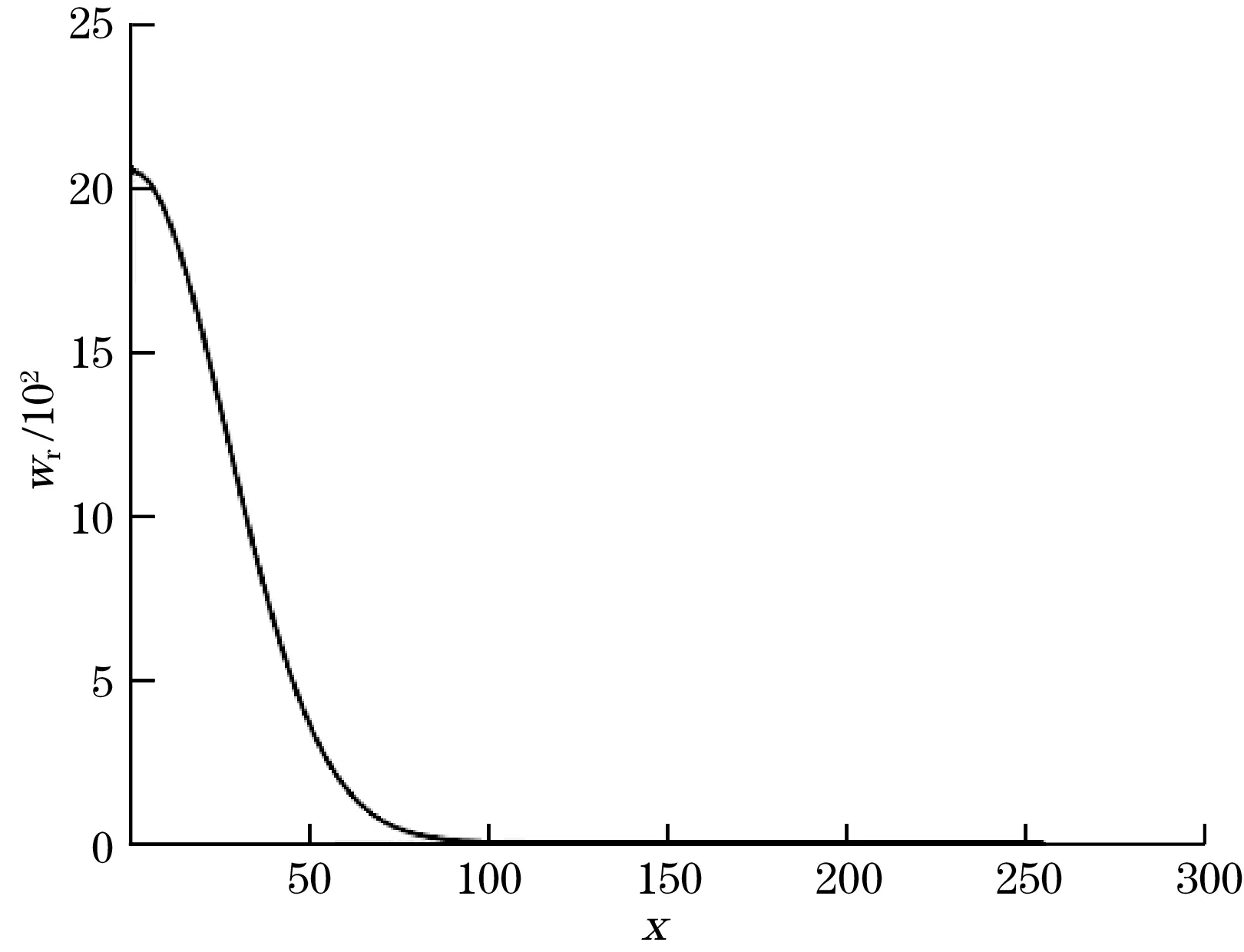

wr=2 048ax2,x∈[0,255]

(8)

如图4所示,采用Matlab绘制出该函数曲线,对该曲线离散化,在x轴对其进行255次等间隔采样,抽取纵坐标值取整进行存储作为wr近似计算结果,存入FPGA内部8位查找表中进行计算。

图4 函数曲线图

本文对该算法进行优化后,将值域核部分直接缩减为一个8位查找表结果输出。相比于以往的16位查找表,使用的存储资源缩减为原来的1/256,相比于4个8位查找表输出结果相乘,存储资源缩减为原来的1/4,同时省去了查找表后进行乘法运算的步骤,对算法进行加速,减少了资源浪费。

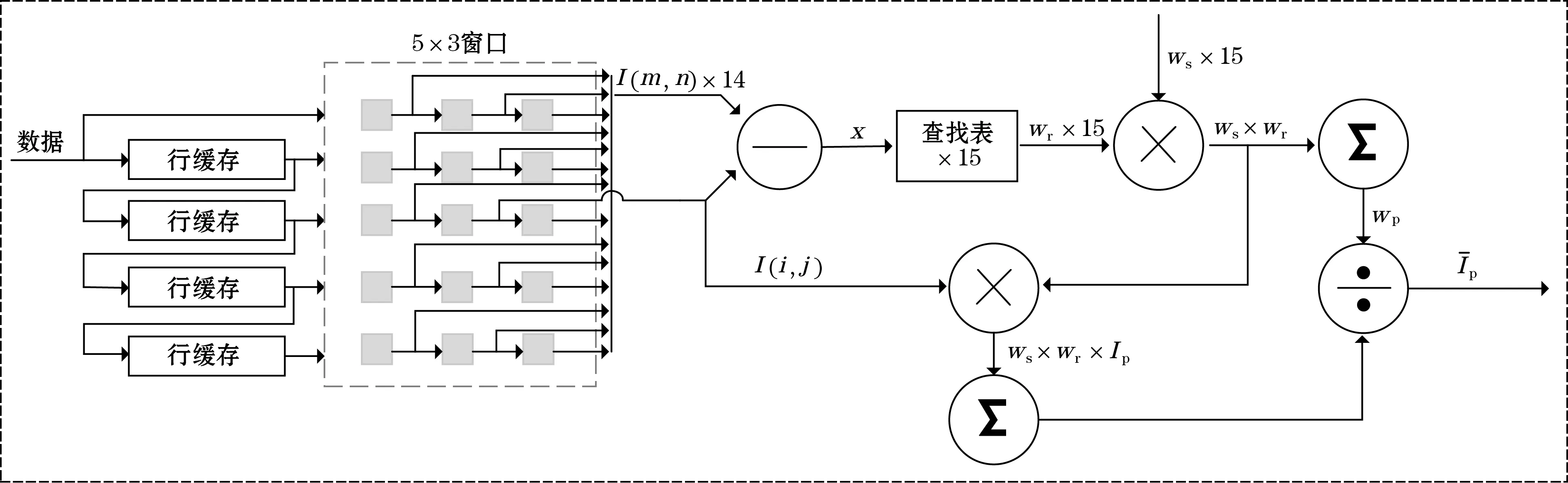

图5为FPGA内部5×3双边滤波算法设计框图,采用4个行缓存FIFO,上一级FIFO读接口与下一级FIFO的写接口相连。内部采用计数器对FIFO中缓存的数据进行计数。当第1级FIFO中数据缓存满一行像素点的同时拉高第2级FIFO读信号与第2级FIFO写信号,以此类推。为了对5×3窗口进行图像卷积运算时补上空白2行像素点,在第3行像素点读入FIFO时便同时取出4个FIFO读端口数据一起组成5×3矩阵第1列数据,将数据存放于寄存器内连打2拍,在第3拍便组成一个完整的5×3矩阵。

图5 双边滤波器算法设计框图

在进行除法运算时,本设计中被除数为36位、除数为28位,如果使用XILINX提供的IP核进行计算,将会消耗40个时钟周期。为了降低延时改为移位比较法,将被除数存放于寄存器当中,除数存放于移位寄存器中。最开始将除数整体左移8位,有效位与被除数进行比较,当被除数大于等于除数时,输出为1,其他情况为0。依次往右移位8次,只需8个时钟即可拼接输出计算结果。

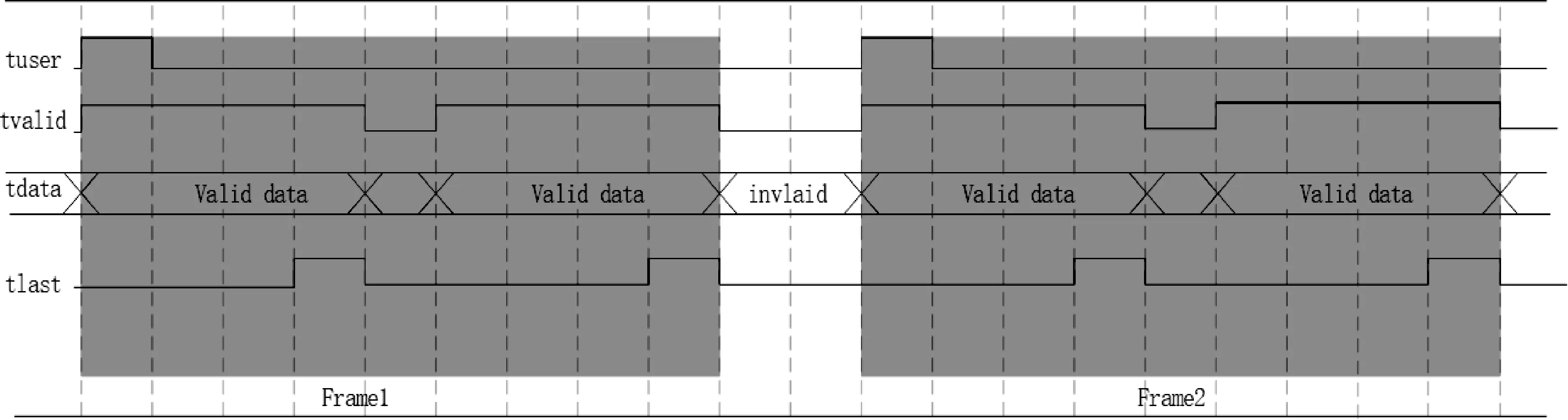

图6为双边滤波器时序设计图。双边滤波器模块采用AXI总线进行设计,tuser为每帧起始使能一个时钟周期,与第一个有效数据对齐,tvalid与有效数据对齐,tlast与每行最后一个有效数据对齐使能一个时钟周期,tdata为数据线,每个时钟周期传递一个像素点的有效数据。该模块的设计灵活,完全符合VGA行扫描时序。

预冷指迅速去除田间热,将产品温度降到适宜温度的过程。预冷是果品冷链保藏运输中必不可少的环节,必须在产地采收后立即进行,若不能及时降温预冷,在运输冷藏过程中很快就会达到成熟状态,大大缩短贮藏寿命。

图6 双边滤波器时序设计图

4 实验结果

表1为采用SPARTEN-7系列的XCS7050FGGA484-1实现本工程的资源利用率以及功耗图。系统内部使用50 MHz时钟对本算法进行硬件加速,功率仅1.3 W。资源使用率低,因此该系统加速是轻量级的。

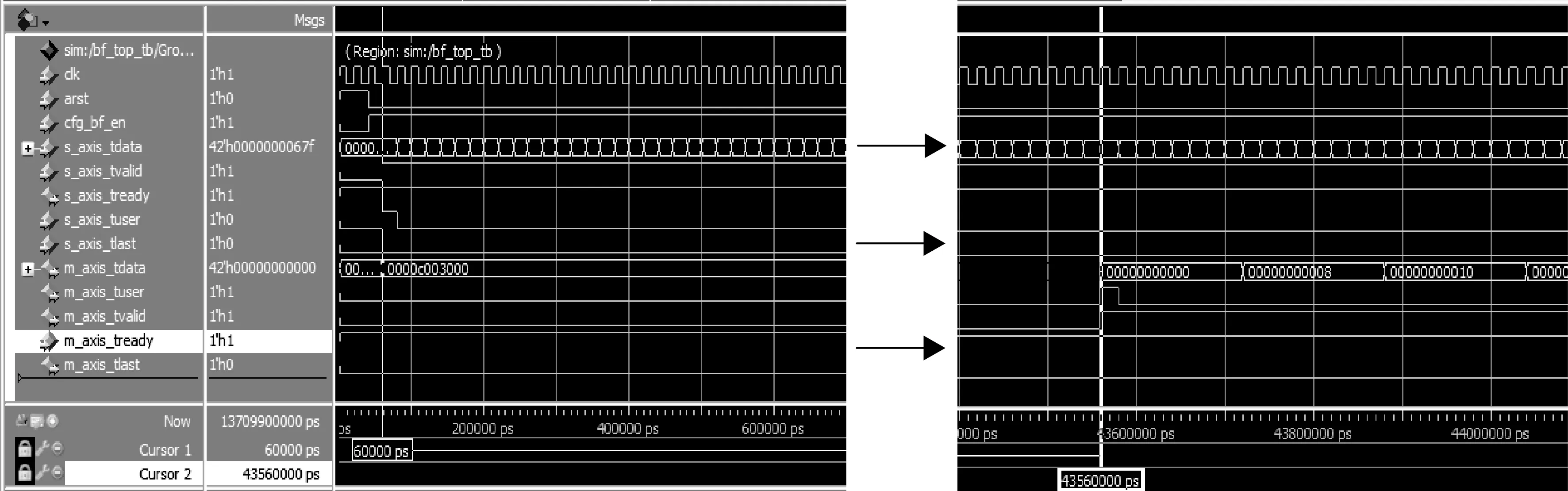

图7为双边滤波器模块Modelsim仿真图,从图7可以看出,数据从s_axis_tvaild有效信号拉高到m_axis_tvaild有效信号拉高总计使用2 175个周期(43.5 μs)。

表1 功耗与资源利用率

使用800×600分辨率的图片对双边滤波系统进行验证,其处理结果如图8所示。

为了更好地对本系统的处理效果进行评估。采用PSNR与SSIM作为图像质量评价指标,PSNR即峰值信噪比,是一种评价图像的客观标准。PSNR数值越大代表图像失真越小。SSIM即结构相似性,是衡量两幅图像相似度的指标。SSIM∈[0,1],其值越大表示失真越小。

(9)

图7 双边滤波器模块Modelsim仿真图

(a)原图

(b)噪声图

(c)FPGA处理图

(10)

SSIM(X,Y)=l(X,Y)c(X,Y)s(X,Y)

(11)

(12)

(13)

(14)

式中:MSE为当前待测图像X与参考图像Y均方误差;H、W为待测图像的宽度和高度;n为像素比特数;μX、μY与σX、σY分别为图像X和图像Y的均值和方差;σXσY为图像X、Y协方差;C1、C2、C3为常数。

表2为PC机与FPGA处理对比。从表2可以看出,图像在PC机上进行同样的处理消耗1.46 s,无法满足实时性要求,在FPGA上对其进行加速处理耗时13 ms。而且经过本系统对图像进行去噪处理后,PSNR指标与SSIM指标都得到了明显提高。

表2 PC机与FPGA处理对比

5 结束语

本文设计了基于FPGA的图像双边滤波处理系统,以提高对图像进行双边滤波处理的速度与能效。对双边滤波算法进行剖析,将算法进行改进。在FPGA上实现了对双边滤波算法的加速。实验结果证明:PSNR与SSIM值得到提升,且实时性得到保证,由此可说明,该系统设计是可行的。本文设计的系统中的双边滤波算法均使用纯Verilog语言及参数化编程,模块可移植性强。