MT系统ADC级联式高倍抽取滤波方法研究

付文涛,孙 娅,韦洪兰,席振铢,黄基文,,李 丽,3

(1.中南大学 地球科学与信息物理学院,湖南 长沙 410083;2.湖南五维地质科技有限公司,湖南 长沙 410083;3.山西省地震局,山西 太原 030021)

1 引 言

在利用大地电磁法采集有用信号的过程中,仪器所使用的ADC(Analog to Digital Converter)发挥着极大作用,目前市场上的ADC不满足大地电磁仪广范围频率的采集,并且对噪声的压制不理想。为此,前人在电磁勘探方法、数据处理及探测仪器上进行了大量的滤波研究。在数据处理中使用的滤波方法也在不断更新,从基于人工神经网络的滤波方法[1]、远参考法[2]、自适应滤波[3]、小波变换法[4,5]、数学形态滤波[6,7]等单滤波方法转变到了组合滤波方法[8,9]。在基于大地电磁仪的滤波方面主要分为模拟滤波及数字滤波。模拟滤波主要对50 Hz、60Hz工频及其谐波干扰进行滤除,常采用模拟陷波滤波器[10,11]以及开关电容滤波器[12]。在一些研究中也对自身电路的噪声等进行了低通或者高通滤波[13,14]。早些时期由于FPGA(Field Programmable Gate Array)芯片内部资源较少,不能满足高阶数字滤波处理,前人基于DSP(Digital Signal Processing)芯片[15]或者专用数字滤波器芯片[16]研究数字滤波,一部分仪器也采用DSP芯片进行数字滤波设计[17,18];另一部分则完全依靠模数转换器的数字滤波功能[19,20]。随着FPGA芯片的发展,其内部资源已经开始能满足低阶数字滤波设计,一些基于FPGA的低阶数字滤波设计应用到了大地电磁仪采集系统中[21]。

近年来,市场上一些FPGA芯片的内部资源已经足够满足高阶数字抽取滤波器的设计,且相应的设计工具也内嵌了各种DSP IP(Intellectual Property)核,包括FIR(Finite Impulse Response Digital Filter) IP 核,极大地方便了高阶数字滤波设计。在数字滤波中,相对IIR(Infinite Impulse Response Digital Filter,无限冲激响应滤波器),FIR(有限冲激响应滤波器)具有稳定性高、通带内具有严格的线性相位、可利用傅里叶变换加快计算速度、易于在FPGA中实现等优点。因此本文提出将模数转换器中的滤波与FPGA中设计的数字FIR抽取滤波器级联,达到高倍抽取的目的,从而在减少处理数据量的同时满足低频信号采集的要求。

2 级联ADC高倍抽取滤波设计

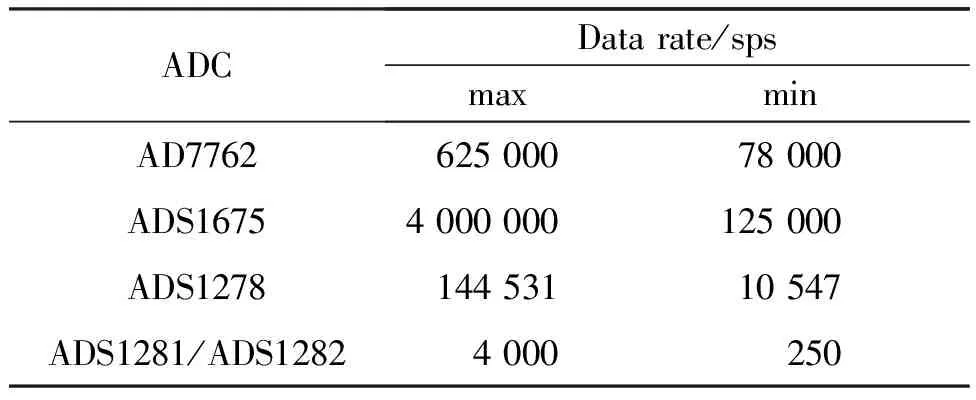

目前先进的大地电磁仪都是基于模数转换器(ADC)作为采集卡,常使用的ADC的数据输出速率如表1所示。由表1可见,所使用的ADC最小数据输出速率均大于100 sps,达不到低频设计要求。

表1 ADC数据输出速率对比

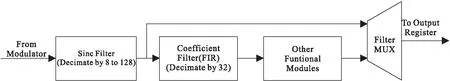

为了解决采集卡不满足低频采集的现状,考虑到近几年来FPGA芯片内部资源的丰富化,本文在FPGA上实现高阶FIR抽取滤波器,共同构成了大地电磁仪接收机的数字抽取滤波系统(图1)。

图1 级联式抽取系统Fig.1 Cascade decimation system

级联式抽取系统中的总抽取倍数R为:

R=RADC*RFPGA

(1)

其中,RADC为ADC中滤波抽取倍数;RFPGA为FPGA中滤波抽取倍数;R,RADC,RFPGA均为无量纲单位。

该系统输出采样率fso为:

(2)

其中,fsi为输入采样率,单位为sps。

该方案具有较大优势:①实现高倍低通抽取滤波,将需要的低频信号保留,有利于分析所采集的地球深部信号;②降低数据速率,减少数据量,可以减少对FPGA及ARM(Advanced RISC Machine)中储存的占用,以满足长时间的采集,并且减少数据量的同时也降低了FFT(Fast Fourier Transform,快速傅里叶变换)运算量,有利于提高运算速度;③抗混叠,避免了数据由于低通滤波而产生的混叠;④充分利用了FPGA资源,避免FPGA资源浪费;⑤避免了选用DSP或专用数字滤波等多个器件而带来的不同器件接口问题。

ADS1282具有高信噪比、低噪声、可编程增益放大器、灵活的数字滤波结构、低功耗、同步输入等优点。该模数转换器还具有高通滤波调试、可编程增益放大调试、数据速率调控、数字滤波结构及相位选择、偏移误差校正等功能。且为用户提供了可选择数字滤波器结构(图2),为级联设计提供了方便。因此本文以ADS1282为例进行级联式数字抽取滤波器设计。

如图2所示,ADS1282采集卡的数字抽取滤波器结构可作为抽取数可设置为8~128的可调Sinc Filter与抽取数为32的FIR滤波器级联,该结构最小输出采样率只有250 sps。为此利用ADS1282为用户提供了可选择数字滤波器结构进行设计,设计中保留采集卡原有的Sinc Filter,应用本文所设计的FIR抽取滤波器。在上述方案中,经过Sinc Filter的最小输出采样率为8 000 sps。

图2 ADS1282的数字滤波器结构Fig.2 Digital filter structure of ADS1282

3 级联FPGA的抽取滤波器设计

3.1 FIR抽取滤波器的设计

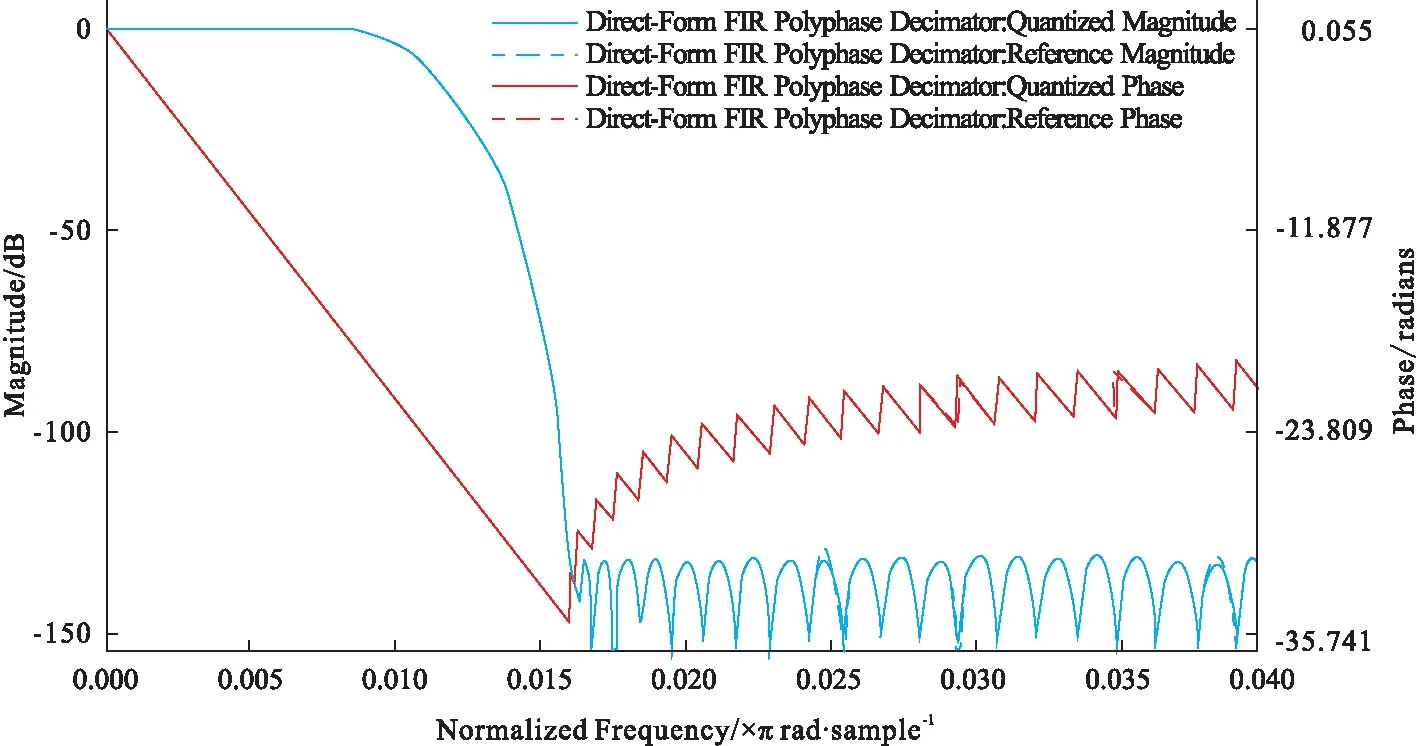

基于FPGA的FIR抽取滤波器指标如下:通带截止频率fc为30 Hz,阻带起始频率fst为64 Hz,输入采样率8 000 Hz,带外压制为137 dB,通带平坦度为0.01 dB,设计方法为Equiripple,采用的是最小阶数设计法,最终总阶数为1 395。

其中,通带截止频率fc满足抗混叠条件:

fsi≥2Rfc

(3)

归一化条件为:

(4)

根据归一化条件对通带截止频率及阻带起始频率进行归一化处理,方便滤波器设计。归一化通带截止频率为0.007 5,无量纲单位。归一化阻带截止频率为0.016,无量纲单位。

为了满足高阶抽取,固定量化系数为24 bit。基于FPGA的大地电磁仪接收机控制系统中数据位宽为32 bit,因此滤波器的输入位宽为32 bit。所设计的滤波器满足128倍抽取数,最小输出采样率为62.5 Hz。采用线性偶对称结构设计减少FPGA内部资源占用。如图3所示在通带及过渡带范围内,所设计的滤波器的相位是严格线性的。

图3 滤波器设计效果Fig.3 Effect diagram of filter design

3.2 FIR抽取滤波器的仿真

3.2.1 基于Simulink的FIR抽取滤波器的仿真

Simulink是嵌入在Matlab中的模块,具有强大仿真功能。本次设计的滤波器在Simulink中进行仿真。

如图4所示,三个输入波形均为Sine Wave,根据滤波器设计的通带截止频率及阻带起始频率,将输入波形分别设置为20 Hz、50 Hz及80 Hz。其中处于通带范围内的20 Hz正弦波幅值为1,处于过渡带范围内的50 Hz正弦波幅值为0.5,处于阻带范围内的80 Hz正弦波幅值为1.5,如图5所示。

图4 FIR抽取滤波在Simulink中的仿真Fig.4 Simulation of FIR decimation filter in Simulink

图5 20 Hz、50 Hz及80 Hz正弦波Fig.5 20 Hz,50 Hz and 80 Hz sine waves

经过Add模块将三个频率进行叠加并输入前面设计好的滤波器中。最后利用Scope模块展示出滤波前及滤波后的波形。

根据图6所示,本文所设计的滤波器成功滤除掉频率为80 Hz及50 Hz的信号,保留了频率较低的20 Hz信号,说明该滤波器的功能满足设计要求。

图6 Simulink仿真中滤波前后的输出Fig.6 Output before and after filtering in Simulink simulation

3.2.2 基于FPGA的FIR抽取滤波器的仿真

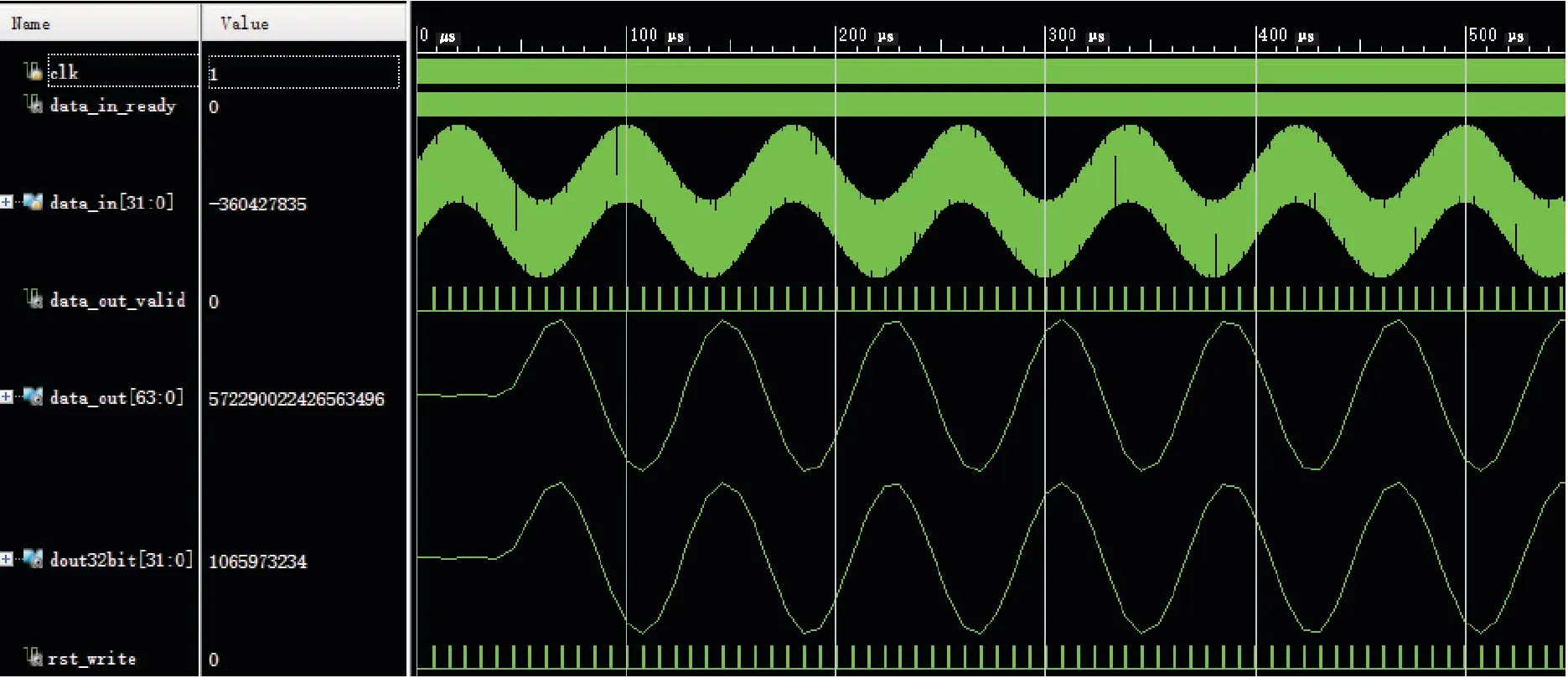

利用FDAtool设计好的数字抽取滤波器以.coe(系数)文件类型导出系数,并将系数导入vivado设计软件中的FIR IP核中。根据上述FIR抽取设计指标设置好FIR IP核,对其进行功能仿真。利用Matlab生成1 Hz正弦波及80 Hz正弦波叠加的混频波,将混频波输入FIR IP核的数据输入端口中。

如图7所示,设计的滤波器在FPGA中得以实现,滤除了80 Hz的“高频”,保留了1 Hz的“低频”,验证了该滤波器基于FPGA的功能可实现性。设计的FIR输出为全精度输出,输出位宽为64 bit。考虑到硬件资源,对滤波器输出采用了截位。去除高位多余的符号位及低位的部分小数位,保留了32 bit的输出。从仿真图可以看出,根据上述方法截位的32 bit输出波形与64 bit全精度输出波形相同,说明该截位方法在该设计中具有应用价值。

图7 基于Vivado的仿真图Fig.7 Simulation diagram based on Vivado

4 抽取滤波器在大地电磁仪采集系统中的应用

采用FPGA+ARM片上系统来设计大地电磁仪采集系统具有很大优势,既能提高数据的传输速度,又能提高数据传输的稳定性。将设计好的抽取滤波以IP核形式嵌入基于FPGA的控制系统中。

如图8所示,利用所设计的ADS1282控制模块分别将5个通道ADS1282所采集的数据缓存到FIFO中,再利用AXI_DATA_FIR模块进行接口转换设计,并将数据输入到FIR IP核中,FIR滤波输出数据经过AXI_DATA_DMA模块转换输入到PL的AXI_DMA中。该设计采用5个通道并行设计,提高了数据的传输及处理能力,极大地缩短了采集时间。

在FIR IP核与AXI_DATA_FIR模块及AXI_DATA_DMA模块互连中,需要对接口进行设计。设计的接口如图9所示,该数据传输主要基于AXI_STREAM模式。该模式下,不需要地址的传输,减少了握手信号,进而减少了数据传输延时,且增强了数据突发能力。

将设计好的FPGA+ARM控制系统进行物理约束,并进行综合及布局布线,进而分析其功耗及资源占用情况。

如图10所示,被占用的资源最高的为PLL(Phase Locked Loop),仅为25 %,因此在资源占用率方面属于正常范围。在功耗方面,动态功耗为1.787 W,总功耗小于2 W,因此功耗也在正常范围内。

图8 大地电磁仪采集系统Fig.8 Magnetotelluric instrument acquisition system

图9 FIR IP核接口设计Fig.9 FIR IP core interface design

图10 资源占用及功耗分析Fig.10 Analysis of resource occupation and power consumption

5 结 论

1)本文提出将ADC的数字滤波与基于FPGA的数字抽取滤波级联的方案,实现了高倍抽取,使大地电磁仪在使用单种采集卡(ADC)的基础上满足更低频率的采集,进而减少了采集系统的功耗以及仪器的体积。

2)采用了系数线性偶对称结构的FIR滤波设计,减少了对FPGA中的乘法器等资源的消耗,也减少了功耗;在Simulink及FPGA上分别对所设计的FIR进行仿真,验证其功能的正确性及基于FPGA的功能可实现性。

3)采用AXI总线中的AXI_STREAM模式进行FIR IP核接口设计,使用更少的握手信号,不仅减少了传输延时,而且增加了数据突发传输的能力。在不影响输出信号完整性的基础上对AXI_DATA_DMA模块数据输出进行截位,保证了输出精度,同时极大地减少了功耗及FPGA芯片内部资源的占用。

4)对包含高阶FIR高倍抽取滤波器的大地电磁仪采集系统进行资源占用率及功耗分析,表明本文所设计的高阶FIR高倍抽取滤波器在大地电磁仪采集系统中具有应用价值。

—— “T”级联