一种高压电平位移电路设计

何宁业,方昊,王云然

(黄山学院信息工程学院,安徽黄山,245041)

1 研究背景

在当代信息产业架构中,集成电路无疑占据着核心地位,也在新一轮技术革命中掌握着主导力量。近年来,作为集成电路发展的关键部分,半导体技术及其制造工艺不断发展、完善和提高。其中,高性能MOSFET器件由于占用面积小、整合度高、驱动功率低、控制能力强等特点,逐渐广泛应用于各个电气设备领域。在整机系统中,控制电路的输出信号一般为PWM脉冲[1],但是其电流和电压特性不足以驱动MOSFET等功率器件,因此需要相应的驱动电路构建桥梁,对该PWM信号进行放大使之具有一定的功率处理能力,并对功率器件的栅极电容进行充电,使其工作在接近理想的开关状态下,从而实现对于功率开关器件的合理控制和应用,提高系统整体效能。

近年来,MOSFET半桥驱动技术在电机驱动、开关电源、电子整流器[2]以及通讯等领域的应用日渐广泛,然而国内目前对于该类电路的研究尚处于起步阶段,系统知识掌握有限,实践操作经验匮乏,应急处理方案不足,大部分市场仍被国外的几大知名公司所垄断。因此,国内迫切需要研制出具有自主知识产权的并且适用于半桥驱动电路中进行信号调试、提高功率处理效能的电路设计方案。

相较国内,国外对于功率集成电路的相关技术研究起步较早,始于二十世纪七十年代后期,如欧洲飞利浦、美国德州仪器等知名企业,主要采用双极结型晶体管BJT和栅极可关断晶闸管GTO等功率器件[3],但是由于所需驱动电流较大,因此驱动电路设计难度大、成本消耗高,发展十分缓慢;至八十年代,随着压控功率器件的产生和不断优化(如MOSFET、DMOS等),电路驱动电流大幅度减小,从而使得整体和局部电路设计更加简易,人力及物力成本大大降低,新型驱动电路的发展势头空前迅猛[4],吸引着众多制造厂商纷纷加入研究和制造的浪潮,产品市场规模稳步扩增。

受各方因素影响我国的电路制造业起步较晚,工艺水平相对国外落后[5]。近年来,经过不断地努力,国内的台积电、华润上华等工艺厂商也逐步扩大对于驱动电路的借鉴学习和自主研制力度,基本掌握了电路设计原理及其有关控制技术,并开发出相应功能的BCD工艺平台[6]。但是由于起步时间晚、人力和物力资源欠缺等,目前我国对于功率驱动电路的研究与发达国家相比仍然存在着较大的差距[7],尤其是在生产实践中依然存有许多问题,如功率处理能力匮乏、产业化程度低下等,因此,亟需科技研究者和相关工作人员提高重视程度,扩充知识储备,争取早日推动我国的集成电路产业跨向新的台阶。

2 总体方案

在整机系统中,控制电路输出的低压逻辑信号常常无法驱动MOSFET等功率器件,因此需要设计合理的驱动电路将其放大,使之具有一定的功率处理能力,从而满足对于功率开关器件的控制需求。基于此问题,本文设计研究驱动电路中的高压电平位移电路模块,使功率电源转换至高边浮动电源,保证高边驱动信号可以开启和关断高压功率器件,从而实现电路功能,降低开关损耗。

本文设计的高压电平位移电路包括LDMOS模块、滤波延时模块、三级反相器缓冲模块和RS触发器模块。首先,由前级电路产生的两路窄脉冲信号分别作为LDMOS电路模块的两路信号输入,经过RC滤波延时模块降低噪声干扰,提高电路可靠性能,然后经延时滤波后的信号进入三级反相器电路实现脉冲延迟和信号整形,最后通过RS触发器将两路信号转为一路方波信号,便于后级驱动负载。此设计不仅能够实现电平位移,也得以在满足功耗小的前提下较好地保障电路的驱动能力。

3 关键电路设计

3.1 CMOS反相器

CMOS反相器是数字集成电路设计最基本的单元电路,其具有集成度高、占用面积小、驱动能力强、电压范围宽以及静态功耗低、抗干扰能力强等优点,被广泛应用于现代数字电路设计中[9]。因此,选用CMOS反相器及其延伸电路作为本次半桥驱动电路中高压电平位移电路研究的基础,也是保障简易电路分析、优化实验结果的关键步骤。CMOS反相器基本电路结构如下图1所示。

图1 CMOS反相器电路图

CMOS反相器电路是由两个增强型的MOS场效应管组成的互补推拉式结构,由图示可以看出相当于两者的“串联”。其中,M0为P沟道增强型MOS管,一般称作负载上拉管;M0’ 为N沟道增强型MOS管,一般作为驱动下拉管。两个MOS管栅极连接在一起,作为反相器电路的信号输入端;各自衬底分别与它们的源极相连,并且M0的源极接电源电压VCC、M0’的源极接地GND;另外,M0和M0’的漏极互相连接共同作为CMOS反相器的输出端。

根据正逻辑约定,记高电平为逻辑“1”状态,低电平为逻辑“0”状态。CMOS反相器的基本原理为:当输入VIN为低电平“0”时,P沟道增强型MOS管M0导通,并且导通内阻很低,约小于1kΩ,而N沟道增强型MOS管M0’截止,截止内阻极高,可达108~109Ω,即流过M0和M0’的静态电流极小,因此在满足静态功耗小的有利条件下使VCC与VOUT之间形成通路,产生一个高电平输出电压“1”;而当输入VIN为高电平“1”时,M0管截止且M0’管导通,VOUT与接地节点NET之间形成通路,产生一个稳定的低电平输出“0”。

综上所述,在静态下,无论输入是高电平还是低电平,M0和M0’总是工作在一者导通而另一者截止的状态,正如所谓的“互补”状态,即共同实现了CMOS反相器的“反相”功能。

3.2 LDMOS电路模块

LDMOS是一种多数载流子导电器件,在频率稳定、高增益、低噪音等方面有着出众的性能,被广泛应用于10~1200V甚至2000V的电压领域。它是一种最早开发的双扩散结构可集成横向功率器件,由于更容易与CMOS工艺兼容,也成为了目前最为主流的功率集成器件之一。本文所设计的LDMOS电路模块如图2所示。

图2 LDMOS 电路图

D1和D2为二极管,它们的正向导通压降VDF=0.5~0.7V,反向击穿电压约为30V,在电路中起到双倍稳压的作用。此外,为了保护栅极和衬底之间的栅氧化层不被击穿,CMOS的输入端常常加有保护电路,由于二极管的钳位作用,也能够使得后级MOS管在正或负尖峰脉冲作用下不易发生损坏;利用电阻R1、R2和R3降低LDMOS管的导通电流,即限制支路电流,从而减少电路功耗,其次,当LDMOS导通时在电阻R1和R2上产生压降△V,也能够保证后级滤波延时电路的安全性和可靠性。

3.3 三级反相器缓冲电路模块

本论文设计的三级反相器缓冲电路结构如上图3所示,用于实现脉冲反相,同时也增大电路驱动能力,对信号起脉冲整形和信号缓冲作用。三级反相器缓冲电路中输入信号IN为前级滤波延时电路产生的输出信号,功率管M8和M9、M10和M11、M12和M13分别组成三个相同的CMOS反相器“串联”组成三级反相器电路,其中各CMOS反相器中的P沟道增强型MOS管作为负载管, N沟道增强型MOS管作为驱动管。

图3 三级反相器缓冲电路图

3.4 RS触发器电路模块

由于前级滤波电路输出的两路窄脉冲宽度的信号不能驱动功率器件,因此需要通过RS触发器将其还原为一路方波信号,即将原来为上升沿触发的信号还原为高电平,下降沿触发的信号还原为低电平,从而便于后级电路驱动负载。

本文设计的RS触发器电路由两个CMOS与非门输入与输出交叉耦合共同构成,其中,单个CMOS与非门电路结构如图4所示。

图4 CMOS与非门电路图

CMOS与非门电路由两个并联的P沟道增强型MOS管M14、M15和两个串联的N沟道增强型MOS管M16、M17组成,A、B为电路的输入端且Y为输出端。CMOS与非门的工作原理为:当A=1、B=0时,M14导通、M17截止,故Y=1;而当A=0、B=1时,M15导通、M16截止,也使Y=1;只有在A=B=1时,M14和M15同时截止且M16和M17同时导通,才有Y=0。由此得出,Y和A、B间为“与非”关系。

MOS 管 M14、M15、M16、M17 和 MOS 管 M14’、M15’、M16’、M17’分别构成上下两个与非门,R和S为信号输入端,其中R为置位端,S为复位端,Q和Q’分别为信号的输出端且两者的逻辑电平相反。

RS触发器以低电平作为输入信号。由于当输入信号同时为“0”状态时会发生输入竞争现象,属于非法输入电平,故该RS触发器的约束条件为输入信号不能同时为“0”。基于此条件下,由与非门构成的RS触发器电路的基本工作原理如表1所示:当输入 R为“0”且 S为“1”时,触发器置“0”;当输入 R为高电平“1”且 S为低电平“0”时,触发器置高电平“1”;当输入R和S同时为高电平“1”时,输出保持不变。RS触发器特性如下表1所示。

表1 由与非门组成的RS触发器特性表

4 仿真结果分析

运用专业仿真软件HSPICE对本文设计的高压电平位移电路进行总体仿真,其中,逻辑电源电压VCC=15V,浮动电源电压VB=8V,控制电压VCCL=1.8V。

LDMOS电路模块中,两窄脉冲信号IN1和IN2分别对应前级脉冲电路输入方波信号上升沿和下降沿,二者脉冲宽度均约为1μs,OUT1和OUT11为两个输出信号,电压仿真波形如图5所示,可实现脉冲电压从0~3.3V到5.04~8V的平移。

图5 LDMOS模块波形图

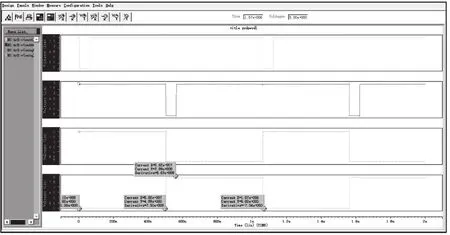

RS触发器模块仿真中,前级三级反相器电路产生的两个输出信号OUT4和OUT44分别对应RS触发器电路的输入信号,电压仿真波形如图6所示,输出端OUTQ约为5~8V、占空比为53.58%、周期为1.069μs的方波信号。综上所述,经过 RS触发器后,原两路脉冲信号还原为一路方波信号,符合设计需求。

图6 RS触发器模块波形图

5 小结

本文实现了一种高压电平位移电路的仿真设计,其核心是LDMOS电路,并在此基础上又添加了包括三级反相器缓冲电路模块、RS触发器电路模块等关键模块。两路窄脉冲信号分别控制两高压LDMOS管的开启和关断,通过LDMOS模块将低电源轨信号传输到浮动高电源轨,实现功率驱动电路功能;利用两级反相器对电路进行缓冲,实现脉冲整形;通过滤波延时电路滤除信号传输过程中产生的噪声dv/dt,提高电路抗干扰能力;最后通过RS触发器电路将两路脉冲信号转换为一路方波信号,便于后级电路驱动负载。在整体电路设计中,为了优化电路运行结果还添加了多级反相器缓冲电路,不仅实现了信号延迟和整形,也有效地增大了电路的驱动能力,一定程度上提高了电路的稳定性能。最后利用专业软件对电路进行仿真分析,验证设计合理性。