一种导航信号频域干扰抑制方法及其FPGA实现*

陈 静,任婵婵,刘金山,刘盛典,李立广

(1.航天恒星科技有限公司,北京 102102;2.天津航天中为数据系统科技有限公司,天津 300301;3.空军装备部北京地区第七军事代表室,北京 100086)

0 引 言

随着导航系统在军民领域应用的深化,导航战也成为继电子战和信息战后的重要作战方式[1-2]。对卫星导航终端设备实施压制式干扰,可以阻止对方区域定位、授时服务进而影响设备的正常运转,所以具备抗干扰能力的终端设备才能在导航战中生存下来。

单天线具有体积小、功耗少、结构简单、接收机不存在互耦和通道失配[3]等优点,是军事领域中单兵作战等无法安装天线阵平台的最佳选择。双频导航接收机作为常用的终端设备,经常受到窄带干扰信号的干扰,当窄带干扰信号的总功率超过系统的干扰容限,会直接影响整个导航接收机的性能。目前常用的抗窄带干扰的方法为时域自适应滤波法和频域自适应滤波法,频域抗窄带干扰方法相对于时域滤波过程更加简洁、灵活性高、处理速度快[4],其算法包括干扰识别、干扰抗剔除、干扰规避三个方面[5]。文献[6-10]提出了频域抗窄带干扰算法实现的干扰抑制、加窗、重叠变换域等技术。

根据文献研究,从提高抗干扰性能和工程实现出发,本文对加窗、混叠、数字自动增益控制(Digital Automatic Gain Control,DAGC)、门限抑制方法进行研究,并充分考虑工程应用环境,在较小资源占用的前提下设计了抗窄带干扰方案,进行了抗干扰现场可编程门阵列(Field Programmable Gate Array,FPGA)工程实现,对于导航接收机系统抗窄带干扰的实际工程应用具有一定参考意义。

1 频域干扰抑制设计

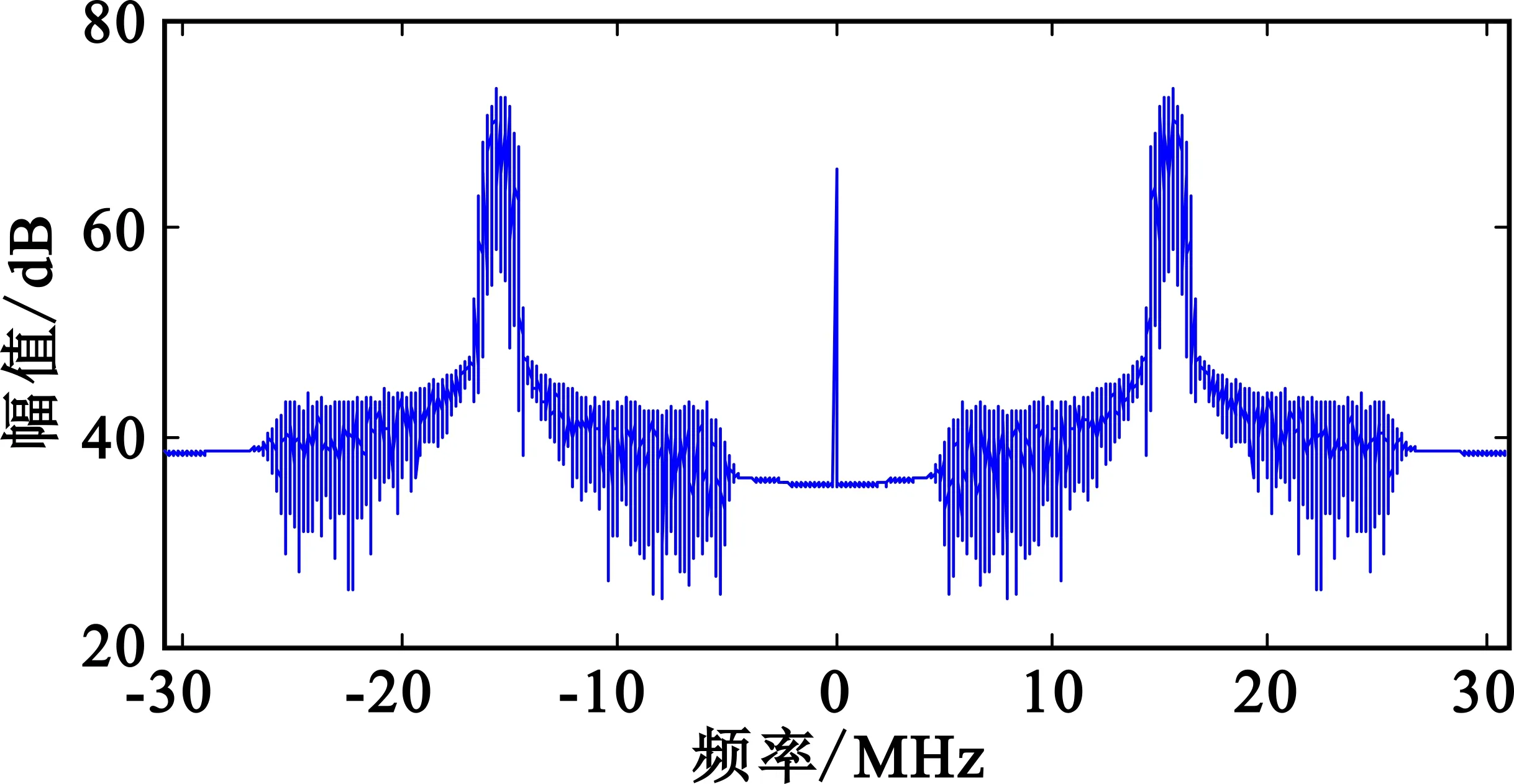

对于压制式干扰,业内普遍认为窄带干扰带宽为有用信号带宽的10%,可用于直接干扰,也可用于扫频干扰。当有用信号带宽为20.46 MHz、中频为15.48 MHz、采样率为62 MHz时,信干比(Signal-to-Jamming Ratio,SJR)为-75 dB的窄带干扰信号进行干扰,含干扰的信号频谱如图1所示。

图1 含干扰信号频谱图

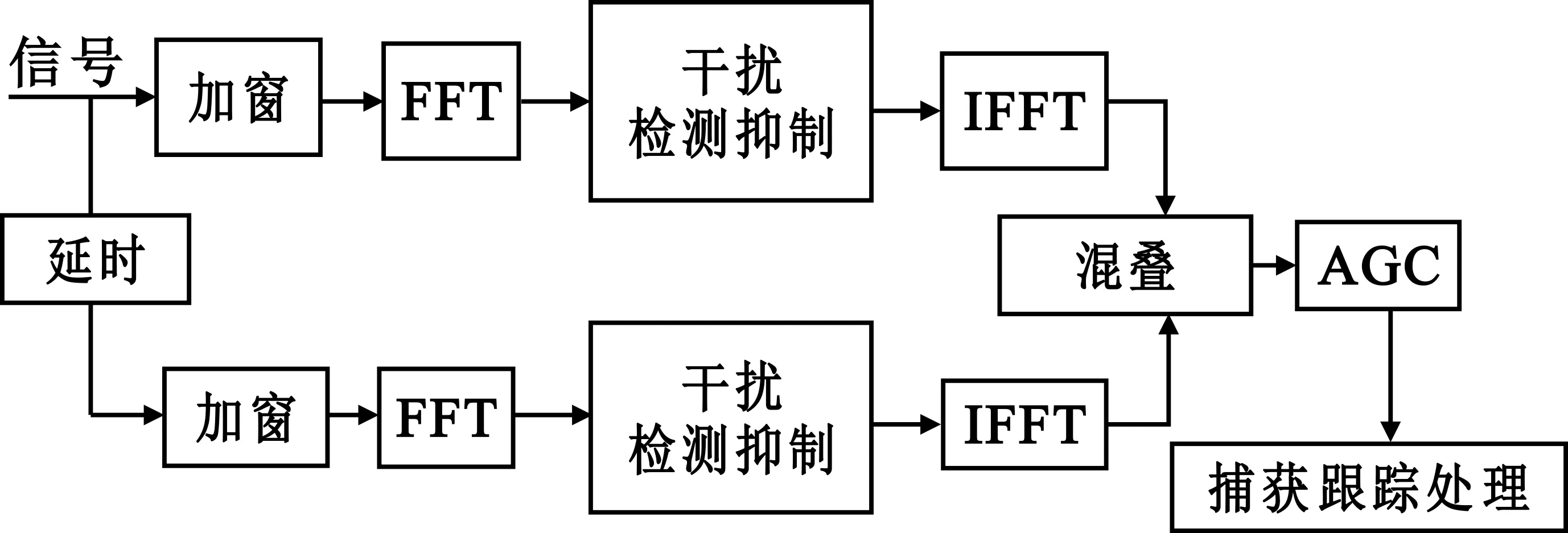

针对此压制式窄带设计了频域干扰抑制的方法,实现过程如图2所示。导航接收机接收到的信号经过射频模块和模数转换后进行抗干扰处理,通过对窗函数、混叠处理设计减少信号的失真。另外,考虑到捕获跟踪所需数字信号位宽,对输出数据进行DAGC设计,提高工程的适用性。

图2 基于频域窄带干扰抑制的方法设计

1.1 加窗处理

窄带干扰抑制方法发生在频域,需将连续的数据进行分割,以实现快速傅里叶变换(Fast Fourier Transform,FFT)。在通过FFT变换到频域时,有限长的数据对应的实际频谱应该是无限宽的,而在应用过程中只取了有限的频带进行窄带干扰抑制,相当于在频域使用了矩形窗滤波。

矩形窗函数旁瓣较高,使窄带干扰边缘附近出现较大的振荡或波纹,影响干扰的滤除。与矩形窗对离散信号的直接截断不同,某些窗函数可以通过平滑截取降低旁瓣[11],如海明窗、汉宁窗、矩形窗、切比雪夫窗、布莱克曼窗等均是常用的窗函数,其时频特性如图3所示。

(a)时域

输入信号x(n)在时域进行加窗处理响应,相当于频域上的卷积:

(1)

为了降低吉布斯效应的影响,需要窗函数的主瓣较窄,主瓣和旁瓣的幅度比值较大。综合分析选取切比雪夫(Chebyshev)窗。如图4所示,Chebyshev窗加入后使得干扰与信号间的过渡带变窄,干扰阻带的衰减变小,降低了干扰抑制时信号频带干扰附近频点被滤除的概率,从而提高了该设计的抗干扰性能。

图4 加窗后信号变化图

1.2 干扰检测抑制

1.2.1 门限抑制法

门限抑制法不需要考虑收敛问题,可以对干扰信号实时处理,因此对于接收机有效捕获之前就被干扰的情况,这种方式可以使接收机快速定位。该方法主要包括干扰归零法和干扰钳位法,两种干扰抑制算法实现过程相同,均是对频域中信号进行阈值比较,干扰归零法把干扰部分直接置零,干扰钳位法把干扰部分钳位到平均噪声值,相位保持不变。

(2)

(3)

式中:N为傅里叶变换和反变换点数,0≤k≤N-1,0≤n≤N-1。

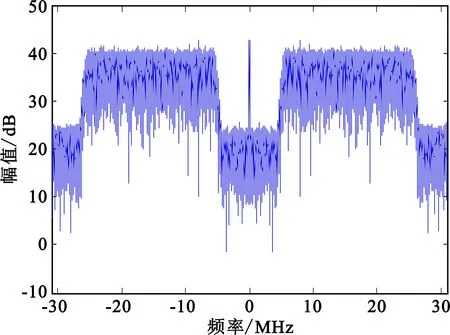

从式(2)和式(3)可以看出,相对于干扰钳位,干扰归零会使导航信号平均噪声降低,但信号伪码失真更严重,对于带宽较宽的干扰归零法更具有优势。图5为带宽为20.46 MHz的含干扰有用信号通过门限抑制法处理后的频谱图,干扰信号被抑制。根据仿真,对于有用信号带宽为10%的窄带干扰,干扰钳位法抗干扰性能更好。

(a)干扰钳位法

抗干扰阈值的选取直接影响着窄带干扰抑制的性能,一般设置抗干扰阈值为噪声功率的倍数,因此需统计噪声功率。由于干扰位置的不确定性,将频带内的数据分为三部分统计功率,取最小值为噪声功率。

门限检测抑制法易于在工程中实现且占用资源较小,但当干扰功率较高时,引起带内相邻导航信号频点幅度的增大,从而使信号频带内部分无干扰频点被滤除,导致信号严重失真,影响接收机性能。因此,该方法适用于一定干扰功率指标需求的环境。

1.2.2 最小均方算法

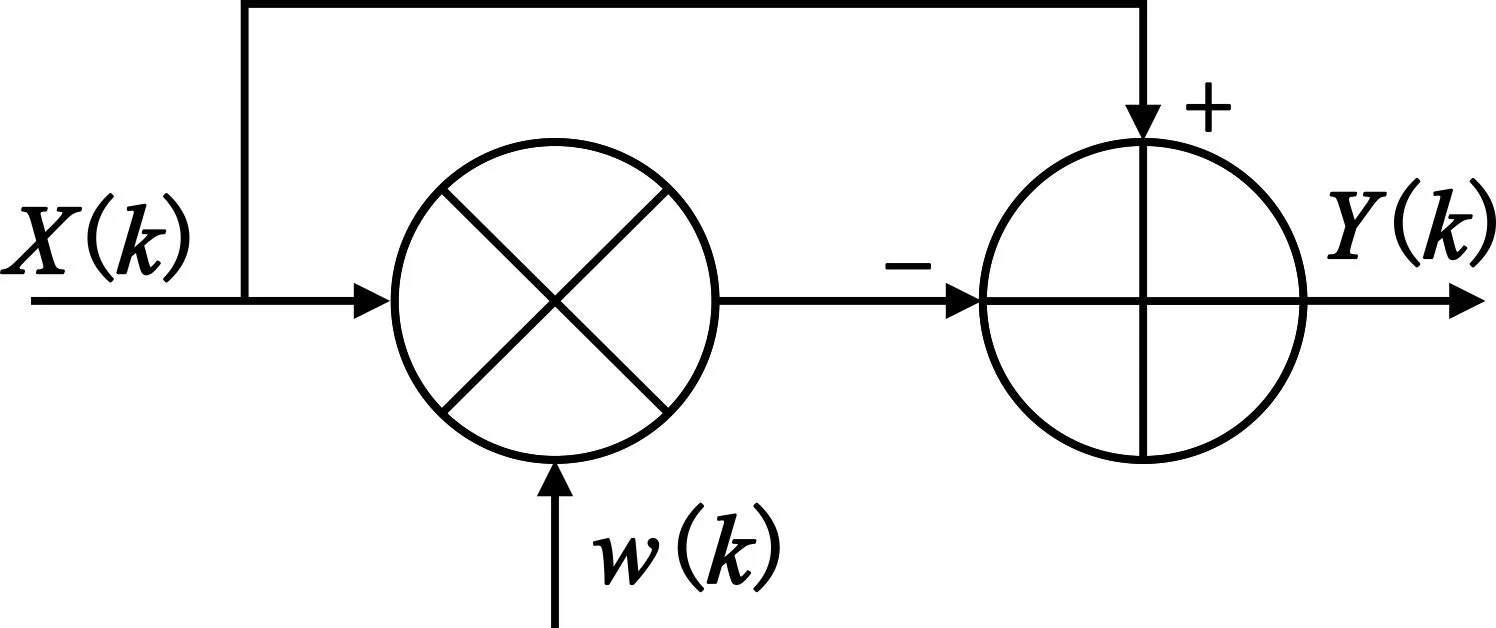

在频域中也可通过最小均方算法来实现窄带干扰的检测滤除,算法流程如图6所示。

图6 最小均方算法流程

由图6可知,经过最小均方算法抗干扰处理后在频域上的输出为

Y(k)=[1-w(k)]X(k)。

(4)

式中:w(k)为权值;X(k)为FFT输出信号。通过计算,权值的更新与当前权值和输入信号功率有关,而且权值更新步长和权值均为实数,其计算式为

w(k+1)=αw(k)+2μ[1-w(k)]X(k)X*(k)。

(5)

式中:α为权值泄露因子,0<α<1;μ为权值步长因子,满足收敛条件时的取值范围为

(6)

式中:σ2为噪声功率,若系统噪声环境稳定,则噪声功率不变的;若噪声环境不稳定,需要实时对噪声功率进行统计。导航接收机接收到的信号噪声功率是稳定的,在抗干扰开始时对噪声功率进行统计即可。

最小均方算法需要不断循环迭代进行收敛,达到抗干扰效果,占用较大资源,且α和μ的配置直接影响对干扰信号的滤除效果,需多次试验确定具体数值。另外,由于其收敛的特性,干扰存在的环境下接收机启动实现定位的时间被延长。根据工程应用中对抗干扰指标的需求,FPGA实现时选取门限抑制法进行抗干扰处理。

1.3 混叠

由于窗不可避免地存在,卷积处理建立时间的影响,使得FFT点数的数据前后两部分存在较严重的畸变,需对数据进行重叠处理改变其影响,混叠比例越高越能改善数据的畸变,但相对地提高了计算的复杂度,实现过程中使资源成倍地增加,当取50%重叠的时候,其整体性能是最优的[12]。如图7所示,进行信号混叠后,时域不连续的状态得到了改善。

图7 加窗和50%混叠后信号时域图

设计过程中使用50%混叠,对混叠前后的信号进行捕获,结果如表1所示。可以看出经过混叠处理,捕获的峰值/噪底约有1 dB的提升,畸变情况得到改善。

表1 混叠前后信号捕获情况

1.4 数字自动增益控制

工程应用时,需要将经过干扰抑制处理后的信号位宽进行变化,以满足捕获跟踪需求。采用DAGC处理避免不同环境下对数据的截位选择变化,使工程更具有适应性。DAGC由数字信号处理算法实现,通过牛顿迭代将算法以分段函数的形式表示为

(7)

式中:Pr为期望输出功率,P0为输出功率,a为增益调整时的放大倍数。

根据文献[13]的分析,AGC系统的期望输出强度范围一般为0.1~0.2 FSB2(FSB为量化器满幅度电平值),对于8 b以上均匀量化器,通常将期望输出强度设置为FSB2/9。

2 频域干扰抑制FPGA实现

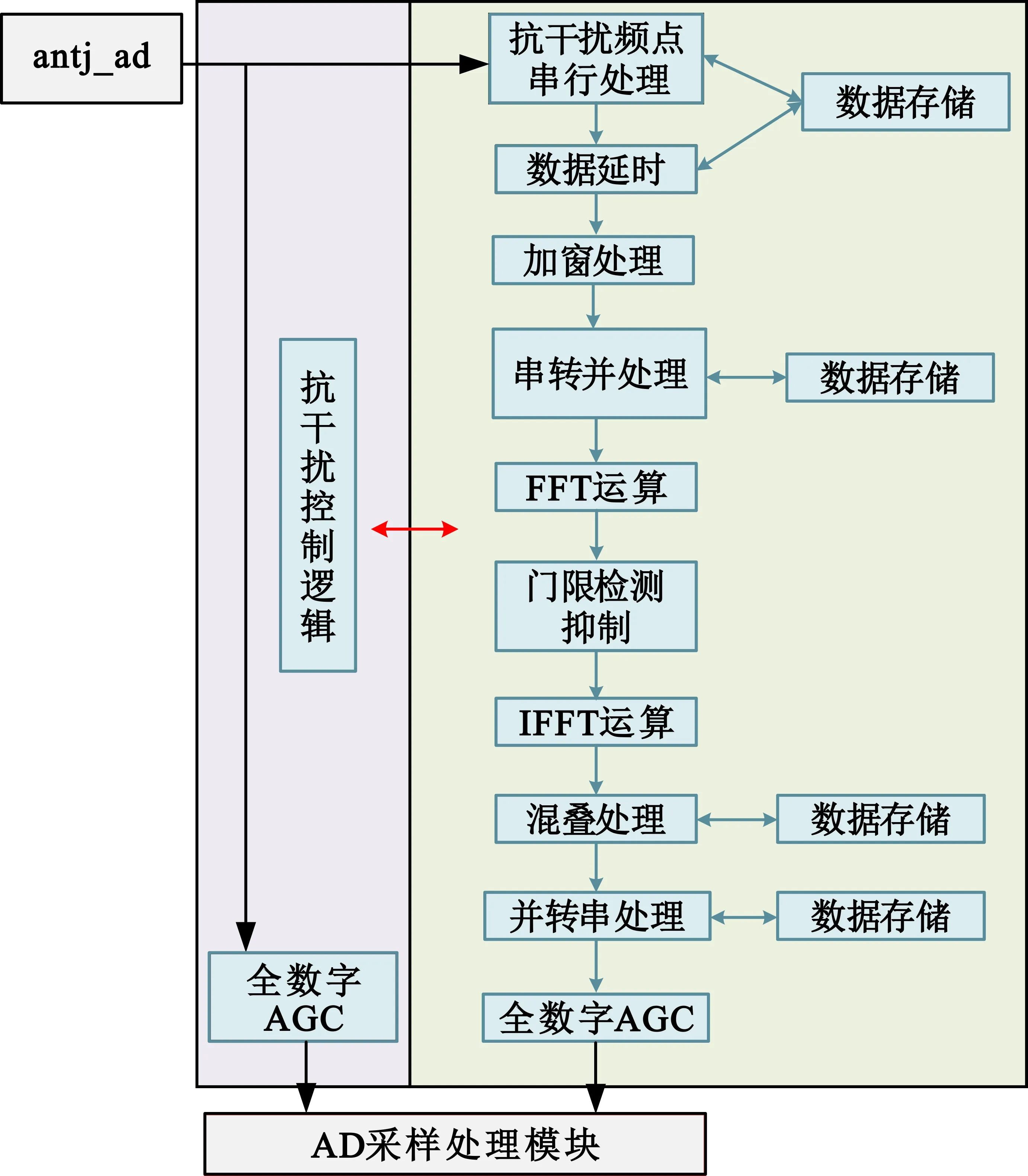

工程应用在双频接收机背景下,抗干扰处理模块需同时处理任意两个频点的含干扰信号,设计过程中将两路信号串行处理,以降低资源使用情况。

根据干扰抑制设计方案进行FPGA实现,流程如图8所示。A/D输出的两路数字信号antj_ad通过随机存取存储器(Random Access Memory,RAM)的读写,将AD数据进行两路信号串行处理以及2 048个时钟的信号时延;4 096点窗系数的上下部分分别与正常数据与实时延数据相乘,进行加窗处理;加窗处理后将两路串行数据通过RAM分别作4×512并行处理,以满足基8的4 096点FFT运算;经过频域门限置零抗干扰处理后,通过RAM对8路并行数据进行混叠处理和串行转换后,进行DAGC处理;最后将抗干扰后的信号输入到AD采样处理模块进行捕获跟踪,使接收机实现定位测速等功能。

图8 FPGA实现流程图

设计的出发点是降低FPGA使用资源的前提下进行双频点抗窄带干扰,所以在工程实现时的关键点一是计算钟配置需大于2倍的采样钟;二是无干扰时取FFT后信号带宽内的频点计算噪底cur_base。计算抗干扰门限时启动cnt_th_cal计数(0~15,计满15时,th_cla_en信号一直置1,直至下一次门限计算),根据软件配置的噪底放大倍数para_thresh,计算抗干扰噪底门限noise_th_use。

para_thresh=[x15,x14,…,x1,x0](参数选取),

(8)

th_use=cur_base×20·x0+cur_base×21·x1+

cur_base×22·x2+…+cur_base×215·x15,

(9)

noise_th_use=th_use/210。

(10)

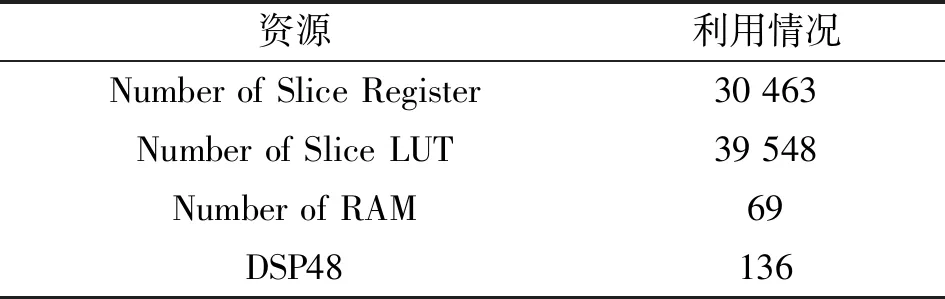

方案在XC7K325t上完成设计输入,通过Synopsys公司的VCS和Verdi工具完成编译仿真,验证工程正确性。资源利用情况如表2所示,可见资源占用较小,可应用于导航接收机中。

表2 FPGA资源占用情况

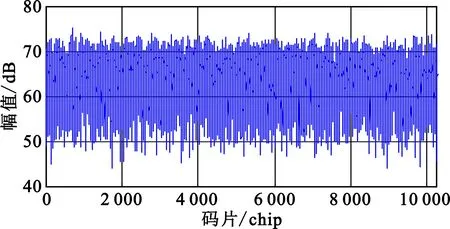

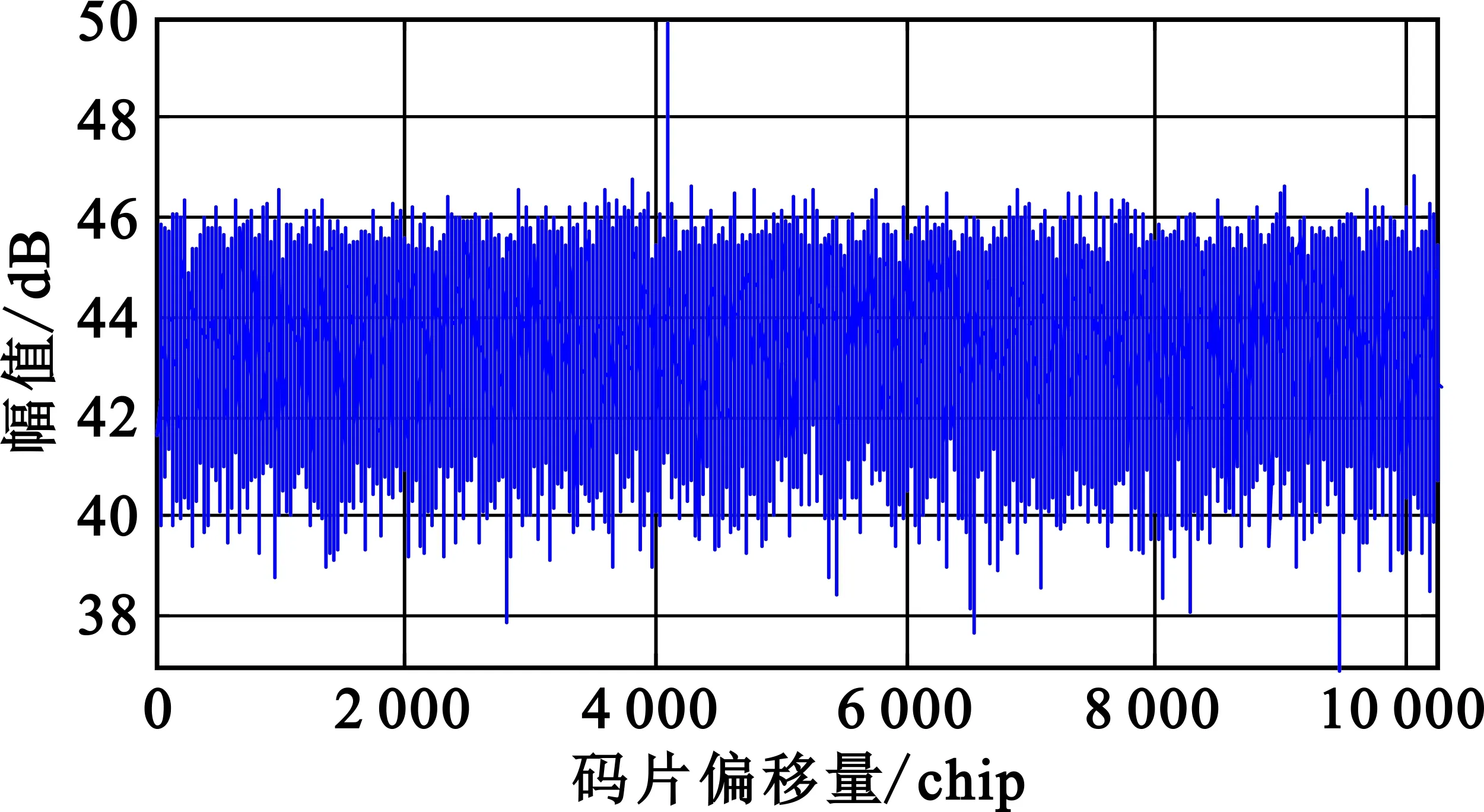

生成的SJR为-75 dB、信号功率为-133 dBm的B3I频点含干扰信号,未经抗干扰处理直接进行捕获,如图9所示,捕获的相关峰淹没在噪声中。经过抗干扰FPGA工程处理后,如图10所示,可以进行有效捕获。经多次仿真验证,抗干扰FPGA工程可以进行抗干扰,比较相同条件下的无干扰信号仿真,含干扰信号抗干扰后噪声减少约1 dB,码的相干性降低约2 dB。

图9 含干扰信号经过抗干扰处理前捕获图

图10 含干扰信号经过抗干扰处理后捕获图

3 系统测试

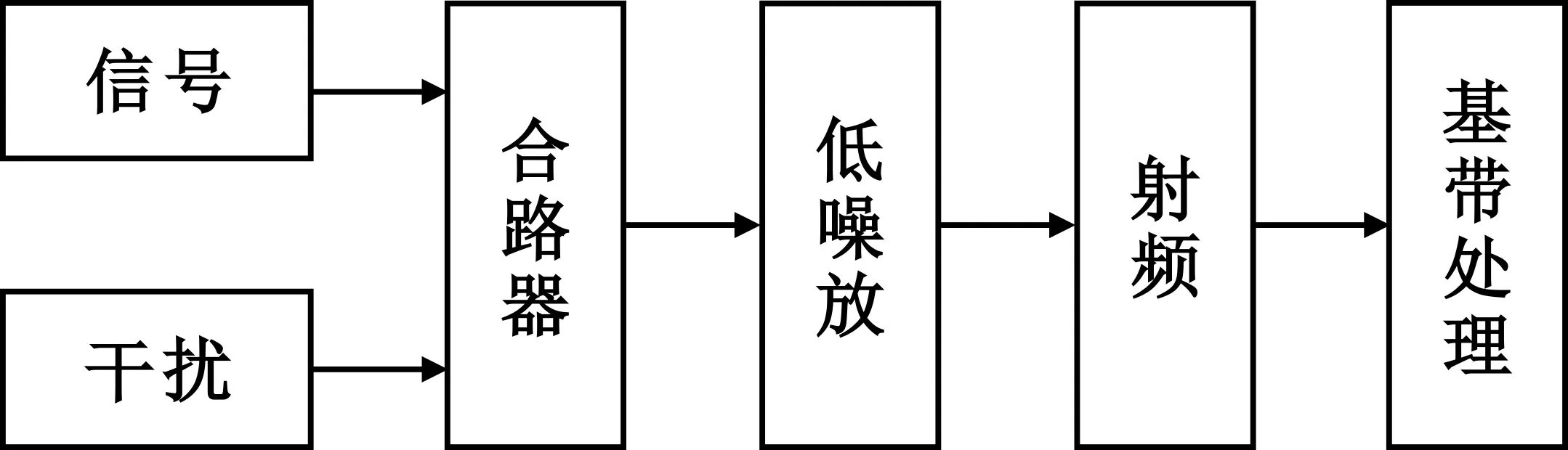

在实际系统测试过程中,信号采用B1I、B3I频点信号,频谱仪标定信号功率为-133 dBm,B1I信号的干扰带宽设置为0.409 6 MHz,中心频点为1 561.098 MHz,B3I信号的干扰带宽设置为2.046 MHz,中心频点为1 268.52 MHz。两路信号通过合路器进入导航接收机,搭建试验平台链路如图11所示。

图11 平台搭建链路图

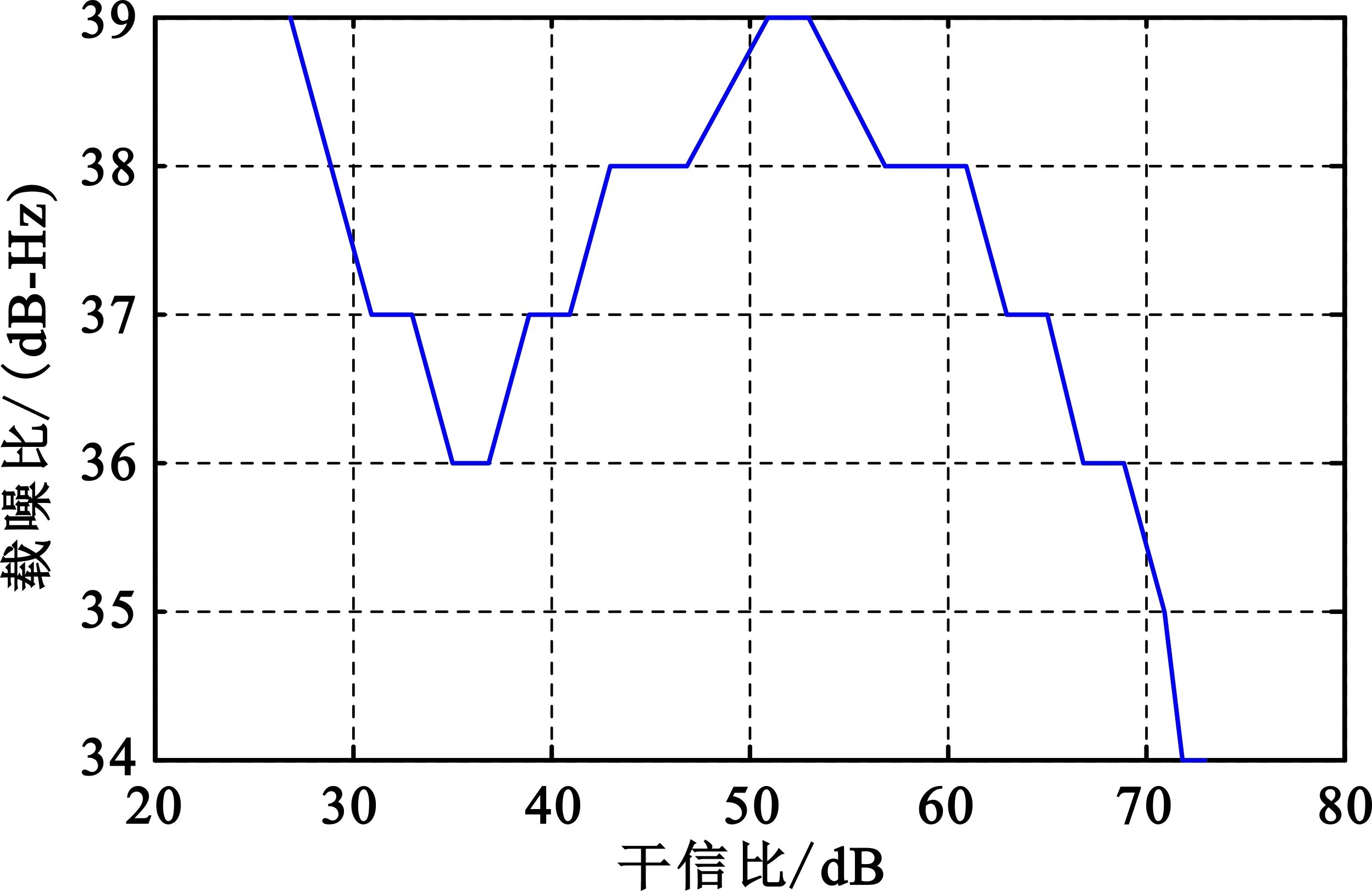

温启动接收机,接收机正常定位后,跟踪后统计的1 s的载噪比为39 dB-Hz。对于无抗干扰设计,当SJR为-26 dB时,接收机不能正常定位。加入抗干扰设计后,接收机载噪比随干扰功率的变化如图12所示:随着干扰功率的增加,通道的载噪比先逐渐降低,当SJR增加到-36 dB时,达到低值;然后逐渐增大,SJR为-54 dB到达顶峰;此后载噪比随干扰功率的增大逐渐降低,当SJR为-78 dB时,接收机跟踪到导航星的个数逐渐减少,直至不能定位,相对于接收机自身该设计方案的抗干扰性能提升了52 dB。

图12 试验过程中载噪比随干扰功率的变化

4 结 论

本文针对双频导航接收机易受干扰的问题设计了一种频域抗窄带干扰方案,并基于该方案实现了基于FPGA的双频点同时抗窄带干扰工程。经仿真试验,抗干扰FPGA工程占用FPGA资源较小,可实时对两种频点的含干扰信号进行抗干扰处理,具备抗干扰功能,比接收机自身的抗干扰性能提升了52 dB,适用于SJR大于-78 dB的干扰环境,为导航接收机系统抗窄带干扰提供了理论和实际工程应用参考。