14位低功耗逐次逼近型模数转换器设计

王一飞,宋树祥,蔡超波,岑明灿,刘振宇

(广西师范大学 电子工程学院, 广西 桂林 541004)

0 引言

随着集成电路制造技术的进步,数字电路的工作频率不断提高,以数字开关为主要模块的逐次逼近型模数转换器(successive approximation register analog to digital converter,SAR ADC)成为研究热点。关于改进SAR ADC性能的技术不断被提出。早在2010年,Liu等[1]提出了单调电容开关的方法来提高能量效率,通过采用N位DAC来实现N+1位ADC;但该方法会使得DAC输出的共模电平不断下降,比较器的动态失调会严重影响ADC的性能,因此该方法不适合高精度应用。2016年,倪亚波等[2]采用二进制冗余补偿法将额外的二进制补偿电容插入DAC电容阵列,来消除DAC不完全建立,比较器失调以及电容失配等对ADC性能的影响;但该补偿电容不仅降低了ADC的线性度,而且总采样电容值得增加使得ADC的动态输入范围降低。2017年Huang等[3]提出了一款采样率为1.2 GS/s分辨率为8位的采用无源残差传输的SAR ADC。2019年,Xie等[4]基于压控振荡器设计了10-bit,5 MS/s的SAR ADC,实现了9.13-bit的有效位数。2020年,曲维越等[5]将顶板采样技术引入二进制缩放重组电容阵列,克服了比较器失调和参考电压抖动对ADC性能的影响,但使用的顶板采样技术对DAC顶板处的寄生电容较为敏感。由此可见,比较器的失调、电路中的寄生参数等都在限制着SAR ADC性能的提高。

为了解决上述问题,本文完成了以下工作:第一,提出一种新型开关策略,与传统开关策略相比,减少电容数量消耗,同时能量消耗降低,此外,设计一种底板采样技术来消除DAC顶板处的寄生电容对ADC性能的影响;第二,使用电容重组的方法设计冗余电容阵列,不需要引入额外的补偿电容,不仅使ADC具有良好的线性度和动态输入范围,而且能够消除DAC不完全建立,比较器失调以及电容失配对ADC性能的影响;第三,根据设计中的冗余电容阵列,提出由少量数字器件实现的数字纠错逻辑,在纠错过程中不会中断ADC的正常工作。

1 SAR ADC电路设计

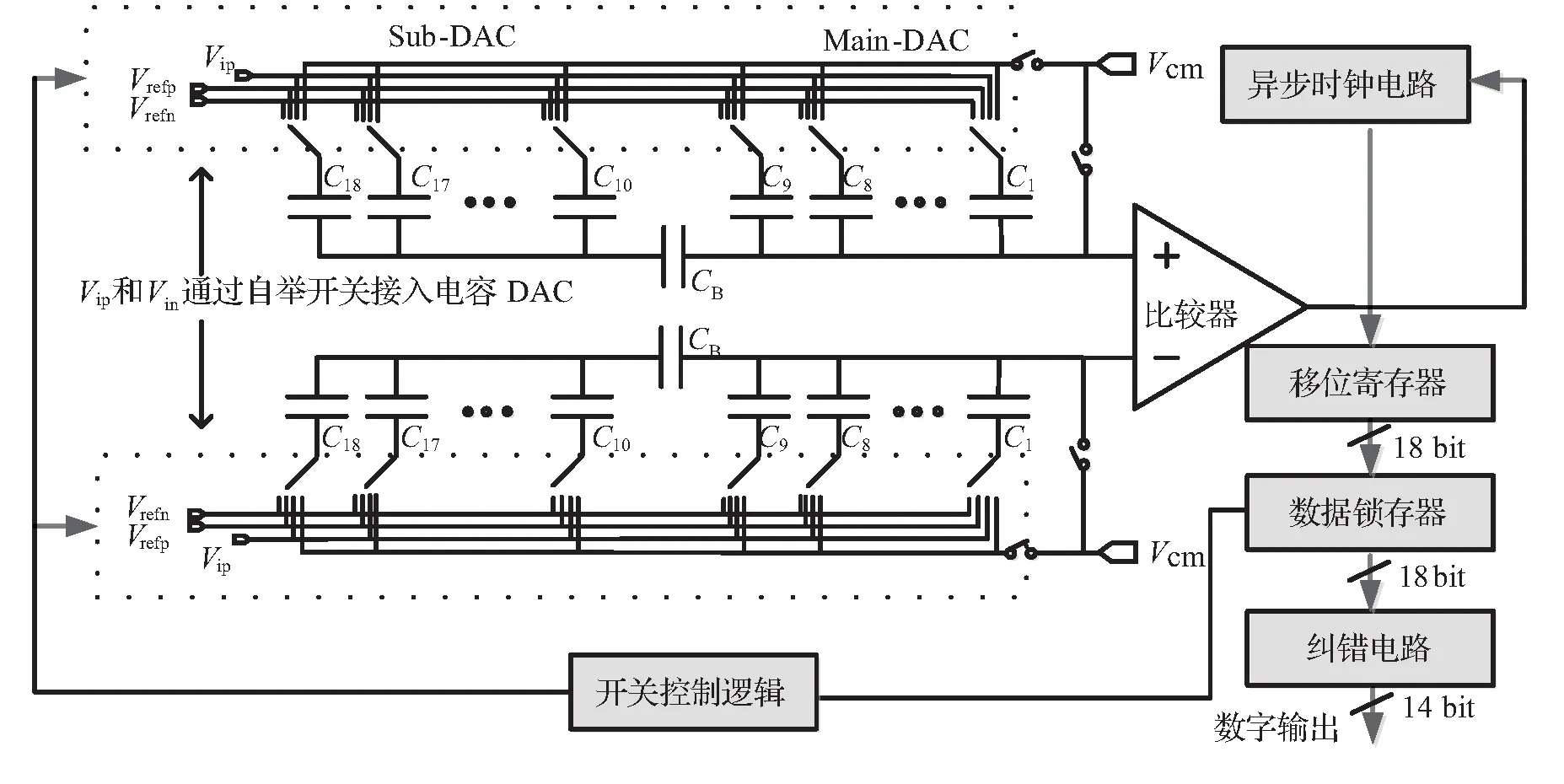

本文所设计的SAR ADC结构如图1所示。该结构主要包括自举采样开关、电容DAC、数字电路和动态锁存比较器等模块。ADC采用全差分结构来实现,以减小电源噪声、共模噪声和衬底噪声对电路性能的影响,而电容DAC和采样保持电路则共用电容阵列,提高了硬件利用效率。此外,采用动态锁存结构的比较器没有静态功耗,在时钟电路的控制下工作,非常适合逐次逼近架构的ADC。本设计通过采用新型开关策略,除了具有较高的能量效率外,还降低了DAC电容阵列一半的电容数量。此外,为了提高SAR ADC系统线性度,本设计采用自举开关作为采样开关。

图1 SAR ADC结构Fig.1 Schematic of SAR ADC structure

1.1 自举采样开关设计

在CMOS集成电路设计过程中,通常使用MOS管做采样开关,由于NMOS管和PMOS管的导通电阻和晶体管的栅源电压Vgs相关,所以不同的输入电压会导致晶体管的导通电阻不同,会给整个SAR ADC电路带来显著的非线性,影响ADC的性能。

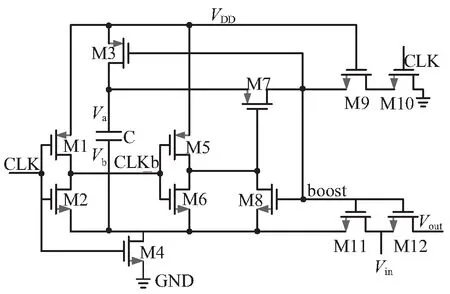

图2 自举开关电路原理图Fig.2 Schematic of bootstrapped switch

为解决上述问题,本文采用了线性度良好的自举开关,自举开关电路原理图如图2所示。CLK和CLK_b为反相信号,当CLK为高电平,M4管导通,使电容C下极板电位Vb接地,M10管导通,使boost节点电位接地将M3管导通,电容上极板电位Va通过M3管接至VDD,M7处于截止区,因此这个阶段实质上是给电容C两端加上压差为VDD的电压,对该电容充电。当CLK为低电平时,M7导通,电容两端储存的电荷量使得M11管导通,故电位Vb和Vin相等,boost节点电位为Vin+VDD,因此在采样阶段采样管M12的栅源电压Vgs恒为VDD,和输入电压Vin无关。

1.2 传统DAC电容开关切换策略

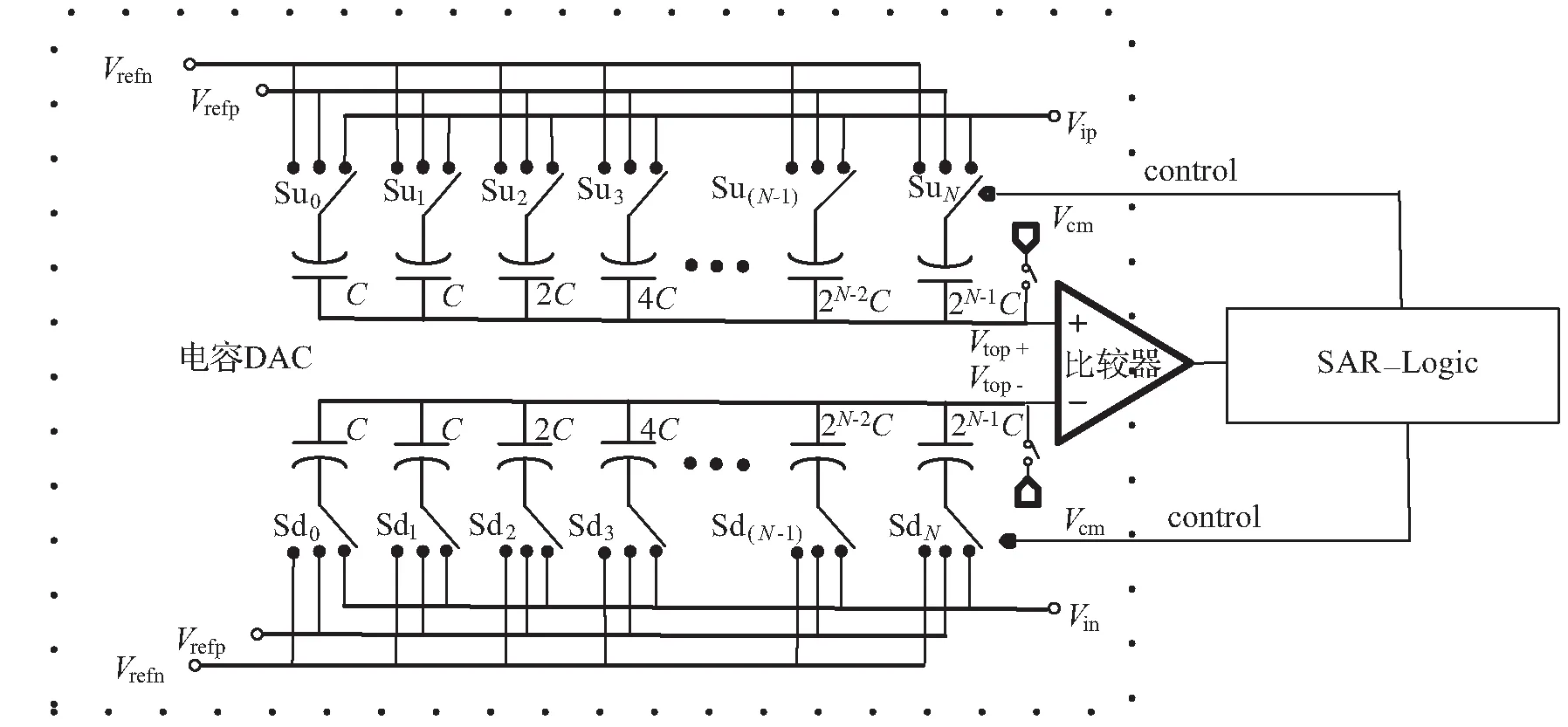

传统N位SAR ADC结构图如图3所示,图3中,Vrefp为电源电压,Vrefn为地电位,Vcm为共模电平。虚线内为N位电容DAC,由N位二进制电容阵列和开关电路组成,开关Su0、Sd0连接的电容为冗余位电容,其作用是提高电路精度,该电容只参与采样过程,转换过程中接固定电位,其中Su0连接的电容在转换过程中底板接Vrefp。Sd0连接的电容在转换过程中底板接Vrefn。规定和比较器连接的电容极板为电容顶板,另外一端为电容底板,Vip和Vin分别为正相端输入信号和反相端输入信号。采样Vip的电容阵列为正电容阵列,采样Vin的电容阵列为负电容阵列。传统的逐次逼近模数转换技术需要精确的器件匹配来实现高分辨率和线性度[6]。

图3 传统N位SAR ADC结构图Fig.3 Schematic of traditional N-bit SAR ADC structure

ADC的工作分采样和量化2个阶段。采样阶段,正负电容阵列顶板都接Vcm,正电容阵列底板接Vip,负电容阵列底板接Vin。采样结束后,进入转换阶段,传统的切换策略是先置位,再比较,首先开始最高有效位(MSB)的预置位,即开关SuN接Vrefn,SuN~SuN-1接Vrefp,SdN接Vrefp,SdN~SdN-1接Vrefn。此时会在正负电容阵列顶板产生2个与输入信号相关的电压信号Vtop+和Vtop-。

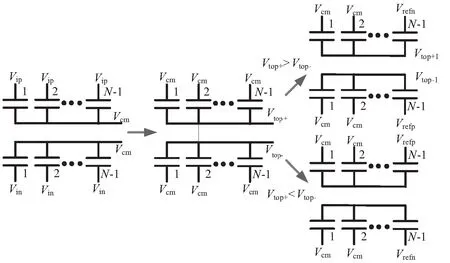

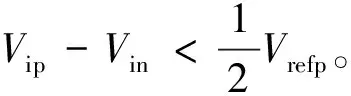

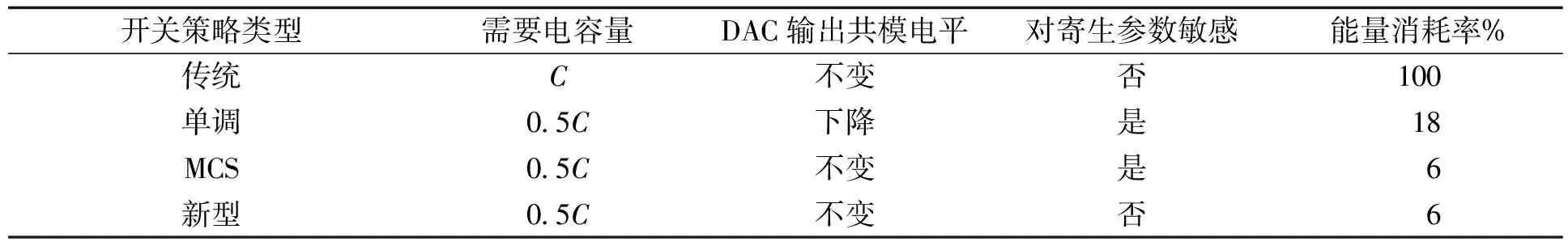

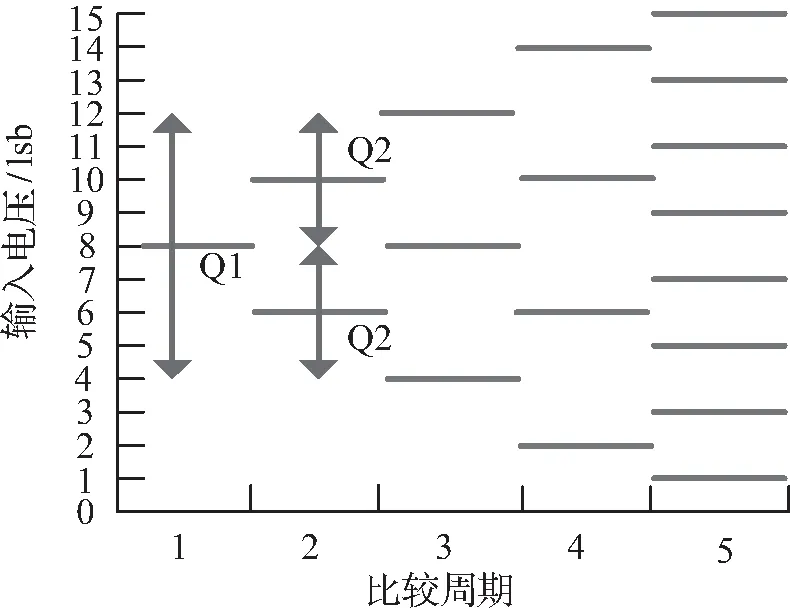

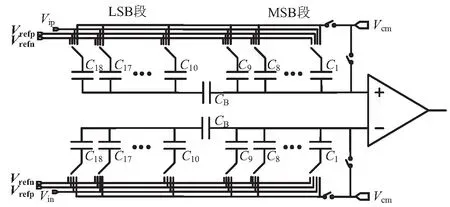

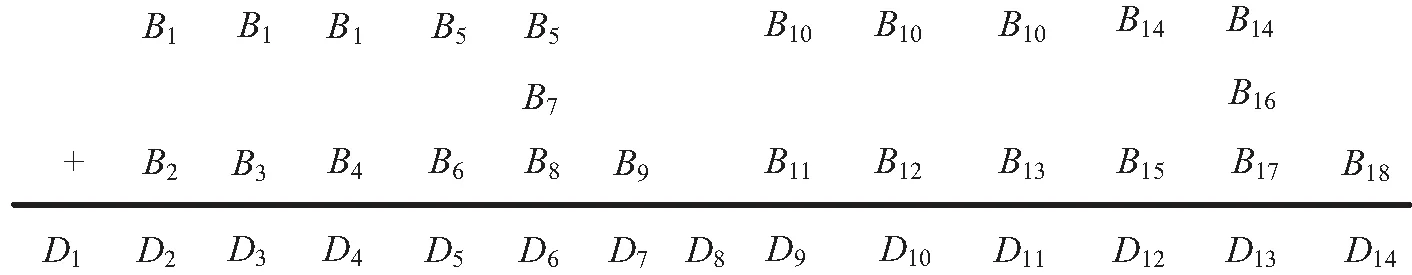

如果Vtop+>Vtop-,即比较器输出结果为“1”(数字高电位,即电源电压),则说明预置正确,MSB位对应的开关状态保持不变,进行次高位的预置;如果Vtop+ 按照以上逻辑,ADC会完成N个比较过程。传统的DAC电容开关切换算法的缺点是电容面积大、动态功耗较高、逻辑控制较复杂[7]。为了应对这些缺点,本文采用了新型DAC电容开关切换策略。 DAC的功耗主要存在于DAC中电容的充放电过程,不同的DAC开关切换方式,对电容的充放电消耗的能量也有所不同[8]。减小DAC的能耗和面积的方法有拆分的电容阵列[9]和新型的电容开关时序[10-13]。为了降低SAR ADC的功耗,近年来陆续提出了拆分、单调[1]及MCS(merged capacitor switching)[14]等多种低功耗D/A网络电容开关切换方式[15]。本电路中所采用的新型开关策略和传统开关策略相比,在保持了底板采样对寄生参数不敏感的优势下,进一步提高了能量效率。如图4所示,Vrefp、Vrefn和Vcm代表含义与前文描述保持一致。在采样阶段,电容阵列对输入信号Vip和Vin进行采样。假设采样时间满足电容阵列建立时间的要求,设总电容值为Ctotal,则正负电容阵列储存的电荷量Q+和Q-分别为 Q+=(Vcm-Vip)·Ctotal, (1) Q-=(Vcm-Vin)·Ctotal。 (2) 采样结束后,ADC进入保持阶段,正负电容阵列的底板全部接Vcm,Vcm从电容阵列的顶板断开, 图4 新型开关策略Fig.4 New switching strategy 此时根据电荷守恒定理可得正负电容阵列顶板电位Vtop+和Vtop-分别为 Vtop+=2Vcm-Vip=Vrefp-Vip, (3) Vtop-=2Vcm-Vin=Vrefp-Vin。 (4) 接下来是转换阶段,如果Vtop+>Vtop-,即Vip-Vin<0。 此时最高位数字码Bn=0,反之则为1。接着进行次高位的转换,正电容阵列最高权重电容N-1的底板接Vrefn,其余电容的底板接Vcm;负电容阵列最高权重电容N-1的底板接Vrefp,其余电容的底板接Vcm。此时电容阵列顶板的电位Vtop+1,Vtop-1分别为 (5) (6) 这时次高位数字码Bn-1=0,反之则为1。按照以上逻辑,ADC会完成N个比较过程。 新型开关策略和部分已知开关策略对比见表1。 表1 不同开关策略对比Tab.1 Comparison of different switching strategies 通过对比可以发现,新型开关策略在减少电容量的同时,具有较低的能量消耗,并且DAC输出共模电平不变和对寄生参数不敏感的特性,使得其能满足本设计高精度、低功耗的要求。 对于一个N位的SARADC,需要M个比较周期(M>N),将会产生2M个比较结果,这些结果需要映射到2N个数字码上,因此该结构会产生的数字码冗余总量Redtotal为2M-2N。这些冗余量会分布在各个比较周期中。如果输入的电压信号位于特定比较周期的可纠错电压范围内,则即使在该比较周期中比较器发生了误判,在后续的比较周期中仍能够纠正,使最终结果正确,SAR ADC的可纠错电压范围如图5所示。 设Wi是第i个比较周期的权值,Qi为第i个比较周期的可纠错电压范围,Qi可以被表示为 (7) 图5 SAR ADC的可纠错电压范围 Fig.5 Error correcting voltage range of SAR ADC 最后一个比较周期的可纠错电压范围为0。 当M=5,N=4时,以实现权值为W1=4,W2=4,W3=4,W4=2,W5=1的ADC为例,该SAR ADC的可纠错电压范围如图5所示。 由等式(7)可得:Q1=8;Q2=8;Q3=0;Q4=0;Q5=0。 由图5可知,该电容阵列产生的数字码冗余总量Redtotal为25-24=16。 这些冗余总量分布在1、2比较周期内。 对于一个N位M个转换周期的冗余SAR ADC(M>N),由于具有M个比较周期,因此会产生M个比较结果即原始码即Ri(i=1,2,3,…,M)。 设在第k个周期,DAC产生的参考电压为Vref(k),Ci为第i位电容所占的权值,在新型开关策略下Vref(1)为2N-1·lsb,Vref(k)为 (8) 当M=5,N=4,以实现权值W1=4,W2=4,W3=4,W4=2,W5=1的冗余SAR ADC为例,为验证冗余电容阵列的容错性,输入为9.5l lsb(least significant bit)的模拟信号,不同的比较过程如图6所示,图6(a)为比较器的五次判断全都正确的情况,得到的最终数字输出为Dout=9。 图6(b)为比较器在第一个比较周期内发生了判断错误,在之后4次判断正确的转换过程,得到的最终数字输出为Dout=9。 由于此时的输入电压信号在第一个比较周期的可纠错电压范围内,因此第一个周期的比较错误,可以在后续的比较过程中进行纠错。利用冗余电容阵列此特性,可以对抗比较器由于失配或者噪声而产生的误判。 图7 传统二进制电容阵列Fig.7 Traditional binary capacitor array 对于传统的电容DAC开关策略,实现一个N位的SAR ADC需要N位的电容DAC,将新型开关策略引入之后,实现一个N位的SAR ADC只需要一个N-1位的电容DAC,大大降低了电容数量的消耗。在使用新型开关策略的情况下,实现一个14位SAR ADC需要的传统二进制电容阵列如图7所示: C1,C2…,C13构成了7+6位电容DAC的电容阵列,C14为冗余位电容,只参与采样,不参与转换过程。电容阵列分为MSB段和LSB段,两段通过桥接电容CB连接,13个单位电容的有效权重依次为:8 192:4 096:2 048:1 024:512:256:128:64:32:16:8:4:2:1。 将上述传统的二进制电容阵列进行拆分得到本设计的冗余电容阵列,电容陈列拆分、插入过程如图8所示,MSB段的最高有效权重Wmsb=8 192,LSB段的最高有效权重Wlsb=64。将Wmsb拆分成三部分权重插入MSB段电容阵列,拆分、插入过程如图8(a)所示;将Wlsb也拆分成三部分权重插入LSB段电容阵列,拆分插入过程如图8(b)所示。 图8 电容阵列拆分、插入过程Fig.8 Process of splitting and inserting capacitor array 经过上述过程后,得到本文设计的分段冗余电容阵列如图9所示。图中C1,C2…,C18的电容值的比值为56∶32∶16∶8∶6∶4∶2∶1∶28∶16∶8∶4∶3∶2∶1∶1∶1。其中桥接电容CB的值和C9、C16、C17、C18相等。 图9 分段冗余电容阵列Fig.9 Segmented redundant capacitor array 数字输出Dout可以表示为 Dout=B1×(213-210)+B2×212+B3×211+B4×210+B5×(29+28)+B6×29+B7×28+ (9) 最终的数字输出码逻辑表达式如图10所示。 图10 数字输出码逻辑表达式Fig.10 Logic expression of digital output code 比较器作为模数转换电路关键模块之一,其速度、精度、功耗等性能决定了ADC电路的整体性能[16]。本设计中使用的比较器电路原理如图11所示。由图11可见,在时钟信号的控制下工作,与SAR ADC的工作方式非常契合。比较器工作分复位阶段和再生阶段。在复位阶段,CLK为低电平,CLK_b为高电平,M5、M8管导通,正相输出端Vout+和反相输出端Vout-的电位复位到地,节点电位op、on被充电至VDD。在再生阶段,CLK为高电平,CLK_b为低电平,M13管导通,节点电位op、on开始从VDD电位放电,由于输入信号Vin+和Vin-的不同导致op、on节点的电位下降速度不同。假设Vin+电位高于Vin-,则op节点电位下降速度较快,M3管先导通,Vout+节点会首先被VDD充电,接下来on节点下降到M4管导通,M1,M2,M6,M7构成正反馈,会迅速将节点Vout+电位拉至到VDD、Vout-节点电位拉至GND。 图11 比较器电路原理Fig.11 Schematic of comparator 本设计的版图主要依据中心对称的原则进行布局布线,电路版图如图12所示,数字电路部分和模拟电路部分进行了严格的隔离,避免了数字信号的跳变对模拟部分电路的干扰。电容阵列在比较器正负输入端对称排列,保证正负输入端的阻抗相等,电容阵列周围使用了dummy电容,避免芯片中的噪声对电容阵列中的关键信号造成影响。最终得到的版图面积为421 μm×271 μm。 图12 电路版图Fig.12 Layout of circuit 在室温(27 ℃)条件下,当ADC工作在采样频率为1 MHz时,输入频率为0.301 MHz的满输入范围正弦波,对本设计进行动态参数仿真,取1 024个点进行快速傅里叶变换,计算ADC的频谱参数,以此分析出各个动态参数,通过后仿数据得到的频谱图(最差工艺角下)如图13所示,各项参数已在频谱图上标出。在TT(Typical)、FF(Fast)、SS(Slow)工艺角下后仿具体参数见表2,fs为ADC采样频率,fin为输入模拟信号的频率。 图13 频谱图Fig.13 Spectrum 表2 不同工艺角下后仿结果Tab.2 Post simulation results under different process angles 表3列出了部分已知文献和本设计性能对比,通过对比可以看出本设计具有高精度和低功耗的优势。 表3 性能对比Tab.3 Performance comparison 本设计在110 nm CMOS工艺下,采用电荷重分配型SAR ADC架构,为了提高ADC的精度,采用冗余电容阵列结构,增加了电路容错性的同时减轻了SAR ADC精度对内置DAC建立精度的要求。本设计所采用的新型开关策略,和传统开关策略相比,不仅降低了能量和一半的电容数量消耗,而且对寄生参数不敏感,DAC输出共模电平不变,满足了高精度、低功耗的设计要求。通过使用Cadence模拟开发套件在不同工艺角下进行后仿,验证了本设计的可行性。1.3 新型DAC电容开关切换策略

1.4 冗余电容阵列

1.5 冗余电容阵列的纠错功能

1.6 分段式冗余电容阵列设计

B8×28+B9×27+B10×(26-23)+B11×25+B12×24+B13×23+B14×(22+2)+

B15×22+B16×2+B17×2+B18。

1.7 动态锁存比较器

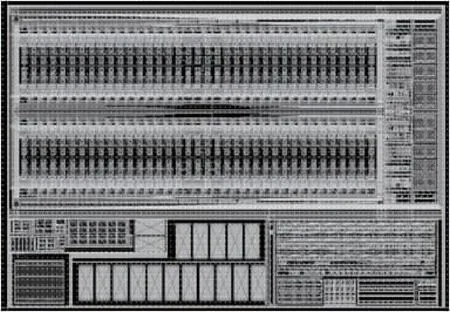

2 版图设计与仿真

2.1 版图设计

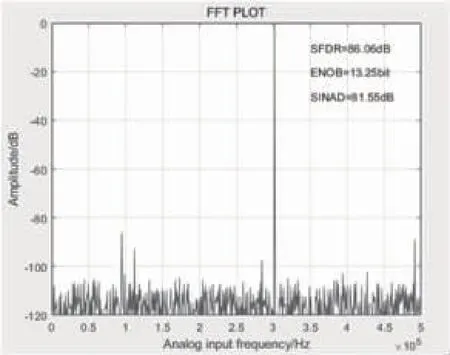

2.2 后仿验证

3 结语