边界扫描寄存器电路的性能分析和优化设计

孙 诚,邵 健

(中电科申泰信息科技有限公司,江苏无锡 214000)

1 引言

数字电路的复杂性决定了在测试中需要能够访问各种外设或内核模块,同时需要在测试时能够把它们彼此隔离开且不得明显增加测试成本的方法[1]。联合测试工作组(Joint Test Action Group,JTAG)和电子与电气工程师协会(The Institute of Electrical and Electronics Engineers,IEEE)共同提出了将串行测试数据移位输出到一个电路板接口的一套规范,也被称为边界扫描[2]。由于省去了用物理探针探测被测组件引脚的过程,该方法提高了对数字电路内部的可控性和可观测性[3]。

JTAG标准的核心思想是在芯片管脚和芯片内部逻辑之间增添移位寄存器组,被称为边界扫描寄存器(Boundary Scan Register,BSR)[4]。BSR的引入使得芯片在测试数据输入(Test Data Input,TDI)端口和测试数据输出(Test Data Output,TDO)端口之间形成一个扫描通道[5]。TDI端口用来将串行测试数据输入芯片,并移入BSR内,TDO端口用于串行输出测试数据[6]。

典型的BSR包括一组通用数据输入输出端口,以及TDI和TDO端口。非测试模式下,通用数据输入输出端口用于芯片内部逻辑和输入输出(Input Output,IO)引脚的信号交互;测试模式下,测试数据通过TDI端口移入BSR,或者捕获通用数据输入端口的信号,通过TDO端口移出BSR[7]。

存在于IEEE 1149.1标准之下的多种BSR单元的设计,主要包括具有一组通用数据输入输出端口的BSR电路和具有两组通用数据输入输出端口的BSR电路[8]。本文在此基础上,对现有的BSR电路进行优化,在保持原有功能的情况下力求电路性能参数指标最优化,进而构建出最优的BSR单元。

2 基本电路模型

2.1 边界扫描链

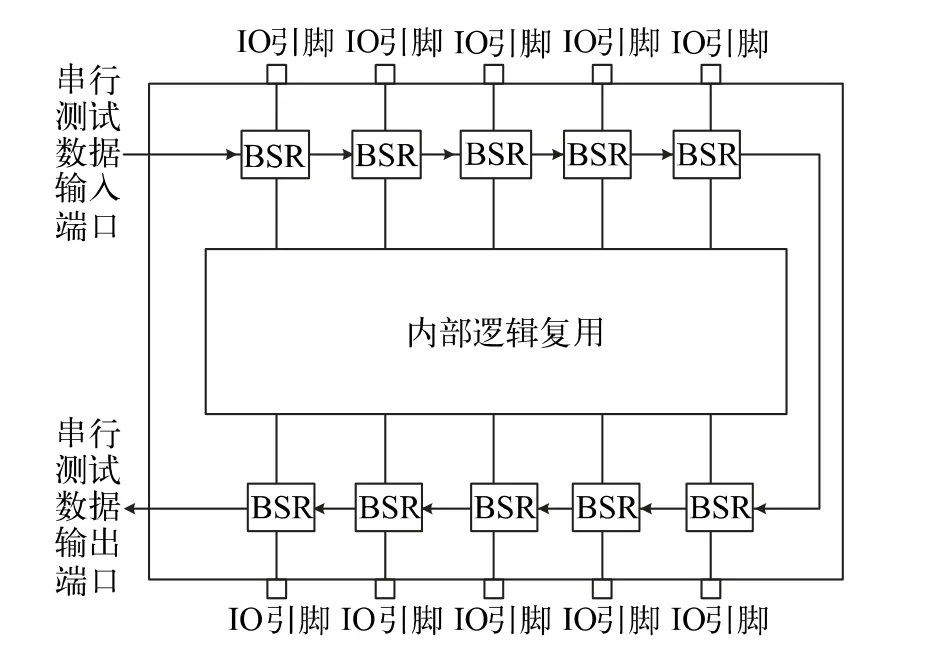

基本的边界扫描链(Boundary Scan Chain,BSC)结构如图1所示,若干BSR通过串行移位的方式连接,测试数据通过TDI端口移入BSC,最终通过TDO端口移出数据。与此同时,BSC起到了连接IO引脚和内部逻辑的作用,通过内部的IO引脚方向复用逻辑确定将要测试的引脚功能,进而实现引脚输入或输出功能的测试。

图1 BSC结构

2.2 传统边界扫描寄存器单元

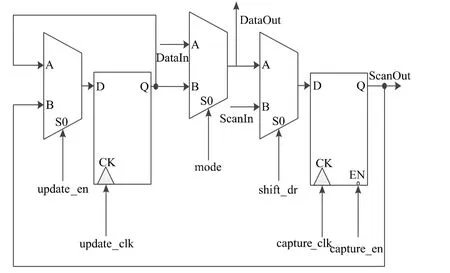

传统的BSR单元结构如图2所示,整个单元由2个多路选择器和2个D触发器组成。触发器的时钟和复位信号应该与系统时钟和复位保持一致。多路选择器的选择端信号应受到如图3所示的测试接入端口(Test Access Port,TAP)控制器的控制,在控制器状态机处于某一状态时,使能相对应控制信号。

图2 传统BSR单元

3 BSR设计方法

在传统BSR单元的基础上,可以将传统单元结构进行变形,根据设计需要增加或减少信号、门电路。本文参考Synopsys公司旗下的DesignWare系列电路单元,将其作为电路结构优化设计过程的初始电路单元。

3.1 具有一组通用数据输入输出端口的BSR电路

基于传统的BSR单元结构,Synopsys公司旗下DesignWare系列在边界扫描领域提供了名为DW_bc_2的BSR电路单元。作为边界扫描单元,由于其在结构上依旧保持了传统BSR电路具有一组通用数据输入输出端口和一组测试数据输入输出端口的特征,因此DW_bc_2可以作为一个系统输入单元或一个输出单元[9]。

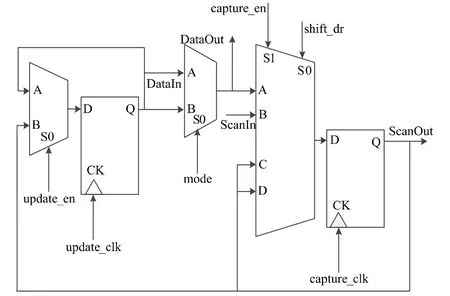

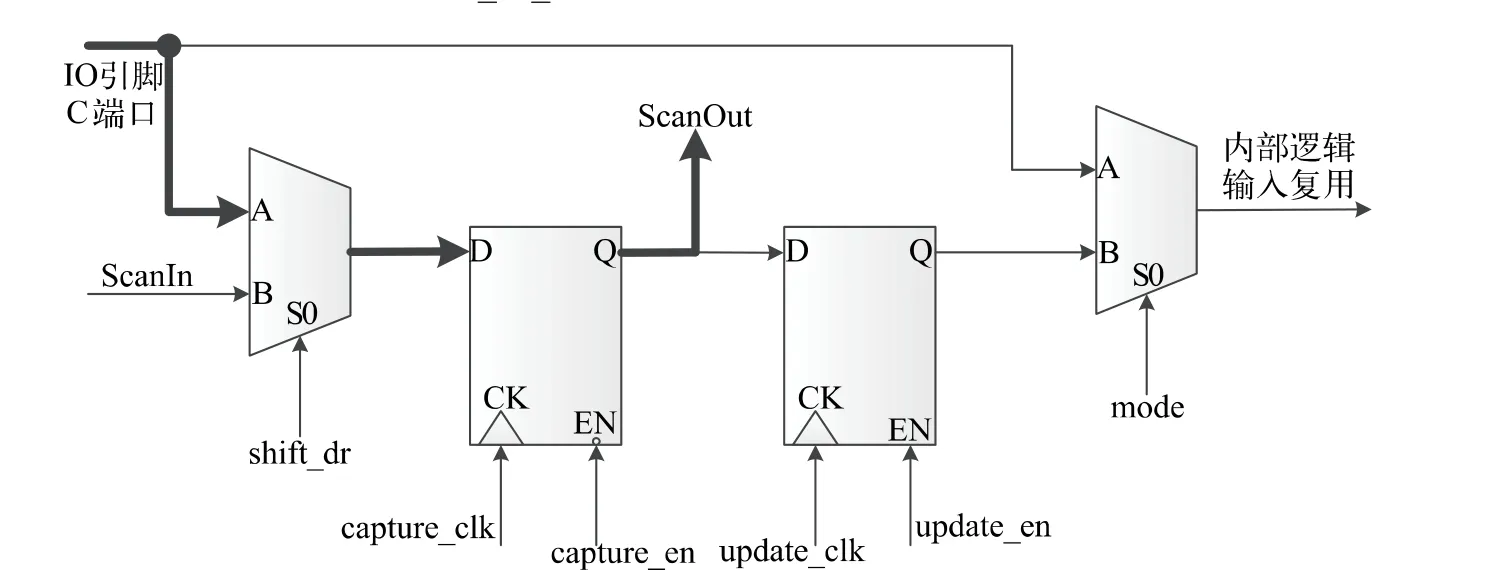

DW_bc_2单元如图4所示,在基本保持传统的BSR单元结构的基础上,额外增加了2个多路选择器,由capture_en和update_en信号作为各自的选择端,并分别作为捕获触发器和更新触发器的D端输入。DataIn和DataOut、ScanIn和ScanOut即为一组通用数据输入输出端口和一组测试数据输入输出端口。增加多路选择器的优势在于加强TAP控制器对边界扫描仿真过程的可控性。电路图中除了数据端口信号和时钟信号,其余的信号均为多路选择器的控制信号。其中shift_dr、capture_en和update_en信号都受到TAP控制器状态机状态的控制,在状态机分别处于Shift_DR、Capture_DR和Update_DR状态时,分别使能上述3个控制信号。该设计可以有效地控制仿真数据在电路中的流向,即在需要的时候,使能对应的控制信号将仿真数据传输至下一单元,从而减少不必要的数据传输,降低不必要的静态功耗。

图4 DesignWare系列DW_bc_2单元

D触发器在其输入端接入2输入多路选择器的时候,可以选择将两者合并,使得原先的D触发器具有一个使能信号,这种门电路的组合可以减少电路元件的数量,从而对整个电路的性能有所提升。所以在此基础上可以将capture_en控制下的多路选择器和capture_clk控制下的捕获触发器进行合并,形成一个带有低电平有效使能信号的D触发器。

由于单一的4输入多路选择器能够在电路性能上优于2个2输入多路选择器的串联,亦可以将capture_en和shift_dr控制下的2个2输入多路选择器合并为一个4输入多路选择器。上述2种优化电路如图5、6所示,这2种单元结构即为目前所存在的针对DW_bc_2单元的2种电路优化形式。

图5 带有低电平有效使能信号D触发器的DW_bc_2单元

图6 带有4输入多路选择器的DW_bc_2单元

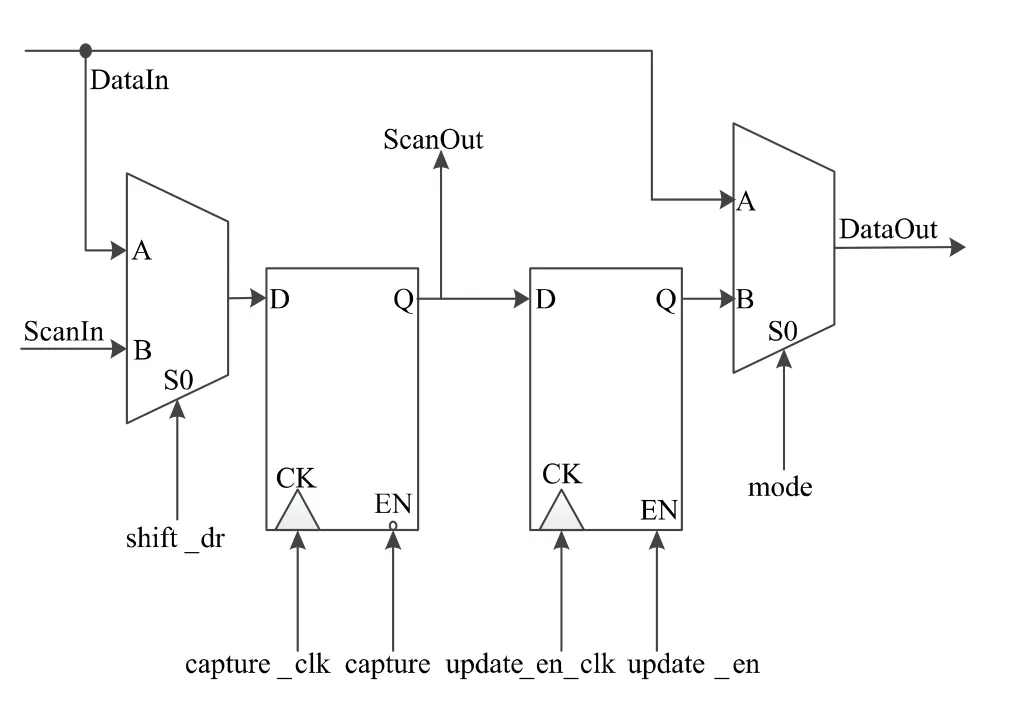

综上所述,可以基于最初的DW_bc_2单元,最大限度合并多路选择器和触发器,从而实现电路结构的最精简设计,即将capture_en、update_en控制下的多路选择器分别和capture_clk、update_clk控制下的触发器进行合并,使得原先的触发器增加使能信号,优化之后的电路如图7所示。值得注意的是,通过将原始的DW_bc_2单元经过门电路合并的方式逐步优化后,最终的电路结构即为在传统BSR单元基础上,省略触发器的复位信号,并将2个D触发器分别添加使能信号。

图7 DW_bc_2优化电路

ScanIn和ScanOut表示测试数据的输入和输出端口信号,测试数据通过ScanIn串行移位进入寄存器单元,并把数据通过ScanOut串行移出。信号DataIn和DataOut用于实现内部逻辑和IO引脚的互联。

非测试模式下,信号mode置为0,DataIn信号直接连接至DataOut,当其作为一个系统输入单元的情况下,DataIn信号与IO引脚的C端连接,DataOut信号与内部逻辑输入模块相连接;当其作为一个系统输出单元的情况下,DataIn信号与内部逻辑输出模块相连接,DataOut信号与IO引脚的I端连接。与此同时,可以利用DataIn和DataOut信号将内部逻辑OEN复用单元与IO引脚的OEN端连接,进而控制IO引脚的输入输出方向。

测试模式下,信号mode置为1,可通过使能shift_dr移位信号将测试数据从ScanIn经过capture_clk控制下的捕获触发器,通过ScanOut输出,并经由update_clk控制下的更新触发器将测试数据传递至DataOut。此时的测试数据可以用来控制IO引脚的输入输出方向,数值置为0时进行输出仿真,数值置为1时进行输入仿真。输出仿真时,DataOut信号与IO引脚的I端连接,通过IO引脚PAD端输出;输入仿真时,IO引脚PAD端的数据通过C端进入寄存器单元,从DataIn信号开始,经过shift_dr和capture_en信号的使能,通过ScanOut输出。以上2种仿真均实现了通过端口对仿真数据的可控性和可观测性。

3.2 具有2组通用数据输入输出端口的BSR电路

由上述分析可知,相同的DW_bc_2电路可以在IO引脚OEN端设置为不同的数值时实现不同的仿真功能,基于这一特点,Synopsys的DesignWare系列提供了名为DW_bc_7的BSR电路单元。此电路单元通过增加门电路和信号的数量,将DW_bc_2电路作为系统输入单元和输出单元的2种功能同时集中在1个电路中[9]。

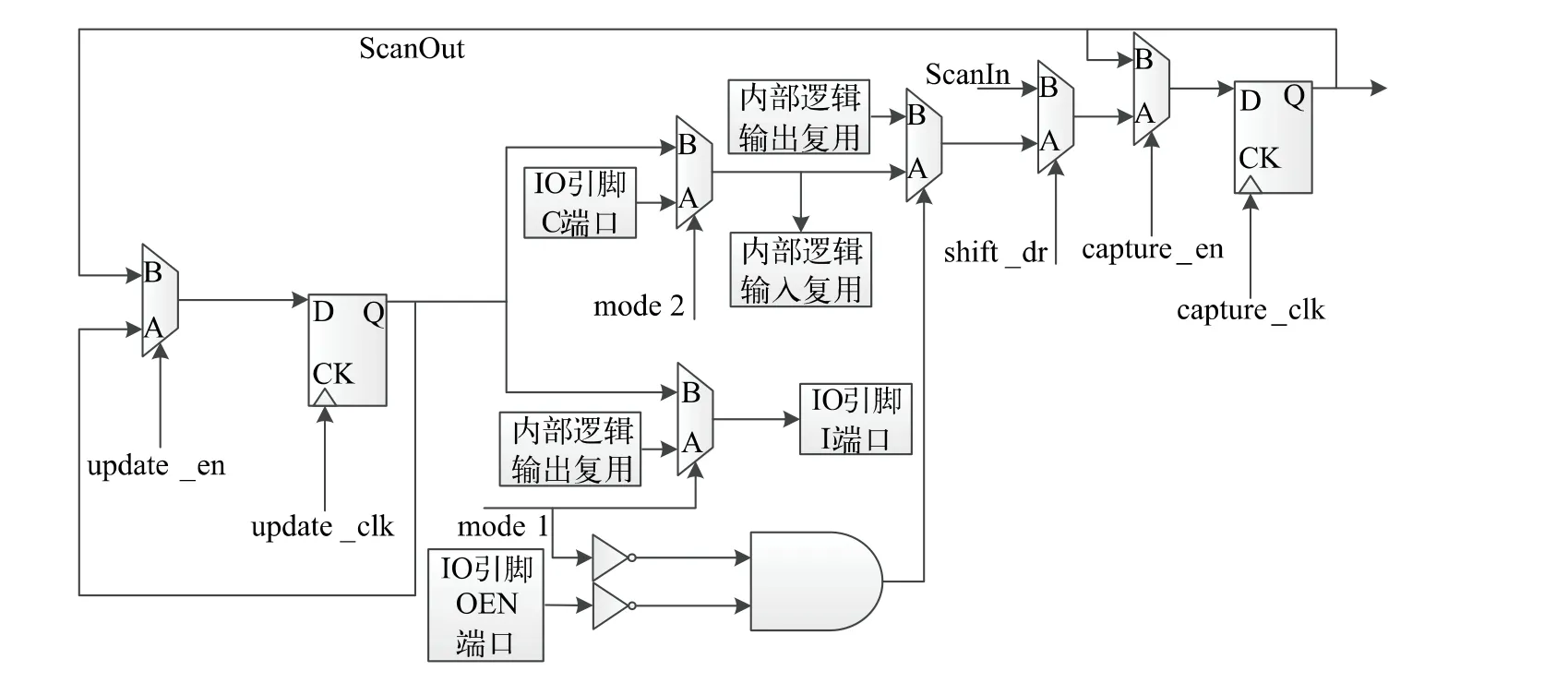

DesignWare系列DW_bc_7单元如图8所示,当mode1和mode2信号同时设置为0时,电路处于非测试模式,2个2输入多路选择器的数据通路实现了内部逻辑和IO引脚的数据交互。当mode1信号设置为1时,2输入与门的输出信号恒为0,此时电路处于测试模式,当IO引脚OEN端数值为0时,进行输出仿真,测试数据从ScanIn经过capture_clk控制下的捕获触发器,并经由update_clk控制下的更新触发器,将测试数据传递至IO引脚的I端,通过IO引脚PAD端输出;当IO引脚OEN端数值为1时,进行输入仿真,此时mode2应该设置为0,IO引脚PAD端的数据通过C端进入寄存器单元,经过shift_dr和capture_en信号的使能,通过ScanOut输出。

图8 DesignWare系列DW_bc_7单元

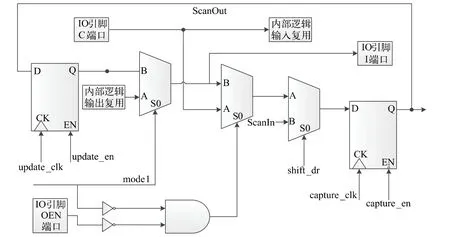

在上述结构中,无论是非测试模式还是测试模式,mode2信号始终为0,经由mode2控制下的多路选择器的这条路径下,数据流始终从IO引脚的C端至内部输入逻辑,因此可以省略该多路选择器,简化非测试模式下的数据通路。具体结构如图9所示,此种电路结构即为目前所存在的针对DW_bc_7单元的简化形式。

图9 DW_bc_7简化结构单元

通过以上的电路分析可知,测试模式下的输入功能和输出功能仿真过程彼此独立,2种仿真过程完全由IO引脚OEN端数值决定,即2种仿真过程不可能同时进行。因此根据3.1节针对DW_bc_2优化电路单元的仿真过程,可以将输入功能仿真和输出功能仿真过程的数据流向反映在电路图中,电路输出、输入仿真功能下仿真数据流向如图10、11所示。

图10 基于DW_bc_2优化电路输出仿真功能下仿真数据流向

图11 基于DW_bc_2优化电路输入仿真功能下仿真数据流向

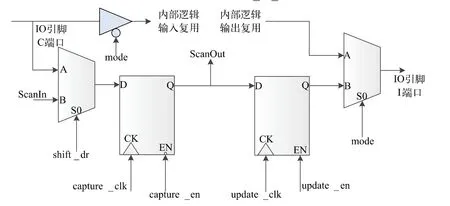

基于上述对仿真过程的电路分析,可以在DW_bc_2优化电路结构的基础上,同时保留以上2种仿真过程的数据流向,则shift_dr信号控制下的2输入多路选择器的A端应该为PAD C端口信号,而mode信号控制下的2输入多路选择器的输出端应该为PAD I端口信号。在此基础上,原先电路结构中IO引脚和内部逻辑复用单元之间的连线应被截断,分别形成内部逻辑输入复用和内部逻辑输出复用2个信号端口。

由于内部逻辑输出复用和IO引脚I端之间有mode信号控制下的2输入多路选择器单元,即可通过mode信号的配置,完成非测试模式和测试模式之间的转换。而IO引脚C端和内部逻辑输入复用之间未设置任何电路单元,这种结果导致在电路进入测试模式时,IO引脚C端仍然将数据传输至内部逻辑输入复用单元,从而引起不必要的功耗。基于此分析,可以在2个信号之间加入mode信号控制的三态门电路,当mode信号为0,电路处于非测试模式,三态门等价于缓冲器,IO引脚C端可将数据传输至内部逻辑输入复用单元,当mode信号为1,电路处于测试模式,三态门处于高阻态,即可切断2个信号之间的数据通路。DW_bc_7优化电路如图12所示。

图12 DW_bc_7优化电路

4 BSR单元性能比较

第3节所有的DW_bc_2和DW_bc_7 BSR单元电路均具有不同的电路结构,故针对门数量、面积、延迟和静态功耗这4种参数指标进行电路性能比较。为了统一工艺库和corner标准,所有门电路的各种参数指标数据均采用 TSMC工艺库中TCBN28HPCPLUSBWP35P140_SSG0P81VM40C为基准,所有数据来源均出自TSMC公司有关电路单元的性能标准参考手册TCBN28HPCPLUSBWP35P140 TSMC N28HPC Standard Cell Library Datasheet[10]。延迟指标选择传输延迟(Propagation Delay),其中需要分别考虑输入信号从高电平转化为低电平时输出信号从高电平跳变至低电平所需要的延迟时间,记为tpHL,以及输入信号从低电平转化为高电平时输出信号从低电平跳变至高电平所需要的延迟时间,记为tpLH。所有DW_bc_2和DW_bc_7 BSR单元电路中使用到的全部门电路的参数指标如表1所示。

表1 门电路参数指标[10]

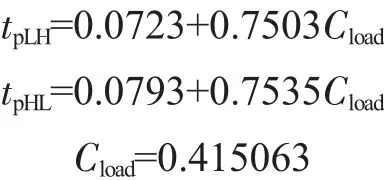

传输延迟的计算方式采用上述TSMC公司性能标准参考手册中提供的公式,以DFQD4BWP35P140(D触发器)为例,其中Cload表示门电路输出端的负载电容。DFQD4BWP35P140(D触发器)时钟端口至输出端口的传输延迟为

由于传输延迟参数只在分析输入功能或输出功能仿真过程中需要使用,故针对每种BSR单元电路,未出现在仿真过程的数据流向上的门电路,无需考虑其传输延迟。

根据电路所使用到的门电路的参数指标数据,可以将所有的DW_bc_2和DW_bc_7 BSR单元电路的参数指标进行计算。需要注意的是,由于工艺库中没有带有低电平有效使能端的D触发器,因此低电平有效使能信号的捕获触发器需要由现有的带有高电平有效使能端的D触发器和反相器组成。同时,分析电路传输延迟时需要依照仿真过程中的最长路径为基准,即输出功能仿真的最长路径从ScanIn信号至DataOut信号(或IO引脚的I端口信号),输入功能仿真的最长路径从DataIn信号(或IO引脚的C端口信号)至ScanOut信号。最终的BC单元参数指标如表2所示。

表2 BSR电路参数指标

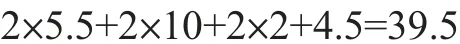

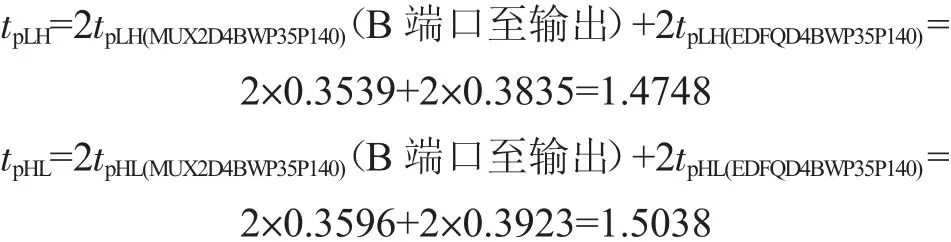

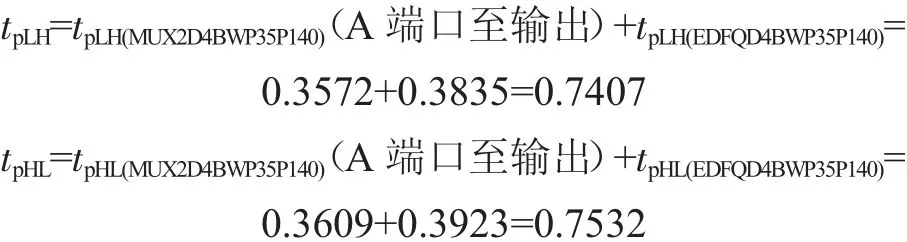

静态功耗、面积、门数量和传输延迟分别用P、A、N和t(包括tpLH和tpHL)表示。静态功耗、面积和门数量的计算方式即将电路中出现的每个元件对应的参数指标相加,传输延迟的计算方式则根据不同仿真类型的仿真最长路径,将路径下所通过的所有门电路的延迟相加。以DW_bc_7优化电路为例。

输出功能仿真最长路径:

输入功能仿真最长路径:

5 分析与讨论

根据对全部BSR单元电路的性能比较,可以看出DW_bc_2和DW_bc_7最终的优化电路在门数量、面积、静态功耗和仿真过程的传输延迟4种参数指标上性能均优于DesignWare系列最原始的DW_bc_2和DW_bc_7电路。

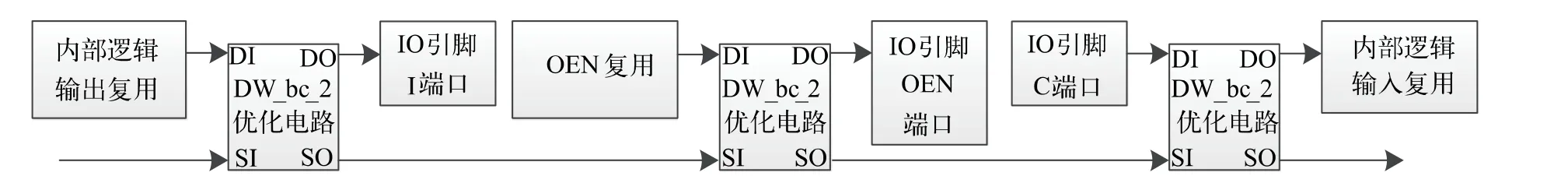

结合图1所示的BSC结构,将BSR电路的ScanIn和ScanOut端口进行前后串联,形成一条链式结构,将其置于IO引脚和内部逻辑之间,从而形成两者之间的数据互联。而通过串行测试数据输入输出端口的测试数据,可以实现对IO引脚双向功能的仿真。目前所存在的BSC电路主要有两种,一种是基于单一DW_bc_2优化电路单元的BSC(见图13);另一种是基于DW_bc_2和DW_bc_7优化电路单元的BSC(见图14)。

图13 基于单一DW_bc_2优化电路单元的BSC

图14 基于DW_bc_2和DW_bc_7优化电路单元的BSC

在基于单一DW_bc_2优化电路单元结构的BSC中,针对某一IO引脚,需要构造3个BSR单元的串联以完成IO双向功能测试。可以将中间一级的BSR设置为配置IO引脚的OEN功能,从而在串行移入测试数据的时候,将对应中间一级的测试数据置为0或1,以实现IO引脚输出或输入功能的仿真。输出功能仿真下,将对应第一级的测试数据进行随机设置,通过ScanIn端口进入BSR单元,此时数据被捕获至capture_en控制下的D触发器的输出端口,当update_en信号使能后,测试数据被更新至DataOut,进而进入IO引脚I端口,由于此时OEN为0,则测试数据可通过IO引脚PAD端口显示出来;输入功能仿真下,由于此时OEN为1,可将IO引脚PAD端口设置随机数值,该数据进入IO引脚C端口,当capture_en信号使能后,数据通过最后一级ScanOut端口输出,可实现对IO引脚数据的观测。

在基于DW_bc_2和DW_bc_7优化电路单元的BSC中,仿真过程与上述过程相同,唯一的区别是将中间一级和最后一级的DW_bc_2优化电路合并为一个DW_bc_7优化电路。DW_bc_7优化电路能够实现在一个电路单元中的IO引脚双向数据通路功能,同时仿真过程的传输延迟与DW_bc_2优化电路的相同,因此2种扫描链电路相比较,后者能够在门数量、面积和静态功耗上得到充分优化。

6 结论

本文根据对BSR单元电路的优化,从复杂的电路结构逐步到最优化电路的过程中,采用了门电路的组合,根据不同门电路的性能参数,尽可能将多个门电路所能实现的功能集中到单一的门电路上,从而在面积和功耗方面实现优化;此外,在DW_bc_7电路单元的优化中,分别针对不同功能下的仿真过程,分析出电路当中的数据流,并基于不同仿真功能彼此独立这一特点,将不同的数据流合并至一个电路单元中,并根据需要调整其他的信号,从而完成优化设计。

重新审视2种优化之后的BSR单元电路,不难看出该电路依然基本保持了传统的BSR单元电路的结构,所以整个电路结构的优化过程更大程度上是基于实际的电路应用,当2种BSR单元用于实现2个电路系统(IO引脚和内部逻辑)的互联时,就决定了原先的DataIn至DataOut这一条数据通路将会做出适当的改变。因此,在未来的电路设计中,可能出现的基于多个电路系统的数据交互,则需要在当前最优化的BSR单元的基础上,适当增加门电路和信号以满足更为复杂的电路设计要求。