一种提高SRAM型FPGA抗单粒子翻转能力的系统设计方案

董会娟 黄振

(中国电子科技集团公司第三十八研究所 安徽省合肥市 230088)

1 引言

FPGA 是集成电路中的一种半定制电路,具有体积小、容量大、性能强等优点,其中的SRAM 型FPGA 更是因为可以多次编程、资源丰富、器件密度高等特点被广泛应用于航空、航天领域[1]。但是,太空环境中存在着大量的高能粒子,而SRAM 型FPGA 断电后数据就会丢失,对空间辐射比较敏感,抗单粒子翻转的能力比较差,影响星载产品在轨工作的可靠性[2]。因此,提升基于SRAM 型FPGA 系统电路的抗单粒子翻转性能一直是研究热点。

在目前的空间应用中,提高SRAM 型FPGA 在轨可靠性的方法主要有,硬件备份、三模冗余和配置存储器刷新技术等,都有各自的缺点[3]。硬件备份增加星载单机的体积和重量,软件冗余会增加FPGA 所需的内部资源,并且无法修复单粒子事件引发的错误。配置存储器刷新技术主要面临的难点是较复杂的系统软硬件设计,同时刷新电路本身对空间辐射敏感。

本文基于国产的新一代智能抗辐照芯片,提出了一套高可靠性的SRAM 型FPGA 刷新系统设计。该设计支持回读、刷新、重载、在轨重构等功能,不仅能有效降低单粒子效应的影响,并且降低了软硬件设计的复杂度的和难度。刷新电路自身还可以通过射随信号复位,单机的抗辐照性能得到了极大的提高。

2 空间辐射效应简介

空间环境中的宇宙射线穿过物质发生相互作用被称为辐射效应。星载产品处在不同轨道,受到的辐射强度、种类及辐射时间会有所不同,一般将辐射效应分为总剂量效应、单粒子效应、位移效应和剂量效应等,其中对芯片威胁最大的是总剂量效应和单粒子效应[4,5]。随着半导体技术的进步,总剂量效应的危害也逐渐减小,单粒子效应成为影响星载产品可靠性的重要因素。

单粒子效应是指空间中各种高能粒子:中子、质子、γ射线等,进入半导体器件,使器件性能下降或损伤。单粒子效应产生的错误可分为硬错误和软错误。硬错误是由于射入器件的粒子能量很高,产生了瞬时大电流,对器件造成了永久性损毁,是不可修复的,如单粒子闩锁(SEL)、单粒子烧毁(SEB)等。软错误是指瞬态的单粒子只改变了单个逻辑状态,复位后芯片仍能正常工作,如单粒子翻转(SEU)、单粒子瞬态(SET)、单粒子功能中断(SEFI)等。通过提高元器件自身抗辐照性能可以减少硬错误发生概率,而软错误需要利用抗辐照加固技术来避免或纠正。

3 两种常用的抗单粒子翻转动态刷新方法

提高SRAM型FPGA抗单粒子翻转能力的刷新方式主要有两种,一种是基于反熔丝FPGA,另一种是基于专用刷新芯片,都是在不中断单机功能的前提下,定时完成SRAM型FPGA的动态刷新,减少SEU事件对星载产品造成的影响。

3.1 基于反熔丝FPGA的刷新方案

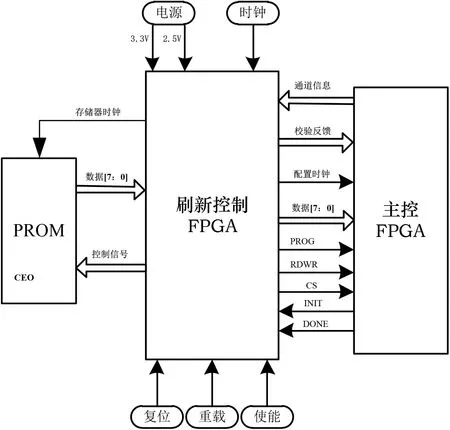

本套方案主要由存储芯片PROM、刷新控制FPGA(反熔丝FPGA)和主控FPGA 组成,总体结构设计如图1所示。主控FPGA 芯片完成对星务系统下发的高速数字信号进行处理、分发,刷新FPGA 芯片完成对主控FPGA 的刷新、重载与配置,PROM 芯片对单粒子效应不敏感,用于初始存储配置程序。反熔丝FPGA 芯片本身抗单粒子翻转能力比较强,因此刷新控制FPGA 的抗SEU 措施可以简化,但其内部使用的寄存器仍然会受到SEU 效应的影响,因此需要有针对寄存器进行的防范措施。

图1:基于反熔丝FPGA 的SRAM 型FPGA 刷新设计方案

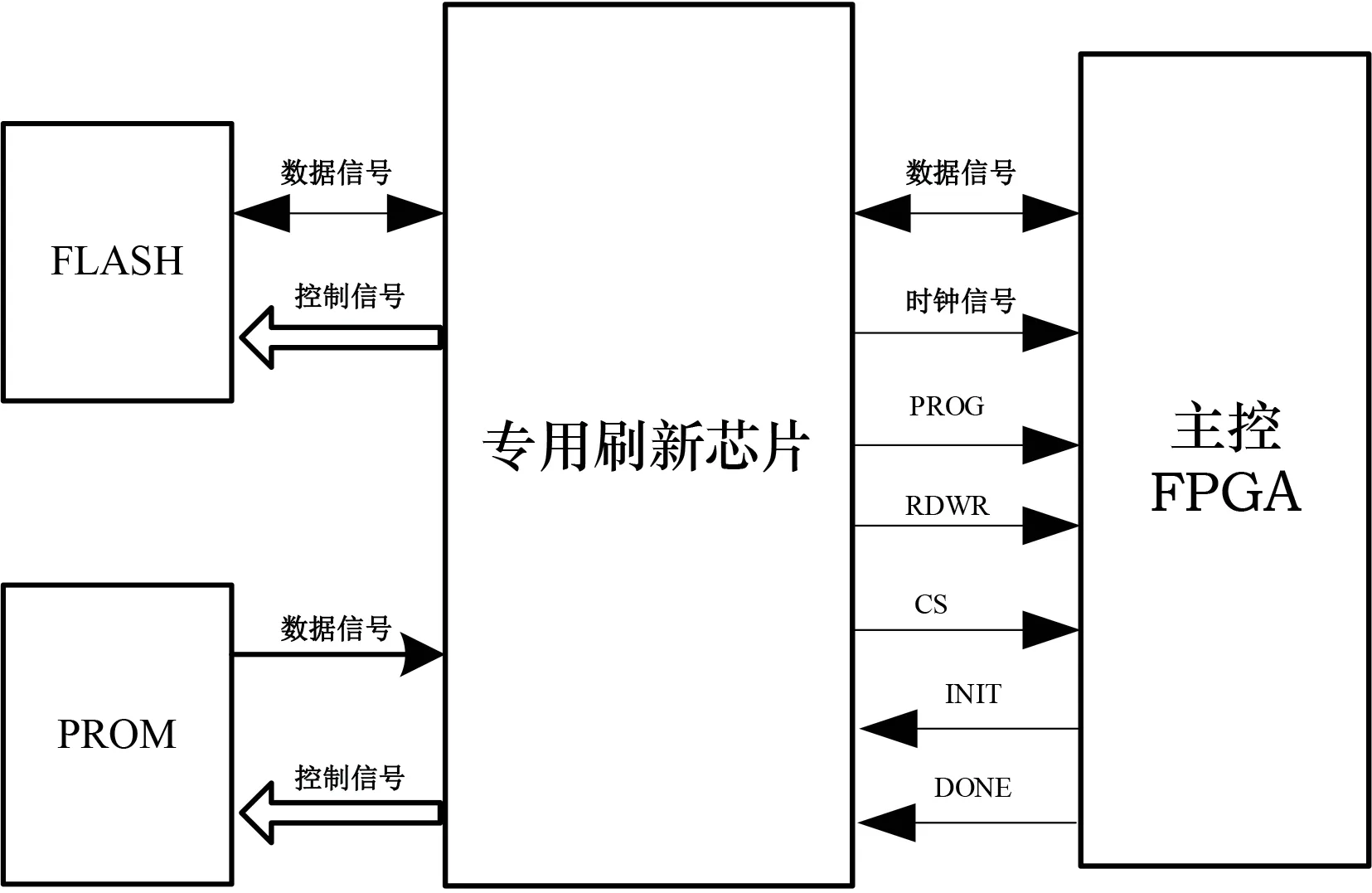

3.2 基于专用刷新芯片的刷新方案

本套方案由专用智能刷新控制芯片、主控FPGA 芯片、存储芯片PROM 和NOR 型FLASH 组成,其中NOR 型FLASH 芯片可反复擦写、编程,实现在轨重构,修正SEU事件造成的错误,完善产品软件功能,提升系统性能。完成在轨重构后,刷新芯片可设置为从FLASH 中读取配置文件定时刷新。PROM 芯片的抗单粒子能力高,用于存储初始配置文件,总体结构如图2所示。通过外部管脚或者UART命令配置刷新芯片的功能寄存器,选择芯片的基本工作模式,UART 命令配置的优先级高于管脚配置。

图2:基于专用芯片的SRAM 型FPGA 刷新设计方案

3.3 两种刷新方法对比

上文中两种刷新方法的不同主要集中在完成刷新功能的芯片种类不同,第一种使用的反熔丝FPGA 多为ATEL 公司的A54SX32A,第二种使用的专用刷新芯片为复旦微电子的JFMS01RH,具体区别如下:

(1)功耗:A54SX32A 的最大功耗为4W,按照航天产品20%降额设计要求,额定功耗为3.2W,JFMS01RH 为低功耗芯片,额定功耗为0.5W;

(2)国产化:A54SX32A 为进口器件,供货周期长,技术支持无法保障;JFMS01RH 为国产化器件,供货周期自主可控,技术支持专业及时;

(3)通用性:A54SX32A 需要用户自行编程,增加了软件设计成本,JFMS01RH 为专用刷新芯片,仅需少量外围支持电路;

(4)容错率:JFMS01RH 芯片具备实现在轨重构的功能,提高了产品在轨运行的容错率;A54SX32A 不支持此功能。

经过对比,本文选用专用刷新芯片JFMS01RH,设计一款可提高SRAM型FPGA抗单粒子翻转能力的刷新电路。

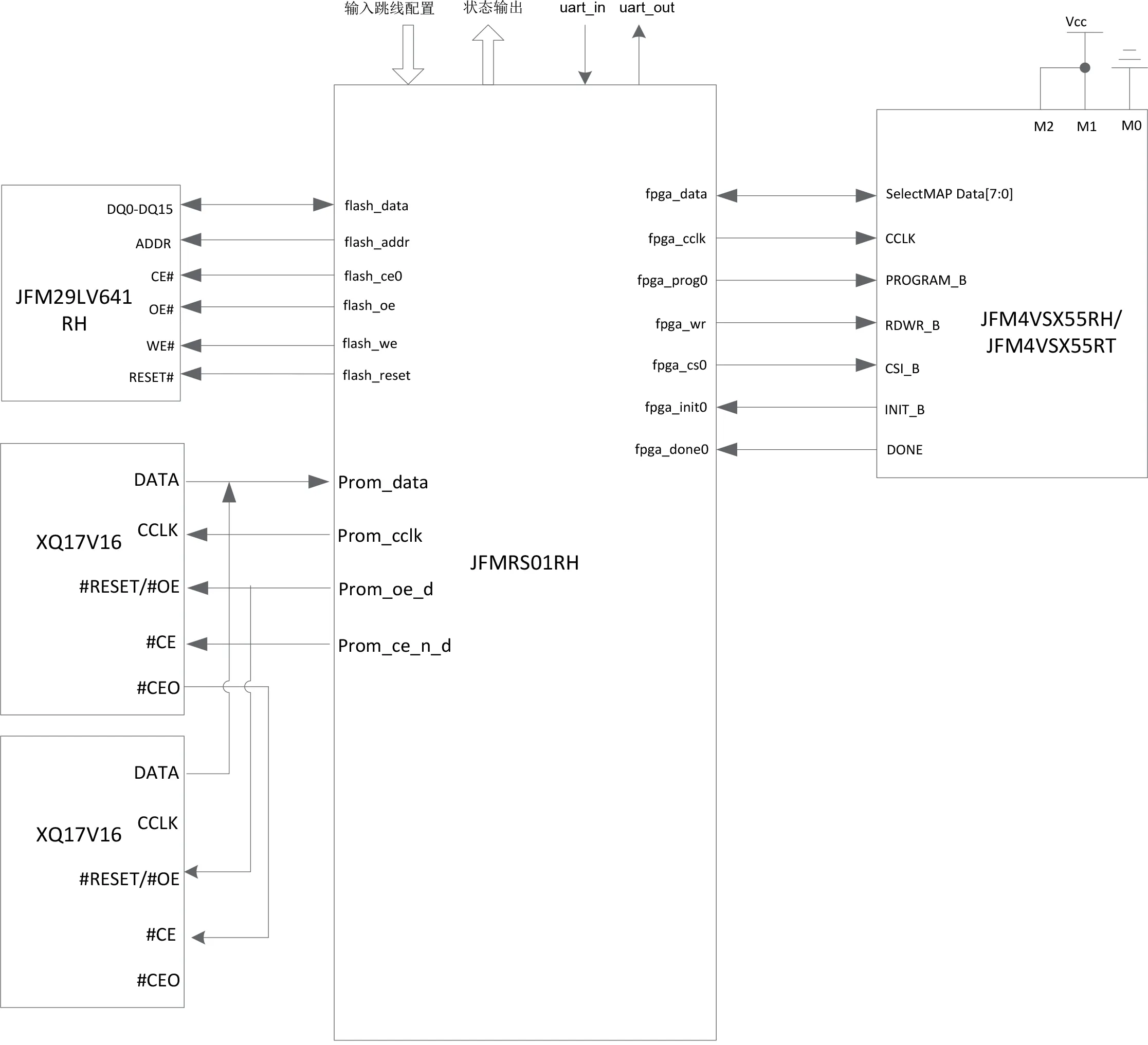

4 系统设计

本文中使用的刷新芯片是上海复旦微电子的JFMS01RH。该芯片提供了多种FLASH 接口(NOR 型FLAH 和SPI 型FLASH)、PROM 接口、UART 接口、FPGA 接口以及硬件配置接口,并且支持Xilinx 公司以及复旦微电子各主流系列FPGA,降低了系统设计的复杂度。JFMS01RH 刷新芯片支持SelectMap 接口(联合并行模式)或者Daisy Chain 接口(菊花链模式),在联合并行模式下,刷新芯片可以对FPGA 进行重载、回读或者刷新,当在菊花链模式下,刷新芯片不支持回读,只能进行重载和刷新。上电时,首先清除主控FPGA 配置区中的内容,完成主控FPGA 初始化,然后,刷新控制芯片从存储器中读取配置数据,按照指定时序发送至主控芯片的SelectMap 接口上,并监测其Done 信号是否加载成功,若信号长时间未拉高,会对主控FPGA 进行重载,若多次重载失败,对主控FPGA 进行自主复位。加载成功后,刷新芯片会读取存储器中的配置文件,通过SelectMap 接口对主控FPGA 的配置区域定时刷新,刷新频率和存储器种类的选择均由外部管脚设置。同时,刷新芯片对主控FPGA 中的FAR寄存器进行SEFI监测,若发生SEU事件,则进行重载,详细的系统设计如图3所示。

图3:系统设计方案

本套方案主要由NOR 型FLASH、PROM、刷新芯片和VCV4SX55 组成。NOR 型FLASH 芯片选用的是复旦微电子的JFM29LV641RH,大小为64M,用于存储FPGA 位流。通过UART 接口,对FLASH 芯片进行编程、全芯片擦除、扇区擦除、数据校验等操作,完成在线重构。PROM 芯片选用的是XQ17V16,其中存储的位流在使用前通过JTAG接口进行固化,之后无法更改。2 片XQ17V16 通过CE、CEO 信号完成级联。刷新芯片虽然也具有一定的抗辐照特性,但仍然存在发生单粒子事件的概率,因而为刷新芯片也设计了射随复位电路。星务平台发出2.5V 复位信号,首先利用B54AC164245 电平转换为3.3V,经过反向电路B54AC14RHF 转换为低电平后直接连接到刷新芯片的复位端。

本设计采用主、备FLASH 冷隔离的冗余设计方案,两片FLASH 中各存放一份相同的位流。工作过程中,刷新芯片首先读取主机FLASH 中的配置文件,当主机FLASH 中的位流数据发生了单粒子翻转事件,导致重载失败或者位流解析错误,会自动切换到备机。如果备机也因发生翻转导致重载不成功或位流解析错误,会自动切换到PROM,切换时间小于1us。通过遥测查询,可以定位到具体发生翻转的存储器,擦除芯片内容后,重新编程。

除了刷新功能,芯片还支持重载、回读、在线重构等功能,均可提高星载产品在轨运行的可靠性。刷新芯片会产生回读位流,并将回读位流下载到FPGA 中。FPGA 计算配置区数据的CRC 校验值,通过SelectMap 接口送出回读数据校验值,刷新芯片会将该结果与存储器中的原始配置数据帧的CRC 校验值进行对比。若发现有不匹配,则记录出错的个数,若出错的个数累加到了设定的重载阈值,则自动启动重载操作。除此之外,重载功能还有两种启动方式,一是系统上电时自动进行,二是UART 指令、OC 指令或WDT指令启动。FPGA 重载的次数可以通过访问遥测量获得。JFMS01RH 首先会发送1us 低脉冲复位信号给FPGA,等待FPGA 的INIT_B 拉高,接着从PROM 或者FLASH 中依次取出数据,按照SelectMap 接口或者Daisy Chain 模式给FPGA 提供控制信号和数据。但是重载操作会中断当前功能,然后重置FPGA 的所有数据。在轨重构功能是对FLASH 中存储的代码进行擦除和编写,完成系统维护与更新升级。在线重构的优先级比重载、回读、刷新优先级高。如果在线重构和重载、回读、刷新功能共同使用同一总线的器件。则会等待该次重载、回读、刷新结束,才能进行在线重构操作。在线重构和重载、回读、刷新功能没有使用同一总线的器件,那么在线重构和重载、回读、刷新操作可以同时进行。

JFMS01RH 芯片的工作流程如图4所示。上电后,芯片首先分析寄存器的功能,然后根据寄存器的配置结果对主控FPGA 进行加载。如果主控FPGA 加载成功,进行后续步骤,如果不成功则需要重新上电复位。当主控FPGA 加载成功后,检测芯片是否接收到在线重构命令,如果需要在线重构,则对FLASH 进行在线重构,若无,则直接对主控FPGA 的联接模式进行判断。在回读或刷新前都要对JFMS01RH 进行SEFI 检测,如果发生了回读或者刷新SEFI 错误,回读或者刷新将不会继续进行。如果sel_auto_reload 寄存器值配置成‘1’,那么退出回读或者刷新模式后,将对主控FPGA 进行重载。如果sel_auto_reload 寄存器值配置成‘0’,那么退出回读或者刷新后不会进行其他操作,直到下次的回读或者刷新继续检测芯片是否发生SEFI。

图4:JFMS01RH 刷新芯片的工作流程

5 结论

空间辐射对航天器在轨可靠性有着极其重要的影响,SEU 和SET 造成的影响更是会对航天电子系统造成不可修复的。本文对比了两种常见的星载产品刷新设计方案,最后基于国产刷新控制芯片,提出了一套完整的抗单粒子翻转及卫星在轨重构的系统设计方案,有效提高了SRAM 型FPGA对单粒子效应故障的容错能力,为航天电子系统的可靠性设计提供了参考。