基于MIPI D-PHY 规范的低速接收电路设计

张自豪,赵建中,周玉梅

(1.中国科学院 微电子研究所,北京 100029;2.中国科学院大学,北京 100049)

随着移动互联网时代的到来以及智能手机、平板电脑和可穿戴式电子产品的高度普及,消费者们普遍提高了对电子产品在图像、视频显示方面的需求[1-3]。MIPI 串行显示接口(Display Serial Interface,DSI)规范是一种高速串行显示接口协议[4],因其功耗低、抗干扰能力强等特点,目前已成为全高清微显示接口领域的主流应用协议[5-6]。

物理层(Physical Layer)是DSI协议的最低层次,规定了发送接收线路的电学特性以及时钟通道和数据通道的时序关系[7]。D-PHY 规范[8]是一种常用的物理层规范(最初D-PHY 单通道传输速率为500 Mbps,500 对应的罗马数字为D)。D-PHY 主要传输模式有高速(High Speed,HS)模式和低速(Escape)模式[9-11]。低速模式是D-PHY的一种特殊工作模式,其特点是无端接[12]、低速、可间断传输,是一种异步通信电路[13]。DPHY规范本身并没有提供低速下的接收时钟,文献[7]采取本地外挂40 MHz的异步时钟来实现低速数据的采样。如何实现D-PHY 低速工作模式下的异步时钟以及低速模式下的时序控制要求,是该文的研究重点。

1 电路架构

1.1 D-PHY架构

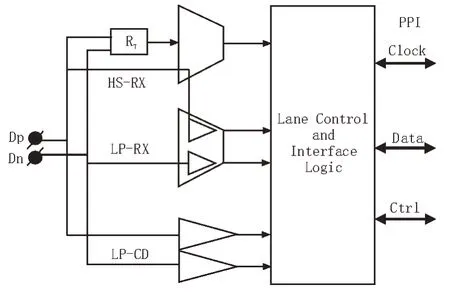

D-PHY 作为DSI 协议的物理连接层,有主端和从端之分。从端D-PHY 是一个数模混合电路,主要功能是通过差分Dp、Dn 传输线路,接收从主端发送过来的串行比特流(Bit)数据,将模拟信号转换为数字信号,解串出并行有效数据,再将数据以字节(Byte)的形式传给协议上层[14]。D-PHY 的模拟电路部分主要实现串行比特流的接收以及高速时钟的恢复,数字电路部分主要实现对每个通道的状态和时序控制,以及对低速数据进行解码和高速数据的帧头检测。从端D-PHY 的电路架构如图1 所示。其中D-PHY 的输出信号为PHY 协议接口(PHY Protocol Interface,PPI)信号。

图1 从端D-PHY电路架构

1.2 D-PHY低速接收模式

1.2.1 低速模式电路架构

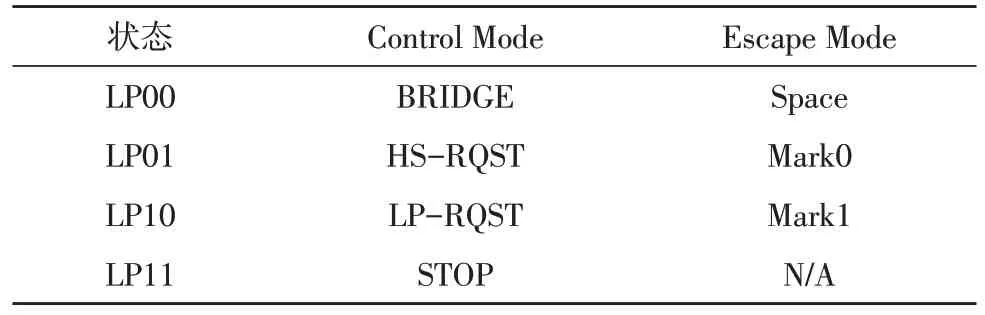

低速模式主要传输DSI 协议规定的低速命令和状态信息[12],并且在D-PHY 进入高速模式之前,需要低速模块电路提前工作,将高速驱动电路使能以及端接电路使能打开,才能建立稳定可靠的高速传输连接。低速模式下,D-PHY 的最高数据传输速率不超过10 Mbps。差分传输线Dp 和Dn 是单端信号(0~1.8 V),Dp和Dn不同的逻辑电平可以组合成4种状态:LP00、LP01、LP10和LP11,D-PHY规范将这4种组合编码成不同的通道状态,如表1 所示。

表1 D-PHY通道状态

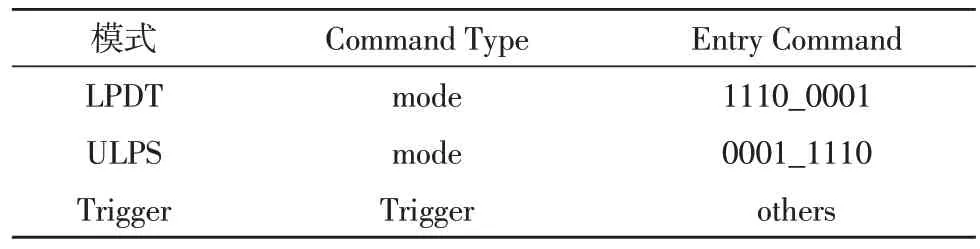

整个低速接收电路可以划分为模拟前端电路和数字电路两部分,如图2 所示,模拟前端进行模拟单端信号Dp 和Dn 的有效接收,并输出正确的逻辑电平给数字电路。数字电路通过Dp 和Dn 的逻辑电平值,进行不同的时序控制和逻辑组合。该文主要关注低速接收电路的数字电路设计。

图2 低速接收电路架构

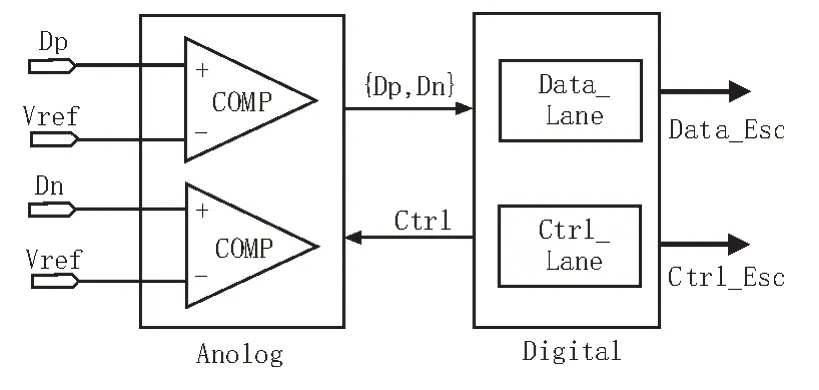

1.2.2 低速模式接收时序

通过检测Dp、Dn 线路上的逻辑电平,D-PHY 首先通过一段引导码进入低速模式,D-PHY 规范规定的低速模式引导码为:LP11→LP10→LP00→LP01→LP00。之后,D-PHY 根据不同的8 比特进入命令码(Entry Command)进入到不同的低速模式,低速模式可细分为3 种模式:低速传输模式(Low-Power Data Transmission,LPDT)、超低功耗模式(Ultra-Low Power State,ULPS)和复位模式(Reset-Trigger)。对应关系如表2 所示。

表2 进入命令码

低速模式下的8 比特进入命令码和8 比特低速数据是通过对Dp、Dn 逻辑电平进行空格-独热码(Spaced-One-Hot)解码得到的。空格独热码是一种特殊的编码方式,它使用2 组LP 状态值来表示数据“0”和数据“1”,每个Mark 状态紧邻一个Space 状态,即Mark1(LP10)和Space(LP00)则表示数据“1”,Mark0(LP01)和Space(LP00)则表示数据“0”。

2 电路实现

2.1 低速时钟生成

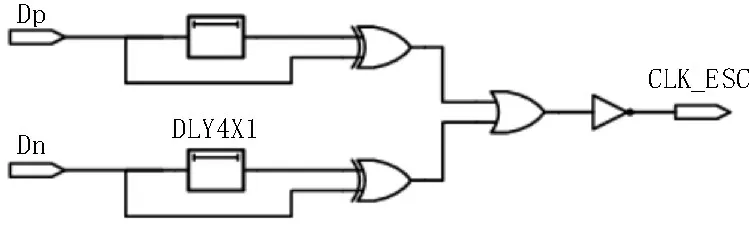

D-PHY 在低速模式下,是一种异步通信模式,数据通道的传输不依赖于时钟通道[12]。根据引导码和Spaced-One-Hot 的编码特点,设计出了一种低速模式异步时钟生成电路,可用来控制D-PHY 的状态控制和低速数据传输。在低速模式下,两次线路状态传输之间会发送一次Bridge 状态或者Space 状态,其值都为LP00;通过调用工艺库里的标准延时单元DLY4X1,分别将Dp、Dn 延时后的信号Dp’、Dn’和Dp、Dn 相异或得到CLK_P 和CLK_N,再将CLK_P 和CLK_N 相或再反相得到低速异步时钟CLK_ESC,电路设计如图3 所示。

图3 低速异步时钟生成

2.2 控制通路和数据通路

低速模式控制通路的主要功能是保证D-PHY通过引导码进入正确的工作模式,由D-PHY 低速状态机(Finite State Machine,FSM)来控制,通过检测不同的线路电平进入不同的状态,状态转移图如图4所示。

图4 D-PHY低速状态机状态转移图

D-PHY 复位结束之后,状态机处于STOP 状态,打开低速接收机进入线路电平检测模式,之后根据不同的引导码进行状态跳转,其中ESC_CMD 为进入命令码判断状态,8比特进入命令码由数据通路给出;低速模式下,当再次检测线路电平为LP11时,D-PHY回到STOP 状态,等待下一次低速传输。

数据通道进行Spaced-One-Hot 的解码,输出进入命令码,并且在LPDT 模式下输出8 比特的低速数据。数据通道的实现电路如图5 所示,State_Ctrl 为状态机控制模块,在ESC_CMD 和LPDT 状态下进行计数和Spaced-One-Hot 解码,分别由Data_Cnt 和Data_Decode 模块实现,其中Data_Cnt 是一个4 位二进制计数器,控制Data_Decode 模块,实现8 比特的数据输出。

图5 控制通路和数据通路电路图

3 电路仿真和结果分析

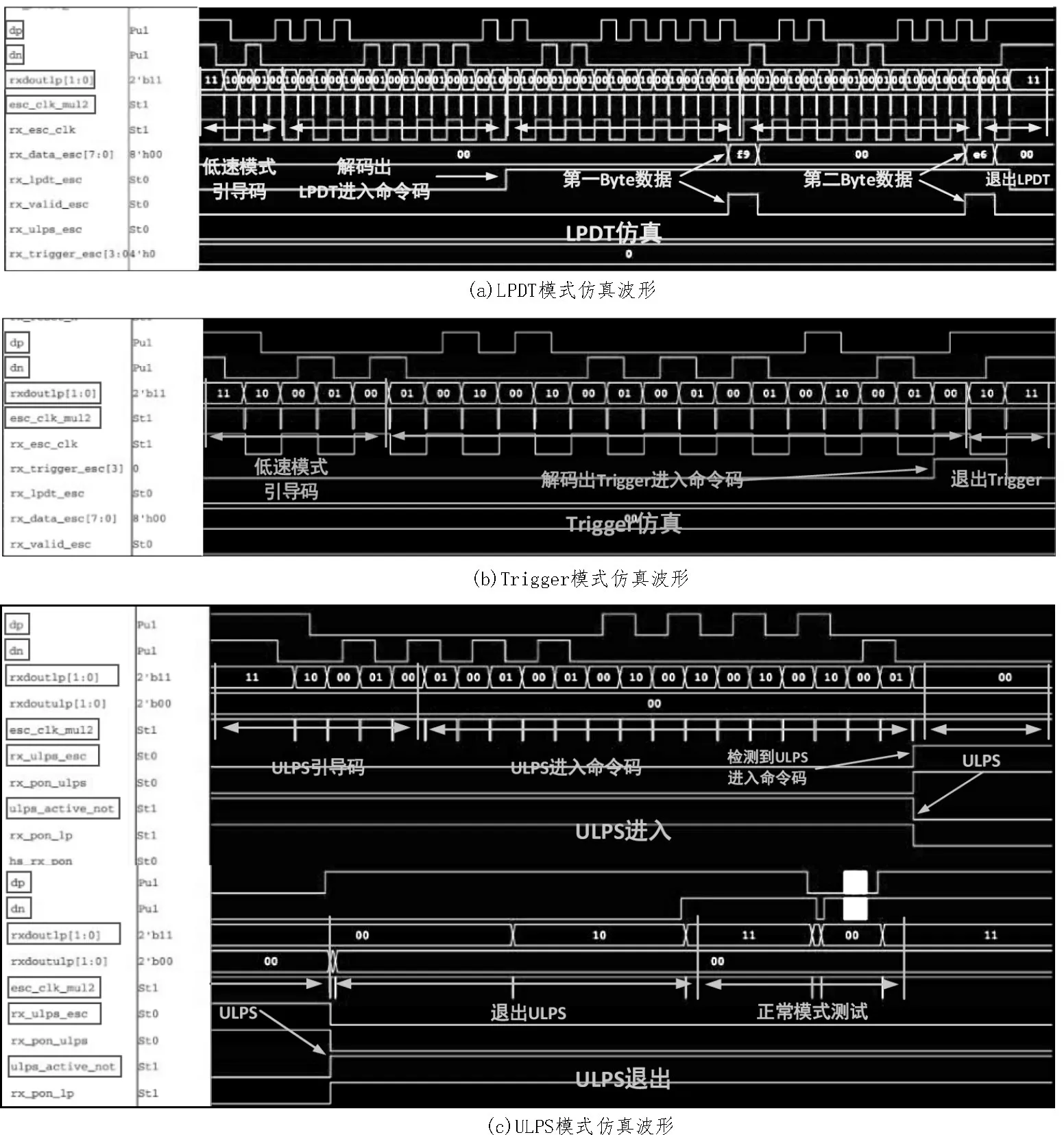

该设计搭建了D-PHY 模拟电路的模型,搭建Testbench 平台对D-PHY 低速接收电路进行了电路前端仿真。测试用例为LPDT 模式、Trigger 模式和ULPS 模式的进入与退出,仿真结果如图6 所示。结果表明,D-PHY 低速接收电路能够正确检测线路电平,根据不同的引导码进行各个模式之间的切换,LPDT 模式下Spaced-One-Hot 解码正确。下面具体分析每个模式的仿真过程。

LPDT 模式仿真波形如图6(a)所示,从端DPHY模拟层模型正确接收Dp 和Dn 数据,转成2 bits rxdoutlp[1:0]输出给数字层。使用该文提出的异步数据采样时钟esc_clk_mul2,数字层正确采样低速模式引导码、以Spaced-One-Hot 解码出8 bits LPDT 模式进入命令码,拉高LPDT 模式进入标志信号rx_lpdt_esc,之后接收LPDT 有效数据,每接收1 byte数 据rx_data_esc[7:0],拉高rx_valid_esc 信号;LPDT数据接收完毕后,检测到LP10 和LP11,退出低速模式。PPI接口信号行为符合DPHY 1.1规范,测试用例符合DPHY CTS 1.1 规范[15-16],LPDT 模式仿真波形正确。

Trigger 模式仿真波形如图6(b)所示,从端DPHY模拟层模型正确接收Dp 和Dn 数据,转成2 bits rxdoutlp[1:0]输出给数字层。使用该文提出的异步数据采样时钟esc_clk_mul2,数字层正确采样低速模式引导码、以Spaced-One-Hot 解 码出8 bits Trigger 模式进入命令码,将Trigger 模式进入标志信号rx_trigger_esc[3]拉高,之后检测到LP10 和LP11,退出低速模式。PPI 接口信号行为符合DPHY 1.1 规范,测试用例符合DPHY CTS 1.1 规范,Trigger 模式仿真波形正确。

ULPS 模式仿真波形如图6(c)所示,从端DPHY模拟层模型正确接收Dp 和Dn 数据,转成2 bits rxdoutlp[1:0]输出给数字层。使用该文提出的异步数据采样时钟esc_clk_mul2,数字层正确采样ULPS 模式引导码,解码出ULPS 进入命令码之后,拉高rx_ulps_esc,拉低ulps_active_not(低有效),进入ULPS模式。ULPS 模式下,当检测到线路电平为LP10 和LP11 时,拉低rx_ulps_esc,拉高ulps_active_not(低有效),退出ULPS 模式;退出ULPS 后,从端DPHY 需立刻能够进行数据的接收,才可认为完全退出了ULPS模式,故退出ULPS 后,立刻进行了一次接收测试。PPI接口信号行为符合DPHY 1.1规范,测试用例符合DPHY CTS 1.1 规范,ULPS 模式仿真波形正确。

图6 LPDT、Trigger、ULPS模式仿真

基于SMIC 0.18 μ m 工艺库,使用Synopsys Design Compiler(DC)工具对该电路进行逻辑综合,典型工艺角下,整体电路的面积为9 616.62 μm2,整体功耗为231.3 μW。所设计电路能够满足D-PHY 1.1 规范低速模式下最高10 Mbps 的数据速率。

4 结论

文中提出了一种基于MIPI D-PHY 规范的低速模式接收电路,该电路解决了D-PHY 低速模式下的异步时钟问题,具有Spaced-One-Hot 解码功能,支持LPDT、Trigger 和ULPS 模式的进入和退出,最高数据传输速率符合MIPI D-PHY 1.1 规范。