视频压缩控制系统优化

李 拓,张贞雷*,邹晓峰,刘同强,周玉龙,魏红杨,王贤坤,展永正

(1.高效能服务器和存储技术重点实验室,山东 济南 250101;

2.山东云海国创云计算装备产业创新中心有限公司,山东 济南 250101)

0 引 言

针对视频流业务具有连续性传输、数据量大、对实时性和可靠性要求高等特点,利用现有的计算机网络进行视频传输,将有效地降低监控系统的成本;同时,网络还需要用来传输大量的其他数据,并不是只传输视频数据,因此必须对图像数据进行高效压缩以降低需要传输和存储的数据量[1]。视频压缩技术是视频处理的基础[2]。传统视频压缩控制方案是将采集到的RGB原始图像[3],经过色彩空间转换为YUV格式之后存储到双倍速率同步动态随机存储器(Double Data Rate SDRAM,DDR),视频压缩IP核(Intellectual Property core,IP core)读取YUV数据,完成压缩之后再存储到DDR,供上层网络驱动读取。IP核是指用于专用集成电路(Application Specific Integrated Circuit,ASIC)或者可编辑逻辑器件(Field Programmable Gate Array,FPGA)的逻辑块或数据块。将这些在数字电路中常用但比较复杂的功能块设计成可修改参数的模块,可以让有需求的用户直接调用这些模块。本文用到的视频压缩IP 核,指的是支持H.264[4]/JPEG[5]等各种压缩格式的IP核。视频压缩流程包括帧内预测/帧间预测、DCT变换、量化及熵编码等步骤。

传统的视频压缩方案存在频繁的数据读写占用大量系统总线带宽[6]等弊端,因此,本文对传统视频压缩控制系统进行优化,设计了数据预处理模块,减少了色彩空间转换的数据量,降低了功耗;设计了BLOCK转换模块,极大地减少了视频压缩IP核对外部DDR的访问,降低了系统带宽;同时设计了动态+静态的组合丢帧机制,具有很强的灵活性,增强了对不同DDR容量的适配性,在不影响远端显示的需求下,进一步降低压缩视频的数据量,提高整体性能。

1 视频压缩控制系统硬件设计

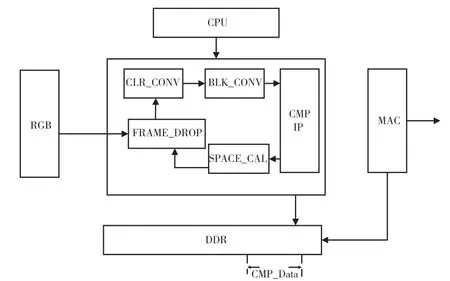

本文设计的视频压缩控制系统,其硬件架构如图1所示。

图1 视频压缩控制系统硬件框图

本文的视频压缩控制系统主要由5个子模块组成,分别是FRAME_DROP(丢帧模块)、DATA_PRE_PRC(数据预处理模块)、BLK_CONV(BLOCK转换模块)、SPACE_CAL(空间计算模块)以及CMP IP(视频压缩IP核,可支持H.264、JPEG等格式)。

工作流程简述如下:原始VGA信号(RGB格式)首先经过FRAME_DROP(丢帧模块)接收软件的配置和SPACE_CAL(空间计算模块)子模块的计算结果,对当前视频进行丢帧操作;其次进行数据预处理,根据当前压缩格式,对需要丢弃的UV数据不进行色彩空间转换和分辨率调整,对需保留的数据从RGB格式转换为YUV格式;再次,将YUV格式的数据输入至BLOCK_CONV,进行BLOCK转换,以BLOCK宏块的形式输入到视频压缩IP核,进行数据压缩;最后将压缩完成的数据写入至DDR指定的空间,上层软件通过网络将压缩后的视频信号传输到远端[7],在远端解码显示。

1.1 丢帧子模块

丢帧子模块的功能是在不影响远端显示控制的基础上,综合考虑本地DDR空间及网络带宽、系统性能等因素,对原始的视频数据进行丢帧处理。减少一部分视频帧,并不会影响远程显示的正常功能,因为远程主要是监控操作,并不需要非常高清晰的显示,因此可以进行丢帧处理。

丢帧可以减少视频压缩数据量,也就减少了存放压缩数据所需要的DDR空间,同时视频压缩控制系统与DDR的数据交互相应减少,间接提高了系统性能。同时,丢帧子模块的动态功耗将随之降低,也就降低了整体系统的功耗。

丢帧子模块采用的是静态丢帧+动态丢帧的组合丢帧策略。静态丢帧是指丢帧子模块接收软件配置的丢帧率进行丢帧;动态丢帧是指模块接收SPACE_CAL的输出结果进行丢帧,这个结果是根据DDR中系统划分的存放完成压缩之后的视频数据CMP_Data(compress data)空间的剩余空间大小计算得出的动态丢帧率,这样可以保证CMP_data空间不至于因为太满而造成数据溢出,进而导致远程显示的视频数据错乱,引起界面偏移或者花屏现象。丢帧子模块架构如图2所示,具体处理流程 如下。

图2 丢帧子模块架构

CFG是丢帧子模块的内部寄存器,接收软件下发的配置,该配置信息为静态丢帧率Static_Drop_Rate,如软件可配置静态丢帧率的值为1/2。值得注意的是,这个静态丢帧不是绝对的静态,也就是说,上层软件可以根据系统整体运行情况实时更新配置。Dynamic_Drop_Rate是后级SPACE_CUL的输出结果,指的是动态丢帧率,如SPACE_CUL的计算结果可能为1/3。值得注意的是,这个动态丢帧率是在静态丢帧率的基础上实时更新的。Drop_Process子模块接收RGB格式的视频源数据(RGB_Data)和分辨率信息(Resolution),然后根据Static_Drop_Rate和Dynamic_Drop_Rate的值进行实时丢帧,其组合丢帧率为1-(1-Static_Drop_Rate)× (1-Dynamic_Drop_Rate)。

系统利用分辨率信息得到当前帧的总数据量,以帧为单位对输入视频数据进行分割,然后进行丢帧操作。丢帧的原则是尽量均匀,以保证保留的视频帧尽可能地保留原始视频信息。系统将未丢弃的帧数据(RGB_Data_Rsv)传递至后级Data_Pre_PRC数据预处理模块,根据转换矩阵进行色彩空间转换[8],将数据从RGB格式转换为YUV格式,然后传输给后级模块处理。

1.2 数据预处理模块

数据预处理模块首先根据当前软件配置的压缩格式(常见的有YUV444/YUV422/YUV420),提前预判出不需要进行色彩空间转换的UV数据。传统方案需要针对每一个像素点的RGB信息,根据矩阵转换公式转换成YUV格式,然后再根据压缩格式的不同,对部分UV数据进行丢弃。本文对传统方案进行创新修改,根据软件配置的压缩格式,对当前压缩格式下要被丢弃的UV数据直接不进行格式转换,即不生成要被丢弃的UV数据。本方案与传统方案相比,在YUV420格式下将节省50%的乘法和加法操作,YUV422格式下将节省25%的乘法和加法操作,极大地降低了该子模块的功耗。数据预处理模块逻辑架构如图3所示。

图3 数据预处理模块框图

该子模块的CFG模块接收软件的配置,配置的内容是当前压缩格式(YUV444/YUV422/YUV420等)。L_R_DET(Line_Row_Detection)是行列号检测模块,能够根据当前分辨率判断出当前像素点的行/列号信息。RSL_ADJ是分辨率调整模块(注:本文以JPEG压缩格式为例,H.264或其他格式则采取相应操作),功能是将非8整除的分辨率调整为可以被8整除(YUV444/YUV422格式时调整为8的整数倍,而YUV420格式时则需调整为16的整数倍,原因见1.3节分析)。Data_Drop模块则根据软件配置的压缩格式以及分辨率调整之后的信息(RSL_ADJ模块的输出结果),对RGB2YUV色彩空间转换模块进行控制:根据RSL_ADJ模块的计算结果,对需要舍弃的行/列的像素点,直接不进行RGB2YUV格式的转换;对不需要舍弃的行/列像素点,根据压缩格式的配置的不同进行不同的处理。

(1)对于YUV444格式,根据RGB数据,计算得到每一个像素点的YUV数值。

(2)对于YUV422格式,计算每一个像素点的Y值,同时只计算偶数列的U值和V值,或者是奇数列的U值和V值,只要保证两个Y值能对应一组相邻的U/V值即可。

(3)对于YUV420格式,计算每一个像素点的Y值,同时只计算偶数行的偶数列的U值和V值,也可以是偶数行的奇数列、奇数行的偶数列、奇数行的奇数列,需保证4个Y数据共用一组相邻的U/V 数据。

RGB2YUV模块根据色彩空间矩阵转换公式[9]和Data_Drop的控制信息,计算得到YUV数据。

1.3 BLOCK转换模块

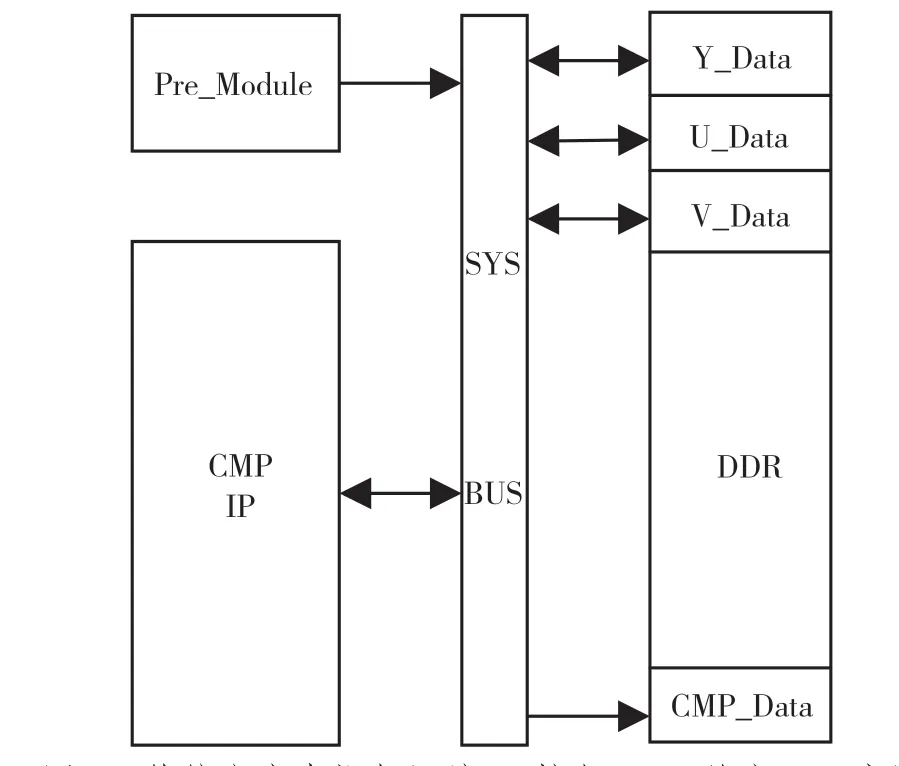

传统方案中,DDR用来暂时存储采集到的还来不及处理的图像信息,这个过程叫帧缓存。之后系统再把DDR中的图像信息传送到处理模块中进行处理。视频压缩IP核内部集成ADDR_GEN,即地址产生模块,根据YUV压缩格式,按照BLOCK宏块的顺序去读YUV数据的地址。而这些Y/U/V数据需提前准备好,在DDR中分别存放,然后将Y/U/V 的首地址,配置给视频压缩IP核。传统方案中视频压缩IP核与DDR的交互过程如图4所示。

图4 传统方案中视频压缩IP核与DDR的交互示意图

传统方案中,前级模块Pre_Module通过系统总线将Y/U/V数据分别存储在DDR的不同地址[10],同时软件将Y/U/V数据的首地址配置给CMP IP。CMP IP内部的地址产生模块通过系统总线,按照BLOCK宏块的顺序分别去读Y_Data,U_Data,V_Data。CMP IP压缩完成的数据通过系统总线写入到DDR指定的空间。

由此可见,传统方案会大量占用系统总线,需要先将源视频源写进DDR,然后再从DDR中读出,而未压缩的视频数据量巨大,频繁的数据读写占用了大量的系统总线带宽[6],这将给系统总线带宽带来巨大压力,降低整体系统性能。

为此,本文对传统方案进行改进优化,主要思路是,不关心CMP IP发出的读Y/U/V的地址(这个地址顺序就是BLOCK输入的顺序),而是设计BLOCK转换模块,按照图5的顺序,直接将Y/U/V数据传递给CMP IP,这样就避免了源视频数据先写入DDR再从DDR中读出的弊端,极大降低了系统总线的带宽压力[11],而且节省了传统方案中用于存储视频源Y/U/V数据的DDR空间,进一步提高了系统整体性能。CMP IP支持YUV444/YUV422/YUV420格式的压缩。

图5中的一个方框是8×8个像素点[12],也就是本文的BLOCK宏块。BLOCK转换模块的逻辑结构如图6所示。

图5 BLOCK转换模块输入到CMP IP的顺序格式

图6 BLOCK转换模块框图

BLOCK转换模块接收前级模块调整后的分辨率信息和YUV数据,L_R_DET(行列号检测子模块)计算得到当前输入的YUV数据的行/列号,CFG子模块接收软件的配置,配置的内容是压 缩 格 式(YUV444/YUV422/YUV420)。BLOCK转换模块按照软件配置的压缩格式(YUV444/YUV422/YUV420)将按行输入的帧数据存到FIFO阵列,然后根据压缩格式,按照图5的BLOCK顺序读取FIFO阵列。FIFO阵列包括16个Y_FIFO(用于存取Y数据,分别记作Y_FIFO_0,…,Y_FIFO_15),16个U_FIFO(用于存取U数据,分别记作U_FIFO_0,…,U_FIFO_15)以及16个V_FIFO(用于存取V数据,分别记作V_FIFO_0,…,V_FIFO_15)。

FIFO_WR_CTRL(FIFO阵列写控制)按照YUV444/YUV422/YUV420压缩格式,将输入的YUV数据写到FIFO阵列。前级的数据预处理模块已经根据压缩格式进行了数据预处理,本子模块的处理流程如下。

YUV444压缩中Y数据的写顺序为:将第0/8/16/24…行的Y数据写进Y_FIFO_0,将第1/9/17/25…行的Y数据写进Y_FIFO_1,……,将第7/15/23/31…行的Y数据写进Y_FIFO_7。

YUV444压缩中U数据的写顺序为:将第0/8/16/24…行的U数据写进U_FIFO_0,将第1/9/17/25…行的U数据写进U_FIFO_1,……,将第7/15/23/31…行的U数据写进U_FIFO_7。

YUV444压缩中V数据的写顺序为:将第0/8/16/24…行的V数据写进V_FIFO_0,将第1/9/17/25…行的V数据写进V_FIFO_1,……,将第7/15/23/31…行的V数据写进V_FIFO_7。

YUV422压缩格式中Y数据的写入顺序为:将第0/16/32…行的Y数据写进Y_FIFO_0,将第1/17/33…行的Y数据写进Y_FIFO_1,……,将第15/31/47…行的Y数据写进Y_FIFO_15。

YUV422压缩格式中U数据的写入顺序为:将第0/16/32…行保留的U数据写进U_FIFO_0,将第1/17/33…行保留的U数据写进U_FIFO_1,……,将第15/31/47…行保留的U数据写进U_FIFO_15。

YUV422压缩格式中V数据的写入顺序为:将第0/16/32…行保留的V数据写进V_FIFO_0,将第1/17/33…行保留的V数据写进V_FIFO_1,……,将第15/31/47…行保留的V数据写进V_FIFO_15。。

YUV420压缩格式中Y数据的写入顺序为:将第0/16/32…行的Y数据写进Y_FIFO_0,将第1/17/33…行的Y数据写进Y_FIFO_1,……,将第15/31/47…行的Y数据写进Y_FIFO_15。

YUV420压缩格式中U数据的写入顺序为:将第0/16/32…行保留的U数据写进U_FIFO_0,将第2/18/34…行保留的U数据写进U_FIFO_1,……,将第14/30/46…行保留的U数据写进U_FIFO_7。

YUV420压缩格式中V数据的写入顺序为:将第0/16/32…行保留的V数据写进V_FIFO_0,将第2/18/34…行保留的V数据写进V_FIFO_1,……,将第14/30/46…行保留的V数据写进V_FIFO_7。

FIFO_RD_CTRL(FIFO读控制)按照压缩格式的配置,参照图5的格式去读FIFO阵列,将读出的数据输入到CMP IP。

YUV444压缩格式中,参照图5的顺序,依次读8次Y_FIFO_0,Y_FIFO_1,…,Y_FIFO_7,依次读8次U_FIFO_0,U_FIFO_1,…,U_FIFO_7,依次读8次V_FIFO_0,V_FIFO_1,…,V_FIFO_7,然后再去读Y_FIFO,依次循环。

YUV422压缩格式中,按照图5的顺序,依次读8次Y_FIFO_0,Y_FIFO_1,…,Y_FIFO_7,依次读8次Y_FIFO_0,Y_FIFO_1,…,Y_FIFO_7,依次读8次Y_FIFO_8,Y_FIFO_9,…,Y_FIFO_15,依次读8次Y_FIFO_8,Y_FIFO_9,…,Y_FIFO_15,依次读8次U_FIFO_0,U_FIFO_1,…,U_FIFO_15,依 次 读8次V_FIFO_0,V_FIFO_1,…,V_FIFO_15,然后再去读Y_FIFO,依次循环。

YUV420压缩格式中,按照图5的顺序,依次读8次Y_FIFO_0,Y_FIFO_1,…,Y_FIFO_7,依次读8次Y_FIFO_0,Y_FIFO_1,…,Y_FIFO_7,依次读8次Y_FIFO_8,Y_FIFO_9,…,Y_FIFO_15,依次读8次Y_FIFO_8,Y_FIFO_9,…,Y_FIFO_15,依次 读8次U_FIFO_0,U_FIFO_1,…,U_FIFO_7,依次读8次V_FIFO_0,V_FIFO_1,…,V_FIFO_7,然后再去读Y_FIFO,依次循环。

图5 主要国家和地区专利布局的技术领域分布

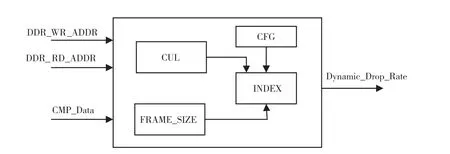

1.4 空间计算子模块

空间计算子模块的功能是计算系统在DDR中预留的用于存储压缩视频数据的内存空间剩余量,并计算得出动态丢帧率,将动态丢帧率传输给FRAME_DROP(丢帧子模块)。具体过程为:根据DDR中CMP_Data段的总线读写地址(DDR_WR_ADDR,DDR_RD_ADDR),计算得出剩余内存空间,同时结合当前帧压缩之后的帧大小(根据帧头帧尾信息FRAME_SIZE),预测出剩余空间还能存储多少压缩帧(压缩帧余量)。根据事先配置的丢帧率与压缩帧余量的对应索引表,得出动态丢帧率。空间计算子模块的架构如图7所示。

图7 空间计算子模块架构

举例描述对应索引表(INDEX):当剩余空间可以存储大于10压缩帧,动态丢帧率为0;当剩余空间可以存储大于6压缩帧小于10压缩帧,动态丢帧率为1/3;当剩余空间可以存储大于2压缩帧小于6压缩帧,动态丢帧率为4/5;当剩余空间存储小于1压缩帧,动态丢帧率为1。对于上述数值,用户可以根据应用需求灵活配置。

2 设计验证

2.1 系统仿真验证

搭建仿真验证平台,将多帧JPG格式的原始图像转换成RGB格式的16进制数据,保存文本(source_data.txt),在验证平台的TOP层读取原始数据文本(source_data.txt)后,输入到本设计。然后将本设计输出的压缩数据保存到文本(compress_data.txt),再转成二进制文件,生成JPG格式的压缩图片,通过比对压缩前后的图像信息,确定本文设计方案的正确性。

仿真测试用例1:输入10张分辨率为640×480的原始图像,对比压缩后的图像与原始图像,且遍历YUV444/YUV422/YUV420压缩格式。

仿真测试用例2:输入10张分辨率为1 024× 768的原始图像,对比压缩后的图像与原始图像,且遍历YUV444/YUV422/YUV420压缩格式。

仿真测试用例3:输入10张分辨率为1 920× 1 200的原始图像,对比压缩后的图像与原始图像,且遍历YUV444/YUV422/YUV420压缩格式。

仿真测试用例4:输入3张分辨率为640×480的原始图像,3张分辨率为1 024×768的原始图像,4张分辨率为1 920×1 200的原始图像,对比压缩后的图像与原始图像,且遍历YUV444/YUV422/YUV420压缩格式。

上述仿真用例全部测试通过。仿真波形如图8所示。

图8 本设计仿真波形截图

2.2 板级验证平台

基于服务器+Xilinx的Virtex UltraScale VU440 FPGA搭建硬件板级验证平台。现场可编程门阵列(Field Programmable Gate Array,FPGA)因其并行的处理方式,在图像处理方面具有低延时、高灵活的特点,能够满足图像数据采集与处理系统对实时性的要求[13]。将本设计的逻辑代码经过综合之后下载到VU440 FPGA开发平台,服务器主机端的系统画面经过PCIe接口输入到VU440 FPGA,经过本设计的功能处理后,实现对服务器主机端画面的视频压缩,并将压缩视频数据通过Web界面进行远程实时显示。显示结果如图9所示。

图9 服务器主机画面压缩后的远程显示

3 结 语

本文针对传统视频压缩方案需大量占用系统总线的弊端进行优化,设计BLOCK转换模块,避免了传统方案中将原始视频数据先写入DDR,再从DDR读出的弊端,并且设计了数据预处理模块,进一步减少了视频处理的数据量,同时设计了灵活的丢帧机制,以适应不同DDR容量,在不影响远端显示的需求下,进一步降低压缩视频的数据量,提升了系统整体性能。