基于FPGA的交通灯控制系统的设计与实现

赵万里 陈初侠 张涛 钟声 张永康 王世龙

摘要:该文基于FPGA芯片EP4CE6E22C8设计了一款交通灯控制系统。首先从设计要求出发,将交通灯控制系统分成多个底层电路模块并用Verilog HDL语言对其进行设计和仿真,然后调用已设计好的各底层电路采用原理图方式进行顶层电路设计,最后将设计好的顶层电路进行管脚锁定并下载到FPGA芯片中进行硬件验证。仿真和硬件验证结果表明,该交通灯控制系统在实现常规交通指挥功能的同时,還能够在一定程度上根据高峰时段和非高峰时段车流量的变化调节车辆通行时间,并且还具有在特殊情况时为应急车开道的功能,有效提高了十字路口的通行效率。

关键词:交通灯控制系统;FPGA;Verilog HDL;设计

中图分类号:TP29 文献标识码:A

文章编号:1009-3044(2022)01-0124-04

1 引言

交通信号灯在人们的日常生活中,起着至关重要的作用,但是随着国民经济的快速发展,城市化建设规模的不断扩大,人们对交通信号灯在协调交通、管理交通等方面的能力提出了更高的要求[1]。尤其是在当前社会城市化速度不断加快,城市交通基础建设已经远远赶不上实际需求的情况下,城市交通状况日益恶化,而随之带来的各方面问题也渐渐突出[2],如交通拥堵日益严重问题、交通事故频发问题、交通导致的空气污染和噪声污染问题等。因此,设计一款能有效提高十字路口通行效率的交通灯控制系统,对缓解日益严重的交通拥堵现象具有重大现实意义。

本文使用Verilog HDL语言以QuartusII软件为平台设计一款实用的交通灯控制系统[3],主控芯片采用Altera公司CycloneⅣ E系列FPGA芯片EP4CE6E22C8。该系统在实现常规交通指挥的同时,还能够在一定程度上根据高峰时段和非高峰时段车流量的变化调节车辆通行时间,另外还具有当发生特殊紧急情况时,东西、南北路口均设置为禁止通行,为应急车开道的功能[4]。

2 交通灯控制系统设计要求

本文设计的交通灯控制系统具有以下三方面的要求。

1)具有常规交通指挥的功能,具体表现如下。

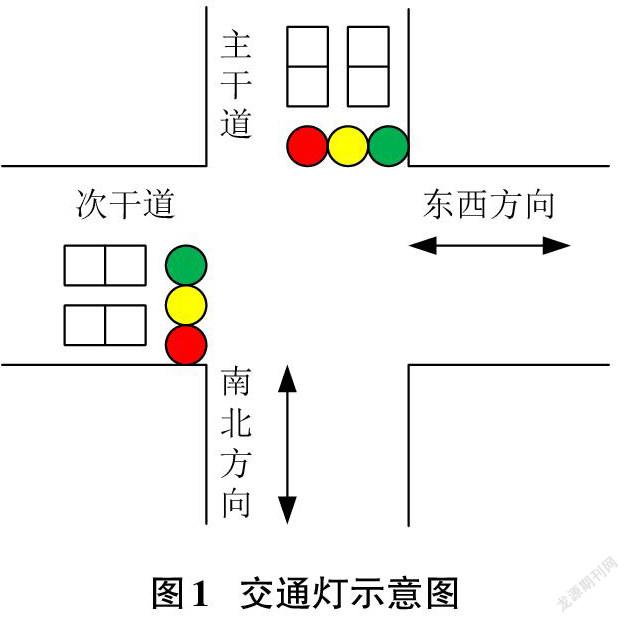

① 在交通灯十字路口的南北方向(主干道方向)和东西方向(次干道方向)都设置有红、黄、绿指示灯,如图1所示。

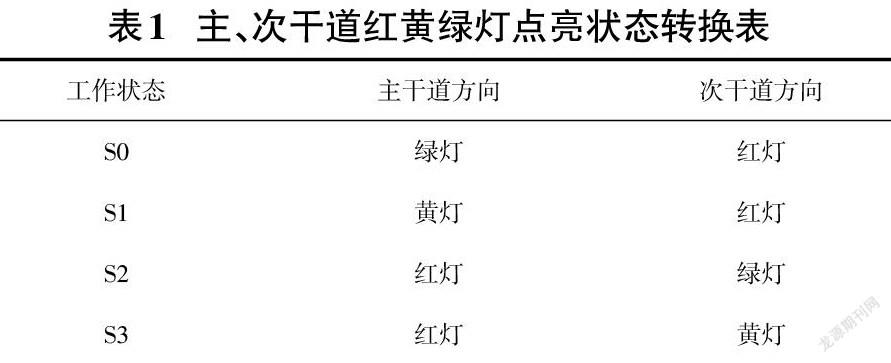

② 红、黄、绿灯的点亮按照绿灯→黄灯→红灯→绿灯依次循环,其中黄灯亮灯时间为5秒。这里要注意,主、次干道红黄绿灯的点亮应遵循表1规则。

③ 主、次干道都有数码管,显示红黄绿灯点亮的倒数计时时间。

2)具有应急车通行的功能。当发生紧急事件时,主、次干道都设为禁止通行,专为应急车开道。

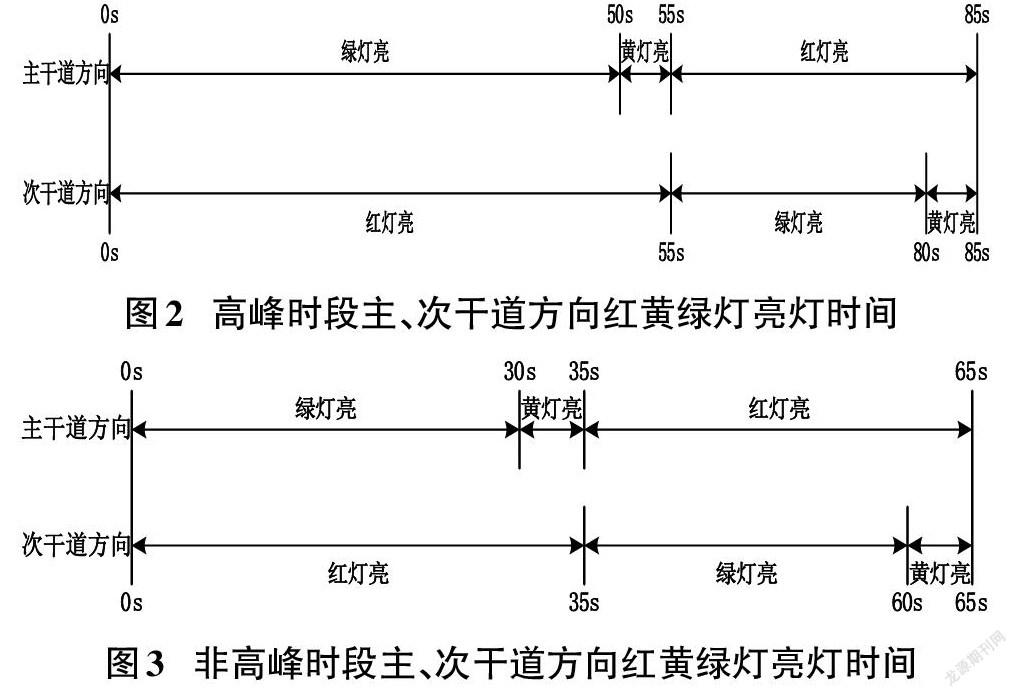

3)具有调节车辆通行时间的功能。这里指的是在高峰时段和非高峰时段,车辆通行时间不同。由于主干道车流量大,故通行时间相较于次干道要长。我们规定,在高峰时段主干道通行(绿灯亮)时间为50秒,次干道通行时间为25秒,如图2所示;在非高峰时段主干道通行时间为30秒,次干道通行时间为25秒,如图3所示。

4)具有状态保持功能。这里指的是当交通灯控制系统在正常运行时可以通过某个按键来控制交通灯是正常运行还是暂停运行,当暂停运行时,交通灯信号和倒数计时保持原状态不变。

3 交通灯控制系统总体设计方案

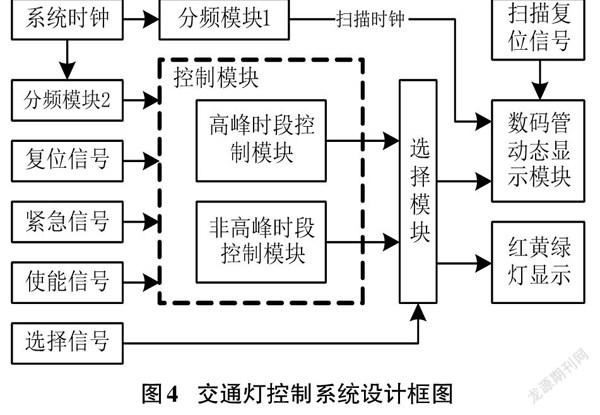

交通灯控制系统设计框图如图4所示。根据设计要求,本设计将交通灯控制系统分为五个部分,分别为外部输入、分频模块电路、控制模块电路、选择模块电路和显示输出电路。外部输入包含系统时钟、复位信号、紧急信号、使能信号、选择信号和动态扫描复位信号,其中系统时钟为50MHz的时钟源,紧急信号为特殊紧急情况时的控制信号,高电平有效。

分频模块电路包含分频模块1和分频模块2,分频模块1输出的为10KHz的扫描时钟信号,驱动数码管动态显示模块电路工作;分频模块2输出的为1Hz的激励信号,驱动控制模块电路工作。控制模块电路包含高峰时段控制模块电路和非高峰时段控制模块电路,其输出为主、次干道的红黄绿灯点亮及倒数计时情况。选择模块电路通过选择控制信号s来选择高峰或非高峰时段控制模块电路的输出数据。显示输出电路包含数码管动态显示模块电路和红黄绿灯亮灭的显示输出,其中数码管动态显示模块电路显示的为红黄绿灯点亮时的倒数计时情况。

4 交通灯控制系统设计

本次设计采用先底层电路设计后顶层电路设计的层次化设计方法。设计过程中,通过Quartus Ⅱ软件采用Verilog HDL语言和原理图相结合的设计方式来进行,其中底层电路用Verilog HDL语言来实现,顶层电路通过调用底层电路用原理图设计方式来实现[5]。

4.1 底层电路设计

底层电路有六个子电路模块,分别是5000分频模块、50000000分频模块、高峰时段控制模块、非高峰时段控制模块、选择模块和数码管动态显示模块。

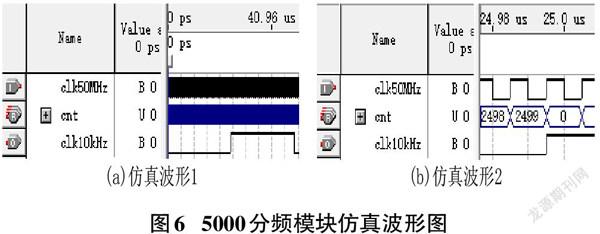

4.1.1 5000分频模块

该模块的功能是对50MHz系统时钟进行5000分频,产生一个10KHz的时钟信号,驱动数码管动态显示模块电路工作,其元件符号如图5所示。

图6为5000分频模块仿真波形图,可以看出,50MHz系统时钟每输入一个脉冲就对其进行一次计数,当计数到2499时,输出信号clk10KHz进行翻转,刚好计数5000次时输出为一个完整的周期信号,即实现了5000分频。

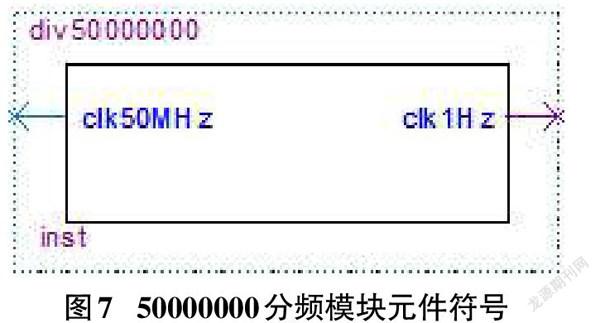

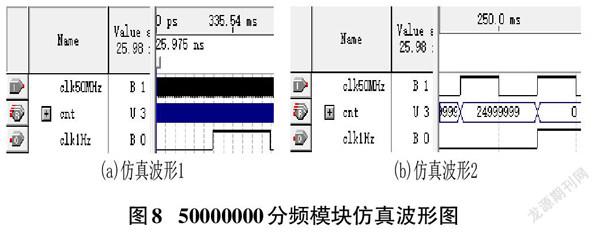

4.1.2 50000000分频模块

该模块的功能是对50MHz系统时钟进行50000000分频,产生一个1Hz的时钟信号,驱动控制模块电路工作,其元件符号如图7所示。

图8为50000000分频模块仿真波形图,可以看出,50MHz系统时钟每输入一个脉冲就对其进行一次计数,当计数到24999999时,输出信号clk1Hz进行翻转,刚好计数50000000次时输出为一个完整的周期信号,即实现了50000000分频。

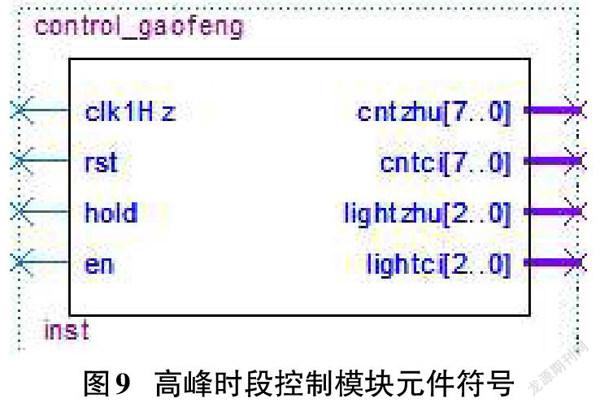

4.1.3 高峰时段控制模块

高峰时段控制模块通过输入信号来控制在高峰时期主、次干道的红黄绿灯亮灭情况,以及点亮时间的倒数计时情况,其元件符号如图9所示。输入信号有1Hz的周期信号clk1Hz、复位信号rst、紧急情况控制信号hold、状态转换使能信号en;输出信号有主干道倒数计时cntzhu、次干道倒数计时cizhu、主干道红黄绿灯亮灭显示lightzhu、次干道红黄绿灯亮灭显示lightci。

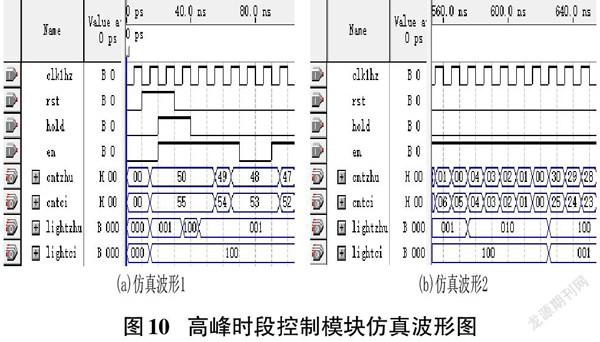

图10为高峰时段控制模块仿真波形图,主、次干道点亮红灯用“100”表示,点亮黄灯用“010”表示,点亮绿灯用“001”表示。从图10可看出,当rst、hold、en分别为1、X、X时(X代表未知,可以是0也可以是1,下同),主干道绿灯点亮且倒数计时为50秒,次干道红灯点亮且倒数计时为55秒,属于复位状态;当rst、hold、en分别为0、1、X时,主干道红灯点亮且倒数计时为50秒,次干道红灯点亮且倒数计时为55秒,属于紧急情况状态;当rst、hold、en分别为0、0、0时,主、次干道红黄绿灯亮灭情况保持原来状态不变,倒数计时数值保持不变,属于保持状态;当rst、hold、en分别为0、0、1时,交通灯属于正常工作状态,此时主、次干道红黄绿灯亮灭情况及倒数计时情况符合图2中所示,即主干道通行(绿灯亮)时间为50秒,次干道通行时间为25秒。

4.1.4 非高峰时段控制模块

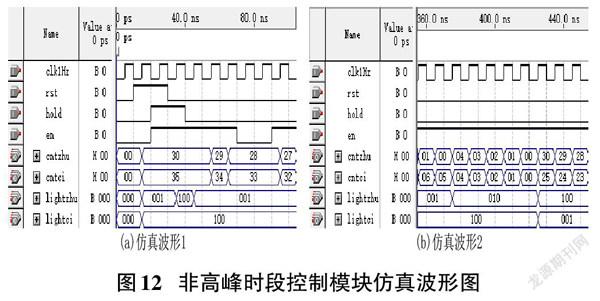

非高峰时段控制模块通过输入信号来控制在非高峰时期主、次干道的红黄绿灯亮灭情况,以及点亮时间的倒数计时情况,其输入输出信号与高峰时段控制模块完全一致,元件符号如图11所示。

图12为非高峰时段控制模块仿真波形图,可以看出,当rst、hold、en分别为1、X、X时,主干道绿灯点亮且倒数计时为30秒,次干道紅灯点亮且倒数计时为35秒,属于复位状态;当rst、hold、en分别为0、1、X时,主干道红灯点亮且倒数计时为30秒,次干道红灯点亮且倒数计时为35秒,属于紧急情况状态;当rst、hold、en分别为0、0、0时,主、次干道红黄绿灯亮灭情况保持原来状态不变,倒数计时数值保持不变,属于保持状态;当rst、hold、en分别为0、0、1时,交通灯属于正常工作状态,此时主、次干道红黄绿灯亮灭情况及倒数计时情况符合图3中所示,即主干道通行(绿灯亮)时间为30秒,次干道通行时间为25秒。

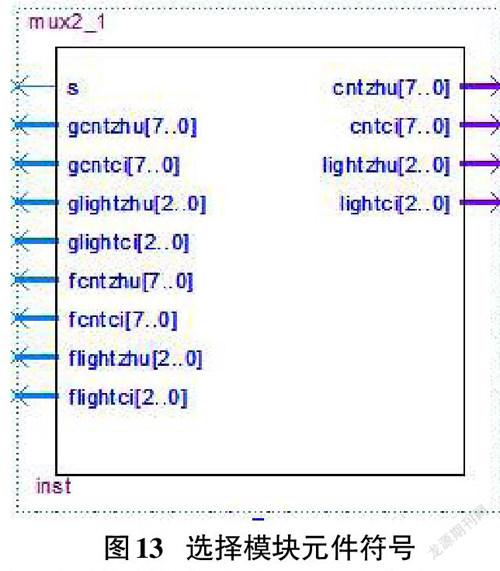

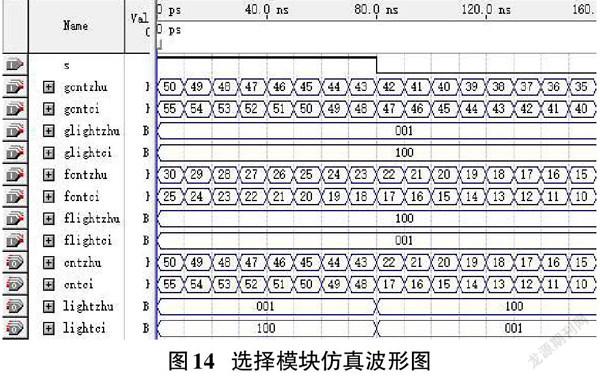

4.1.5 选择模块

选择模块是一个二选一数据选择器,选择控制信号为s,输入数据有高峰时段控制模块的输出数据和非高峰时段控制模块的输出数据。当处于高峰时段时选择高峰时段的数据,否则选择非高峰时段的数据,元件符号如图13所示。

图14为选择模块仿真波形图,此时高峰时段的数据为主干道通行并从50秒开始倒计时,次干道禁止通行并从55秒开始倒计时;非高峰时段的数据为主干道禁止通行并从30秒开始倒计时,次干道通行并从25秒开始倒计时。从波形可以看出,当s为1时选择的是高峰时段的数据,当s为0时选择的是非高峰时段的数据。

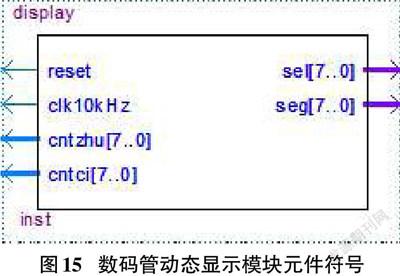

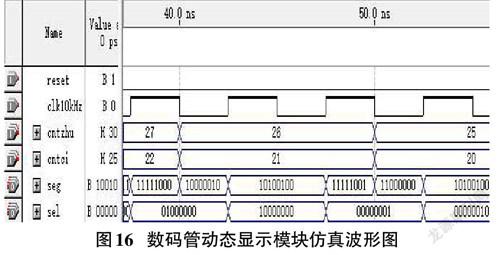

4.1.6数码管动态显示模块

数码管动态显示模块采用动态扫描的方式用八段数码管来显示红黄绿灯倒数计时的数值,其元件符号如图15所示。输入信号有动态扫描复位信号reset、扫描时钟clk10KHz、主次干道倒计时的数值;输出数据有位选信号sel和段选信号seg。位选信号sel为“10000000”“01000000”时,选择的是主干道数据cntzhu的十位和各位;sel为“00000010”“00000001”时,选择的是次干道数据cntci的十位和各位。段选信号seg为共阳极的八段数码管译码输出,当seg为“11111001”时数码管显示为“1”,当seg为“10100100”时数码管显示为“2”。

图16为数码管动态显示模块仿真波形图,从图中可以看出,当sel为“10000000”时应选择主干道的十位数据即“2”,而此时seg数值为“10100100”,在数码管上显示刚好就是“2”,说明仿真波形正确。

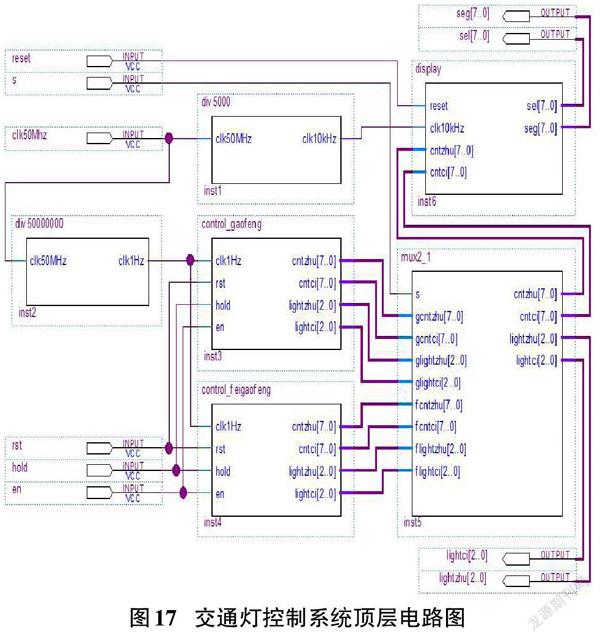

4.2 顶层电路设计

交通灯控制系统顶层电路设计采用原理图输入方式进行,通过调用已生成的各底层模块元件符号,并将它们做适当连接就可实现顶层电路的设计,电路如图17所示。

5交通灯控制系统的硬件实现

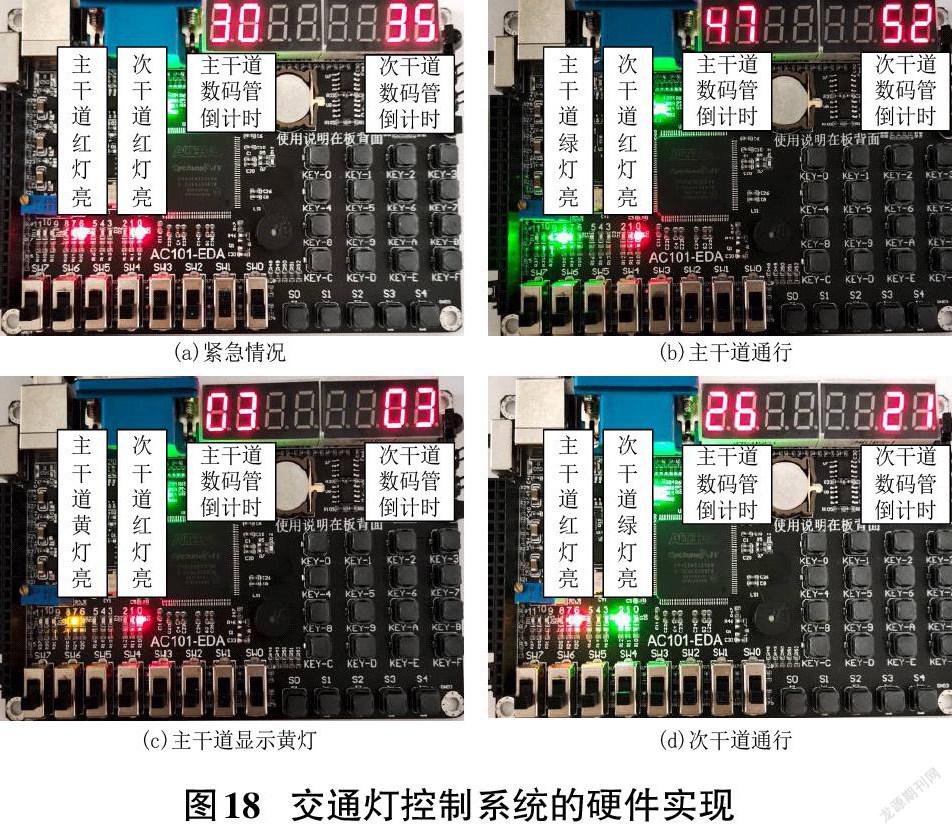

本设计选用小梅哥AC101-EDA开发板作为硬件验证平台,首先对交通灯控制系统顶层电路的输入输出引脚进行锁定,然后重新编译并下载到开发板FPGA芯片EP4CE6E22C8中,最后对交通灯控制系统进行硬件测试验证。

硬件验证结果如图18所示,(a)为非高峰时段交通灯控制系统处于紧急状态的情况,此时主干道和次干道都禁止通行,专为应急车开道;(b)为高峰时段交通灯控制系统处于正常运行的情况,此时主干道通行,次干道禁止通行,且主干道倒计时显示为47秒,次干道倒计时显示为52秒;(c)为交通灯控制系统处于正常运行的情况,此时主干道由绿灯变成了黄灯,次干道禁止通行,且主干道和次干道倒计时显示均为3秒;(d)为交通灯控制系统处于正常运行的情况,此时主干道禁止通行,次干道通行,且主干道倒计时显示为26秒,次干道倒计时显示为21秒。以上四种情况基本上包含了本交通灯控制系统的运行情况,从硬件验证结果可以看出,所设计的电路完全实现了本交通灯控制系统的设计要求。

6 结束语

本文基于FPGA芯片采用层次化的设计方法设计了一款交通灯控制系统。设计过程中,首先将交通灯控制系统分成多个底层电路模块;然后通过Quartus Ⅱ软件采用Verilog HDL语言设计各底层电路模块并对其进行仿真分析;接着把设计好的各底层电路模块生成元件符号并调用它们用原理图设计方式进行交通灯控制系统顶层电路设计;最后把设计好的顶层电路进行管脚锁定并下载到FPGA芯片EP4CE6E22C8中对其进行硬件测试验证。仿真和硬件验证结果表明,本交通灯控制系统在实现常规交通指挥功能的同时,还能够在一定程度上根据高峰时段和非高峰时段车流量的变化调节车辆通行时间,并且还具有在特殊情况时为应急车开道的功能,具有一定的实用价值。

参考文献:

[1] 沈晟.基于FPGA的交通灯控制系统的设计与实现[D].昆明:昆明理工大学,2010.

[2] 孙辉.基于FPGA的实时交通灯控制系统的设计与实现[D].武汉:华中科技大学,2011.

[3] 刘艳昌,王廷雨.基于FPGA的交通灯控制系统设计[J].河南科技学院学报(自然科学版),2013,41(4):67-73.

[4] 林倩,孙晴,李柳群,等.基于FPGA的多相位交通控制系统的设计[J].电声技术,2015,39(11):37-41.

[5] 张炯,陈初侠,操晓思,等.基于FPGA的出租车计费系统设计[J].电脑知识与技术,2021,17(13):93-95.

【通联编辑:朱宝贵】

收稿日期:2021-06-25

基金项目:巢湖学院2021年度国家级大学生创新创业训练计划项目(项目编号:202110380002);巢湖学院2019年度校级质量工程项目(项目编号:ch19yykc01);巢湖学院2020年度校级一流课程建设项目(项目编号:chylkc015);巢湖学院2020年度校级质量工程项目(项目编号:ch20jxyj14)

作者简介:赵万里(2000—),男,安徽亳州人,本科在读,主要研究方向为电子电路设计;陈初侠(1984—),男,江西乐安人,通信作者,实验师,硕士,主要研究方向为EDA技术、数字图像处理等。

3073500338209