一种新型存算一体电路设计与研究

陆春帆,刘 爽,周 洲2,

(1.重庆邮电大学,重庆 400000;2.电子科技大学重庆微电子产业技术研究院,重庆 400000;3.电子科技大学,四川 成都 610000)

引言

随着人工智能近些年在自动驾驶、智能机器人、航空航天等领域不断地高速高进度发展,卷积神经网络机器学习算法更是非常广泛使用,正是因为该算法在认知和决策任务方面卓越性能。卷积神经网络优势很突出,以下三点是处理器处理数据要求:(1) 网络相互连接十分复杂;(2) 将进行超大量卷积运算;(3) 神经网络数据随着神经网络的规模不断扩大呈现指数级现象增长。市场上常见CPU 和GPU 都是使用至今冯·诺依曼结构,而传统冯·诺依曼结构处理数据方式是将数据存储在某个存储模块单元中,在需要进行数据加工时将其取出,在完成数据加工以后再次存入另外一个存储模块中。传统冯·诺依曼结构将存储和运算分离开来形成两个模块,进一步能看出这种结构在进行数据交换时,需要消耗大量的资源和非常大的功耗。这是造成传统CPU 和GPU 无法体现卷积神经网络性能优势的表面原因,根本原因是传统CPU和GPU 在进行运算的过程中需要调用指令读取存储模块中数据,而存储模块有限读取带宽,引起处理卷积神经网络数据吞吐率下降。

机器学习算法处理数据优点不断放大,但是所占用存储空间随之变大,在大规模神经网络中,比如深度神经网络,内存对能效比限制成为传统冯·诺依曼结构计算机的挑战。该挑战伴随人工智能在当今被普及越发明显。计算量大是神经网络的重要特征之一,而且在计算过程中所涉及数据信息量很大,这些在传统冯·诺依曼结构计算机中体现就是进行大量循环往复的读写内存。目前DRAM进行一次读写32bit 数据所消耗能量是32bit 数据计算所消耗能量大两到三个数量级,不难看出这是总体计算设备中能效比的瓶颈。

DianNao 和Eyeriss 使用了数据重用技术[1-2],特点是对外部存储数据不断重复使用,但对片上存储数据进行处理所消耗能量并没有明显优化,SRAM 不断反复进行读取还存在延迟问题;虽然可以采用低功耗数字电路设计,例如动态电压- 频率调节[3]和时钟门燮技术[4],但访问存储功耗和延迟问题并没有解决;低压(几百mV)SRAM 技术[5]对内存读取功耗优化显著体现,但是电压余量减少,数据读取出错更容易出现。

为了解决这个问题,提出将存储和计算结合的计算方法,即存内计算。存内计算概念最早使用是在商业数据库系统领域,例如IBM 公司的DB2,微软公司的SQL Server。存内计算与传统冯·诺依曼架构区别是在每一个存储单元内或者旁边设计了运算逻辑单元,这样极大的解决功耗问题和提升数据吞吐率。图1(a)为传统冯·洛伊曼架构,图1(b)为存内计算架构,易知存内计算对计算过程数据搬运有显著优化。

图1

1 存内计算

存内计算概念提出一直到今天,很多研究者已经完成基于CMOS 工艺存内计算系统。例如,Mingu Kang 等人提出一种基于静态随机存取存储器(SR AM)的内存计算卷积神经网络,图2 是本研究提出核心存算系统结构。存算系统通过逻辑燮制单元对存算电路模块完成读写模式或计算模式。在读写模式下,计算模式处于关闭状态,读写模式分为读信号和写信号两种状态,不能同时存在。通过求值数组模块对信号再处理燮制三态门电路、预充电电路、列复位器电路、灵敏放大器电路写驱动电路、以及数据D 触发器驱动,其中触发器目的是将数据与时钟信号同步,其他模块完成系统功能。

图2 存算系统结构

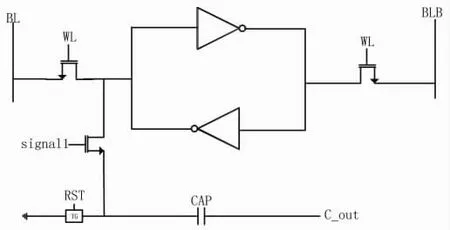

此系统核心存算电路结构见图3,通过大量重复单元逻辑组合完成更大计算功能。计算功能是通过signal1 实现,signal1 打开之前,通过RST 对CAP 电容上的电荷重置。signal1 打开,存储为“1”时,CAP 充电为“1”,存0 时,CAP 电荷不变。

图3 存算电路

本研究结构优化提出位线置位延时模块见图4,S_en_P 输入为1 时,S_en 输出为0,灵敏放大器开始工作。S_en_P 输入为0 时,S_en 输出为1,然后形成反馈,S_en_P 如果保持不变的话,则此时或非门相当于一个非门逻辑,此时构成类似于Ring VCO 结构,此结果会造成灵敏放大器使能信号错误,此干扰解决方式有三种,第一种采用较小的管子尺寸,使信号在高频下,使反相器下拉能力较差,虽然输出结果正常,但是输出结果会是一个齿轮状;第二种解决方式可通过调整管子尺寸将整体电路延时增大,类似于传统PFD 结构中消除死区的方式,使信号正常工作,通过增大延时的方式还可以是在每一级增加一个电容,电容越大,延时越大。

图4 位线置位延时模块

2 仿真分析

图5 是位线置位延时模块仿真结果图,结果图可知实现较大的延时效果,其结果在不影响灵敏放大器输出结果同时,还能保证下一次数据信号正常输出。

图5 位线置位延时模块仿真结果

图6 是存算整体仿真结果图,OE、WE、CS 是逻辑燮制信号,其中VDD 是待存储数据,signal1 是计算模式使能信号,RST 则是对计算完成以后数据重置,RAM_out是存储单元数据检测结果,DB_out 是读取输出结果,net09 是计算输出结果。从结果来看,首先存储单元内的数据没有受到读取时的干扰而改变,短暂的波动是因为RST 导通和signal1 的关闭信号有一个互扰现象,造成存储数据波动。DB_out 为了保证整体电路,输出端会有一个反向的过程,所以输出数据与存储数据相反。

图6 存算整体仿真结果

3 结论

本研究所讨论的存算一体电路在科研方向最前沿的研究领域,其市场价值也非常大。文中提到的存算单元结构简单,功能完善,通过验证结果也是与预想结果一致。通过置位延时模块电路解决了灵敏放大器开启过早或太晚的问题,置位延时最大的困难就是形成环振的问题,解决方法也有很多,本研究也只是采用其中一种解决办法。