基于LabVIEW 和FPGA 的半实物仿真平台的设计与实现*

疏成 成 ,苏建 徽 ,施 永 ,解 宝 ,赖纪东

(1.光伏系统教育部工程中心,安徽 合肥 230009;2.合肥工业大学 电气与自动化工程学院,安徽 合肥 230009)

0 引言

半实物实时仿真的技术有两种方式:一种是快速控制原型(Rapid Control Prototyping,RCP)采用“虚拟控制器+实际对象”方式;另一种是硬件在回路(Hardware in Loop,HIL)采用“实际控制器+虚拟对象”方式,主要应用于电力电子系统控制器软件的开发。半实物实时仿真的应用领域非常广泛,涉及轨道交通、风电、光伏发电、新能源汽车、电力系统、工业传动等[1-5]。半实物仿真的硬件在回路(HIL)仿真的方式是将数学化的实体模型和实际控制器联系在一起运行的仿真系统[6-7]。相对于纯计算机软件仿真,半实物仿真具有有效性、可重复性、经济性、安全性等诸多优点,是一种更接近实际情形的仿真技术[8-11]。

平台采用“FPGA+ARM”作为下位机,用以太网方式和LabVIEW 上位机通信,实现在同一网络下下载模型,很大程度降低了用户使用的难度,让学生用模型做实验更加便捷。

1 半实物实时仿真平台的结构

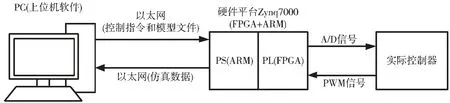

半实物实时仿真平台是基于HIL 仿真方式设计而成的,主要由三部分组成:硬件系统、实物软件模型和上位机系统。硬件系统主要用于采集和处理各种信号,通过FPGA 和ARM 构建一个基本的通信平台,保证通信的可靠性和稳定性,并拥有丰富的I/O 接口提升其扩展性。硬件系统通过以太网的方式与上位机系统建立通信,进行数据传输。在硬件系统的基础上,上位机软件主要完成硬件系统的相关配置、模型的参数设置、提供测试过程中的控制指令、创建可视化的人机交互界面等工作。上位机软件的存在大大提高了整个半实物实时仿真平台的易用性。实物软件模型是根据需要测试的实物设计出不同的实物模型,来配合硬件系统完成半实物实时仿真。该半实物实时仿真平台的原理示意图如图1 所示。本文的平台可以在上位机软件中选择实物模型,将其下载到FPGA 中,通过上位机进行参数的设置和仿真的启停等控制指令。仿真开始后,FPGA 可以得到实物模型实时运行的数据。数据会在ARM 程序中进行打包处理,然后通过以太网,将打包后的数据发给上位机软件。上位机对仿真的数据进行解析、转换格式等处理后,就会在虚拟示波器上显示相应曲线波形。

图1 HIL 系统仿真平台原理图

2 硬件系统设计与实物模型搭建

本文的半实物仿真平台使用的是Xilinx 公司Zynq7000 系列的XC7Z020-2CLG400I 的(FPGA+ARM)芯片。Zynq7000 芯片可分为Processor System(PS)处理系统部分和Programmable Logic(PL)可编辑逻辑部分。PL 部分加载了FPGA 的程序,可以实时运行实物模型,得到相应的测试点数据。测试点的数据会保存在特定的地址区。PS 部分加载了ARM 的程序,是上位机程序和FPGA之间沟通的桥梁,主要有两个功能:(1)解析上位机软件下发的控制指令和参数,并通过一定的逻辑关系进行对FPGA 控制;(2)在数据内存满时触发中断程序,对数据进行打包,发送给上位机。

搭建实物模型的步骤如下所示:

(1)根据该实物模型相关的数学公式和要求,选择自己的建模方法。

(2)根据数学公式,使用System Generator 软件进行实物模型的搭建,生成Verilog 工程文件。

(3)根据实物模型生成的Verilog 工程文件,通过软件创建新项目,在新项目里为模型建立IP 核和相应接口配置,和通信模块一起生成Bit 文件。将Bit 文件、相关参数配置文件和实物模型拓扑图按一定要求存放在上位机软件指定目录下。

3 上位机系统设计

LabVIEW 是图形化的G 语言的编写程序,利用框图式的程序来代替冗长的语言代码,能够快速地创建算法来解决各种工程问题,而且人机交互界面操作简易,可以帮助用户快速上手操作。本文的半实物实时仿真平台的上位机软件是基于LabVIEW 进行编写的[12-14]。上位机软件所采用的框架是“生产者+消费者”。生产者-事件结构根据用户的按键等动作进行触发中断,队列负责将相应中断和中断包含的数据传至条件结构,消费者-条件结构通过中断类型进行判断,进入不同的算法模块和功能模块。

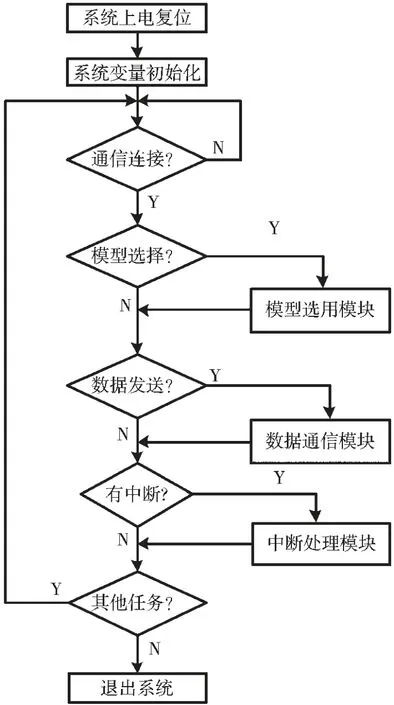

其软件的功能设计主要包括三大模块,分别为模型选用和参数设置模块、虚拟示波器模块和以太网通信及数据处理模块,可实现仿真启停控制、模型拓扑图显示、数据存储及追溯等常用功能。上位机软件主程序流程图如图2 所示,中断处理模块包含了虚拟示波器模块。

图2 主程序流程图

3.1 模型选用和参数设置模块设计

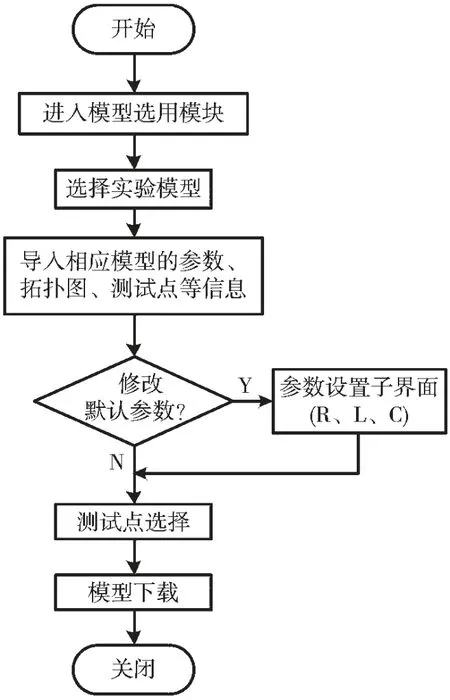

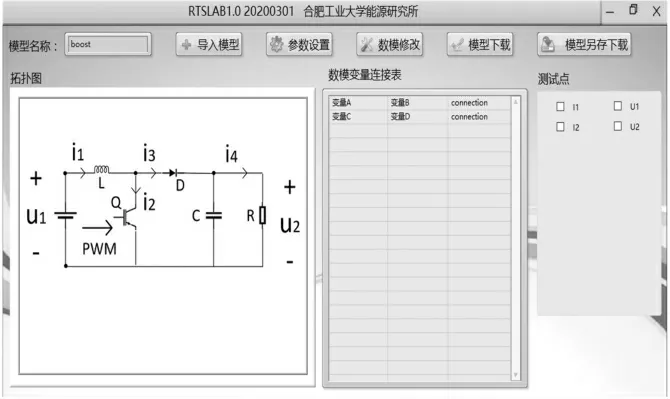

模型选用和参数设置模块负责实验所用的模型及其参数的管理,采用配置文件的方式保存各种实验模型的文件和参数信息。当导入一个模型时,通过NI 的“递归文件列表”索引出该模型文件夹下所有文件名和路径,再通过“文本读取文件”和“读取JPEG 文件”的控件将模型参数和拓扑图读取并显示在前面板。而且用户可以在该模块上对实验模型的参数和测试点的信息进行设置,然后将所有参数信息按变量名区分后打包传输给ARM,ARM 通过协议解析变量,将其参数赋值到FPGA 指定变量地址区中。FPGA 中的模型参数是通过读取指定变量区的值进行确定的。模型选择模块流程图如图3 所示。上位机的Boost 模型选用模块界面如图4 所示。

图3 模型选择模块流程图

图4 Boost 模型选用模块界面

3.2 虚拟示波器模块设计

虚拟仪器技术是通过利用高性能的硬件和高效灵活的软件进行各种测试、自动化的应用。虚拟示波器根据这原理设计制作而成,利用软件创建完全自定义的用户界面,模块化硬件能方便地提供全方位的系统集成,标准化的软硬件平台可以满足同步和定时应用的需求。本文的虚拟示波器是基于传统示波器的功能结合半实物仿真平台所需功能上进行设计的,融合了虚拟仪器的特点,在计算机上实现波形的显示并进行波形处理。其主要有以下功能:

(1)多通道实现

根据半实物仿真的特点,本文的软件设计了多通道的示波器,可以最多同时解析20 组数据包及其他变量状态。选用NI 示波器组件中的“XY 图”,根据该示波器的特性,开辟20 个浮点型的二维数组,每个二维数组对应保存着每条曲线数据和步长数据,前10 组保存电流曲线,后10 组保存电压曲线。通过图4 的测试点的选择,得到所需要显示曲线的变量名,再与ARM 传输过来的数据包对比,得到相应测试点的曲线数据。将每条曲线数据与步长数据结合成二维数组元素,然后将所有元素按顺序组成的新二维数组,并赋值给示波器组件的局部变量,进行曲线显示。

(2)步长设置

步长是虚拟示波器水平方向(X 轴)上所代表的时间间隔,也是实物模型在FPGA 的运行步长。示波器的默认步长为该模型配置文件中的最小步长,最小步长由事先的实验得出。也可以通过界面上的“步长设置”初步设置其步长,当将步长信息传输到ARM 中时,由ARM 对FPGA 中的模型进行步长设置,若设置成功,ARM 会给上位机发送相应的置1 信号,若没有设置成功,则会发0信号。上位机通过接收信号判断步长是否设置成功,若成功则该设置的步长为最终步长,而且X 轴的相应步长变换为该值,若失败则保持X 轴的事先步长不变且弹出提示框告知需要重新设置步长。

(3)波形显示、存储、清空

由于是虚拟示波器界面,波形的显示与传统示波器有差异,在波形显示的过程中,通过“XY 图”示波器的“图例”和“图形控制选板”控件,对显示的波形进行放大、缩小、局部放缩。在主程序中编写示波器的开始赋值、停止赋值、清空数据和保存数据的中断程序,实现前面板示波器的开始和停止操作。实验完成后对实验数据进行存储和清空操作。

3.3 以太网通信及数据处理模块设计

3.3.1 模型的下载方式

模型下载比较简单的方式是通过JTAG 口进行烧写,将模型固化在FPGA 中,即将固定的几种模型文件保存在FPGA的存储单元。这种方式存在着一些缺陷,由于存储空间的限制,模型数量有限且模型变化和扩展困难。本文的方式是模型以规定的文件数据格式存储在上位机硬盘或其他移动存储单元中,通过以太网更新Flash的方式,将模型的文件从上位机下载到FPGA 中。

上位机会通过LabVIEW 中的“读取文本文件”的函数来读取所选模型的Bit 文件内容,并通过以太网通信将模型Bit 文件内容和update 指令传输给ARM。ARM 通过上位机下发的update 的指令,触发ARM 的Flash 写的函数,将Bit 文件内容烧到Flash 中。

ARM 程序中需要一个单独程序负责Flash 写的使能及关闭、Flash擦除、Flash 读、Flash 写、读Flash ID等操作。当更新Flash 结束后再反馈上位机一个下载模型是否成功的信号。

3.3.2 以太网通信及数据处理模块设计

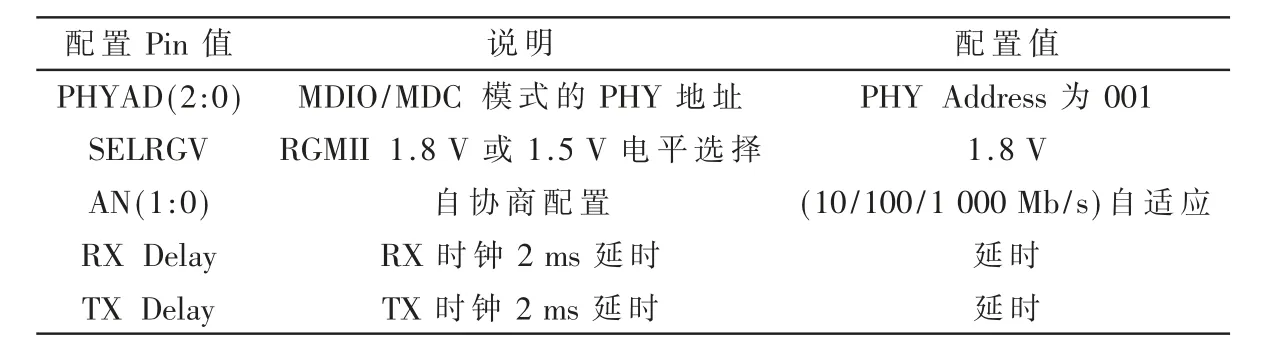

核心控制板上利用Realtek RTL8211E-VL 的以太网PHY 芯片进行网络通信。PS 端BANK501 的GPIO 接口上连接着PHY 芯片。RTL8211E-VL 芯片支持10/100/1 000 Mb/s 传输速度的以太网,它通过RGMII 接口与PS部分的 MAC 层进行通信。RTL8211E-VL 芯片支持传输速度自适应、Master/Slave 自适应、MDI/MDX 自适应,并且允许MDIO 总线对PHY 的寄存器进行管理。RTL8211E-VL 上电后会进行部分特定IO 的电平的状态检测,从而确定其工作模式。表1 为PHY 芯片上电后的默认设定信息。

表1 PHY 芯片默认配置值

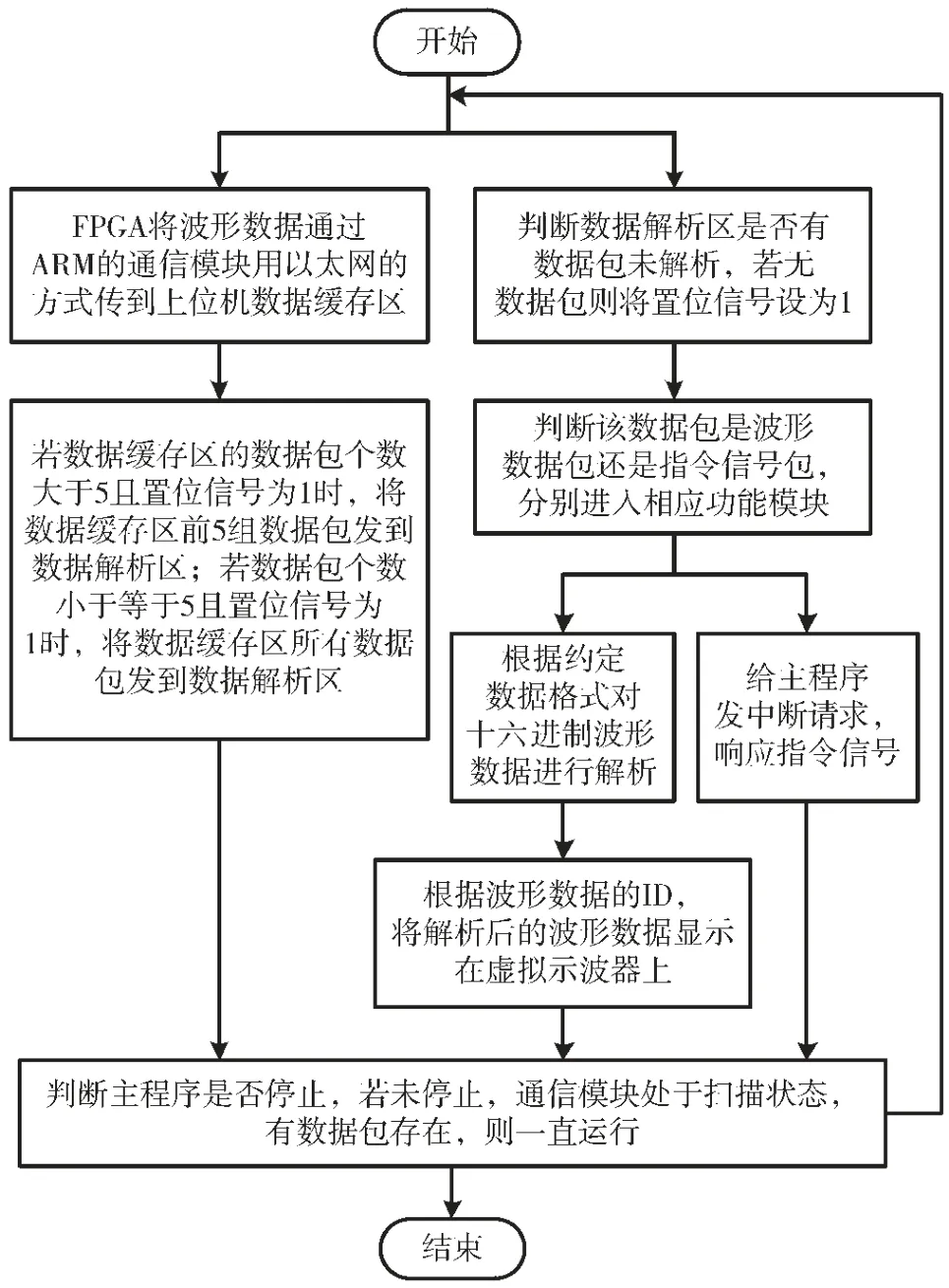

上位机软件与ARM 通信的过程中,上位机作服务器,ARM 作客户端,上位机设置端口号进行监听,ARM 通过IP 地址和端口号连接上服务器。通信的数据分为控制指令、参数数据、模型文件内容和波形数据,上位机与ARM通信的数据格式都是字符串,为了保证消息传输过程不会失真,两边的程序都针对传输数据进行头尾固定字符串校验和整个数据长度进行校验,如果校验不通过,则放弃这个包的数据。以太网通信模块数据处理程序流程图如图5 所示。

图5 以太网通信模块数据处理程序流程图

为了避免通信过程中存在数据解析速率问题导致的丢包问题,上位机采用并行数据处理方法。设立了数据缓存区和数据解析区,数据解析区无数据包解析时给置位信号,数据缓存区不断地接收下位机传送的数据包,当出现置位信号时,将前5 组数据包发给数据解析区。FPGA 读取的1 个波形数据由4 个16 进制的数据组成,出于提高下位机工作效率的考虑,ARM 程序并未对数据进行解析处理,直接将数据打包传给上位机。因此,上位机软件对波形数据进行单独的算法解析。

4 Buck 电路模型实验

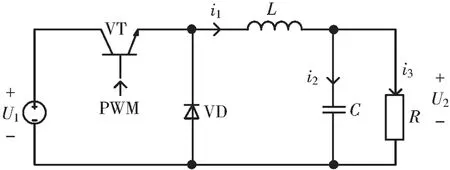

Buck 电路是一种常用的DC/DC 变换的基本电路。下面是以Buck 电路模型为例进行的实验验证,Buck 电路拓扑图如图6 所示。PWM 驱动信号由外置信号发生器提供[15]。

图6 Buck 电路拓扑图

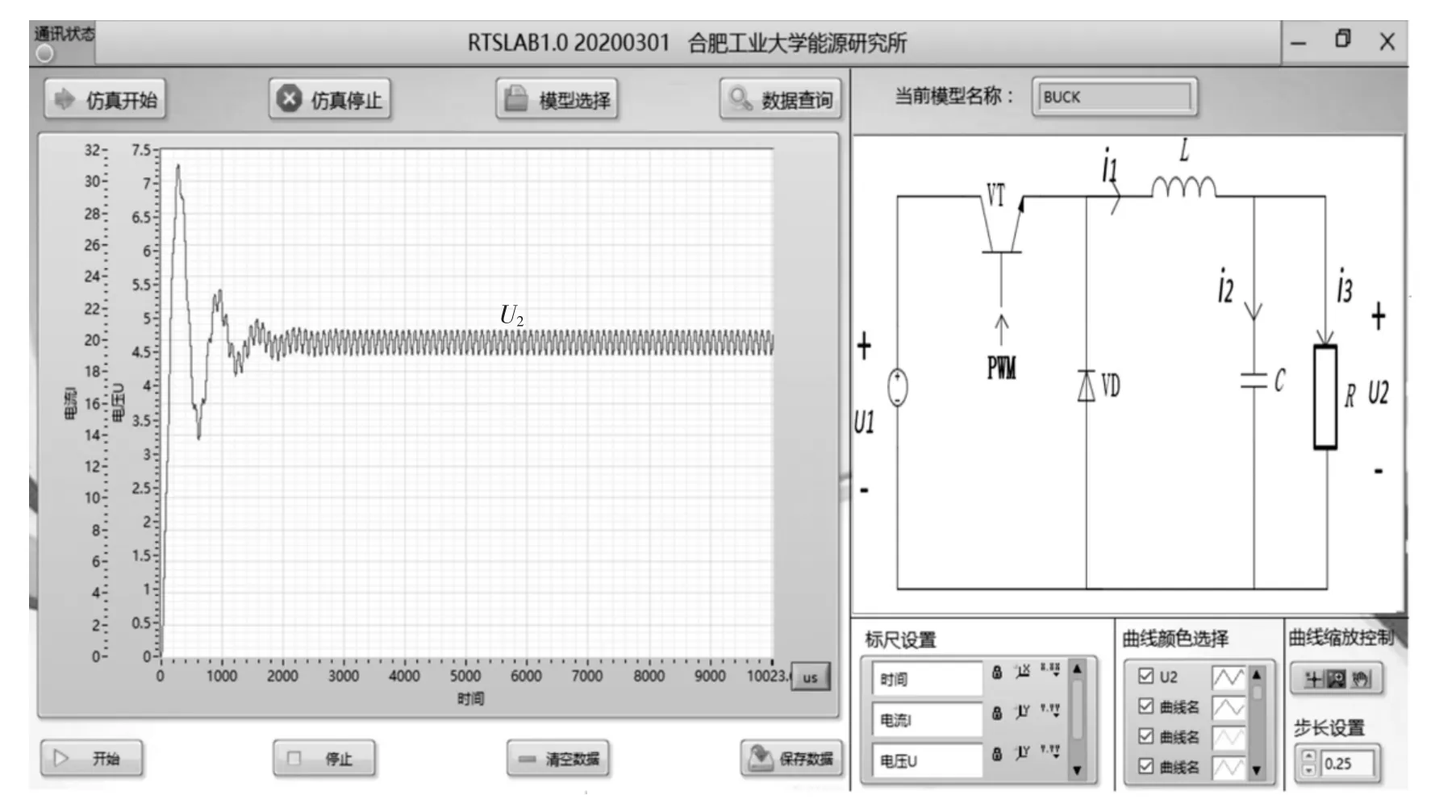

将PWM 信号频率设为100 kHz,占空比为0.4。将下位机与上位机连接在同一网络下,运行上位机时,点击“模型选择”按钮,进入图4 界面,点击“导入模型”并选用Buck 模型。在上位机将参数分别设置为:U1=12 V,R=5 Ω,L=200 μH,C=50 μF,步长设置为0.25 μs。然后选择U2为测试点,点击“下载模型”,在图7 所示的前面板中先点击“仿真开始”按钮然后点击左下角的“开始”按钮,仿真开始运行,并有U2的曲线输出显示。

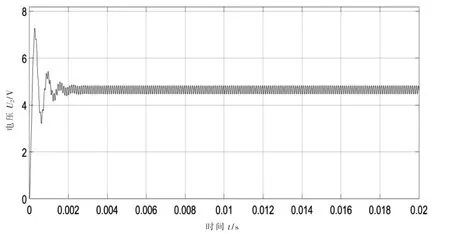

为验证实时仿真波形的正确性,在MATLAB环境下进行了同样参数的仿真,并与半实物实时仿真平台上的同一测试点波形进行了对比,图8 为MATLAB 离线仿真波形。图7 为上位机实时仿真波形,表2 为实验波形分析表,对比实验表明,该实时仿真结果是正确的,说明实验仿真平台达到设计要求。

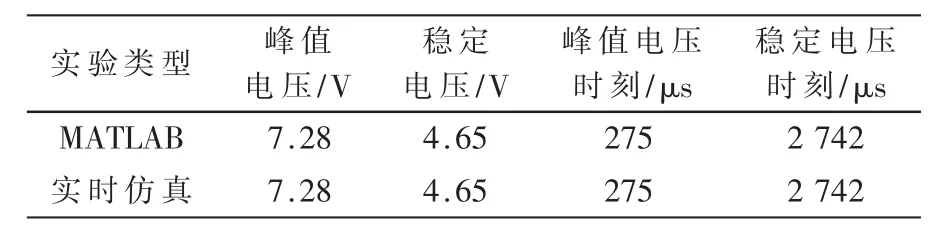

表2 实验波形分析表

图7 上位机电压U2 实时仿真波形

图8 MATLAB 电压U2 仿真波形

5 结论

基于LabVIEW 上位机软件和FPGA 设计的电力电子半实物实时仿真教学实验平台,其操作灵活性和性能指标满足教学与科研需求。利用LabVIEW 实现模型下载、参数设置以及仿真启停等控制指令的下发,并接收ARM 程序通过以太网上传的数据,在虚拟示波器上显示相应曲线波形,具有模型扩展方便、功能扩展容易等特点。利用FPGA 的高速运算能力对模型进行迭代计算,并将得到的数据进行打包处理,通过以太网上传给上位机软件,实现了实时仿真的快速性和各点波形上传。上位机系统的设计主要包括了三大功能模块:模型选用和参数设置模块、虚拟示波器模块和以太网通信及数据处理模块。相比于将模型固化于FPGA 中的设计方法,提出的通过以太网更新Flash 的方式将模型文件从上位机下载到FPGA 中,解决了模型数量有限且模型变化和扩展困难问题。系统通过典型Buck 电路模型HIL 实时仿真实验,步长为250 ns,验证了实验平台的准确性。