JPEG2000位平面编码器并行优化

东南大学微电子学院 庞子安

针对JPEG2000位平面编码器传统的串行扫描方式计算时间长、存储消耗大的问题,笔者提出了位平面编码器的并行优化,分析了位平面编码各编码通道前后显著性状态的改变,设计了流水线结构的通道判决电路,减少了显著性状态中间存储的需求,提升了位平面编码的速度。实验结果表明,并行优化的位平面编码器在性能和资源使用上达到了较好的水平。

JPEG2000压缩标准是当前最新的静态图像压缩标准,该算法首先通过离散小波变换对原始图像进行多分辨率分析,之后对小波系数进行量化后以码块(通常大小为32×32或64×64)为单位输入核心编码模块EBCOT(优化截取内嵌码块编码),EBCOT中传统串行位平面编码器的编码速率低下,文献基于行列跳过对串行编码进行了优化,但其受到原始数据影响,性能不稳定。本文将利用FPGA并行优势对位平面编码器进行改进,以减少资源的消耗,提高运算的速率。

1 串行位平面编码器编码流程

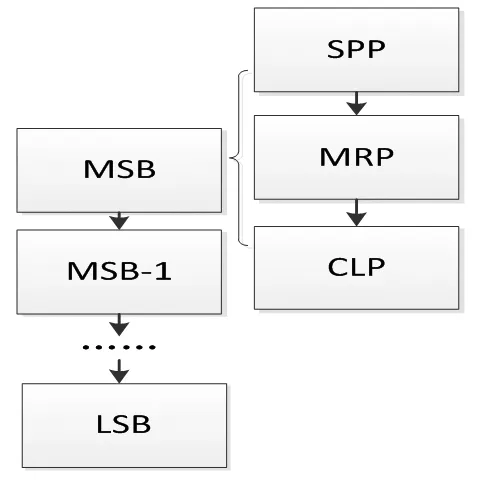

位平面编码器的输入是以码块(大小通常为32×32或64×64)为单位的小波量化系数,输出是上下文标签CX和码值D。传统串行位平面编码流程如图1所示,从最高的非全零位平面(MSB)开始,编码至最低位平面(LSB),在同一个位平面中,按照显著性传播通道(SPP)、幅值细化编码通道(MRP)、清除通道(CLP)的顺序进行编码,特别的,对于最高非全零位平面,所有的比特均属于清除通道,其余位平面中的比特只能属于其中的一个通道,通道的判决与样本显著性状态息息相关,若当前编码比特所在样本之前的位平面存在比特‘1’,则编码比特的显著性为‘1’。

图1 串行位平面编码流程

比特所属通道的判决规则如下:

(1)若当前比特所在样本显著性为‘0’,且周围8个样本至少有一个样本的显著性为‘1’,则该比特属于显著性传播通道。

(2)若当前比特所在样本的显著性为‘1’,则该比特属于幅值细化编码通道。

(3)不属于以上两种情况的比特,属于清除通道。

设码块大小为N×N,通道内的编码以一列四个比特为条带,条带内从上到下进行扫描,条带之间以从左到右、从上到下的顺序进行扫描,若扫描过程中遇到不属于当前编码通道的比特,则丢弃编码结果。

2 位平面编码器的并行优化

2.1 位平面编码器串行编码流程分析

分析串行位平面编码的过程,会在很多时钟周期中产生无效的编码结果;同时,计算出的显著性状态,需要保存下来在下一个编码通道扫描时使用,消耗了较多的存储资源。由此,需要充分利用已经计算出来的显著性状态,以求尽早完成当前编码列各编码通道编码,从而减少存储资源的需求和计算时间,解决这一问题的关键在于分析给定位平面下各个编码通道扫描时,当前编码比特的邻域显著性状态以及扫描过程后当前编码比特显著性状态的改变。

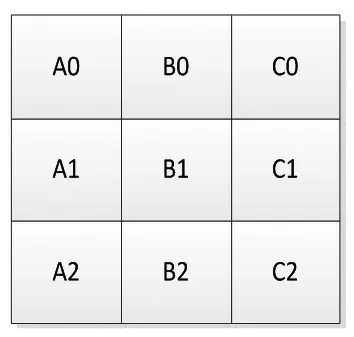

根据前面所述的串行编码流程,除去最高非全零位平面的比特全部属于清除通道编码外,其余位平面的编码顺序为显著性传播通道、幅值细化编码通道、清除通道。邻域各样本定义如图2所示,其中B1为当前编码比特。

图2 邻域显著性状态

B1进行显著性传播通道扫描时,由于输入的顺序,A0、A1、A2、B0已经通过显著性状态扫描,定义四者当前时刻的显著性状态分别为A0_spp、A1_spp、A2_spp、B0_spp。B2、C0、C1、C2未通过显著性状态扫描,定义四者当前时刻的显著性状态为B2_org、C0_org、C1_org、C2_org,定义B1初始显著性状态为B1_org。

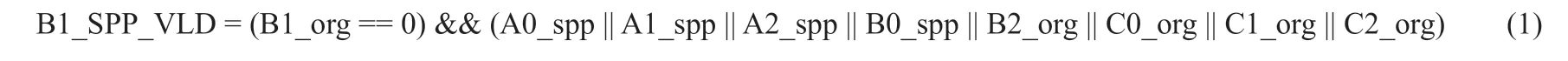

则B1属于显著性传播通道的条件B1_SPP_VLD可以表示为式(1):

其中,当前位平面比特显著性初始值B1_org、B2_org、C0_org、C1_org、C2_org为比特所在样本之前位平面是否已经有‘1’的比特被编码,由此我们可以根据当前编码平面索引和样本中的最高非零比特平面索引比较得出。

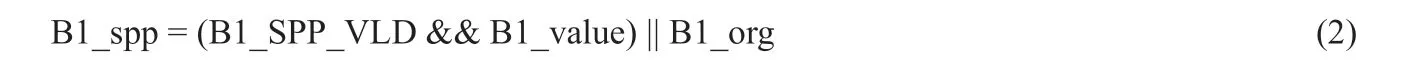

B1在显著性扫描过程之后显著性状态改变,只有一种情况,即B1属于显著性传播通道,且它的值为‘1’,我们令更新后的显著性状态为B1_spp,则可以用式(2)来表示显著性状态的改变:

显著性传播通道扫描之后是幅值细化编码通道的扫描,属于幅值细化编码通道条件为当前比特所在样本此前位平面已经有比特‘1’被编码,可以根据当前编码平面索引和样本中的最高非零比特平面索引比较得出;同时,由于此判决特性,显著性传播通道不会对样本的显著性状态做出改变。

最后是清除通道的扫描,当前位平面所有不属于显著性传播通道和幅值细化编码通道的比特均属于清除通道,由于前面已经得B1_SPP_VLD和B1_MRP_VLD,将两者相或可以得出!B1_CLP_VLD,显著性状态的变化分析方法和显著性传播通道相同,不再赘述具体细节。

本节进行了各通道的编码过程分析,为下面并行位平面编码器的设计打好了基础。

2.2 并行位平面编码器电路实现

(1)通道判决电路

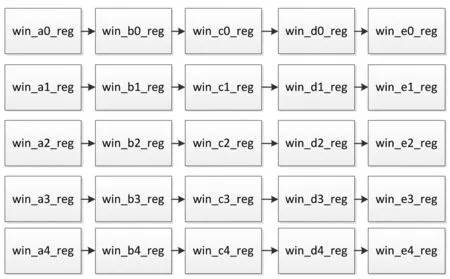

如图3所示,通道判决电路采用流水线结构进行设计,A列为未SPP编码列,B列为当前SPP编码列,C列为当前MRP编码列,D列为当前CLP编码列,E列为完成CLP编码列。

图3 通道判决电路的电路结构

电路的工作过程如下所述,第一个时钟周期,一列四个比特信息首先输入A列寄存器,A寄存器大小为4bit,格式定义为{sign,mag,α,γ},其中mag为当前比特值,α为当前比特初始显著性状态,由预处理器通过比较当前位平面索引和样本最高非零比特平面索引获得,sign为当前比特所在样本的幅值位,γ为首次MRP判据,此两者需要提供给编码原语电路,与通道判决无关,在此不做展开。

第二个时钟周期,B寄存器的格式与A寄存器相同,A列的输出作为B列的输入,同时下一条带的四个样本以上述同样的方式输入A列。

第三个时钟周期,B列的样本需要进行SPP更新,更新的结果将写入C列,C列寄存器的格式如下{sign,mag,α,γ,α_spp},其中α_spp为SPP更新后的显著性状态,同时根据上节逻辑给出四个比特的SPP_VLD,存入寄存器SPP_VLD_REG[3:0]中。

第四个时钟周期,C列的样本需要进行MRP更新,显著性状态不会发生改变,该周期需要根据原始的显著性状态给出四个比特的MRP_VLD,存入MRP_VLD_REG[3:0]中。由于下一个周期判断CLP_VLD需要用到之前的SPP_VLD信息,将SPP_VLD_REG延迟一个周期得到SPP_VLD_REG_DELAY_1。

第五个时钟周期,D列的样本需要进行CLP更新,更新的结果将写入E列,E列寄存器的格式如下{sign,mag,α,γ,α_spp,α_clp},其中α_clp为CLP更新后的显著性状态,将SPP_VLD_REG_DELAY_1和MRP_VLD_REG[3:0]按位与并取反获得CLP_VLD,将结果输入CLP_VLD_REG[3:0]中,同时将SPP_VLD_REG_DELAY1和MRP_VLD_REG分别延迟一个周期得到SPP_VLD_REG_DELAY2和MRP_VLD_REG_DELAY1。

第六个时钟周期,此时SPP_VLD_REG_DELAY2、MRP_VLD_REG_DELAY1、CLP_VLD _REG作为四个编码比特的通道判决输出,此后的每一个时钟周期,均会按条带顺顺序输出四个样本的通道判决。

(2)电路整体结构

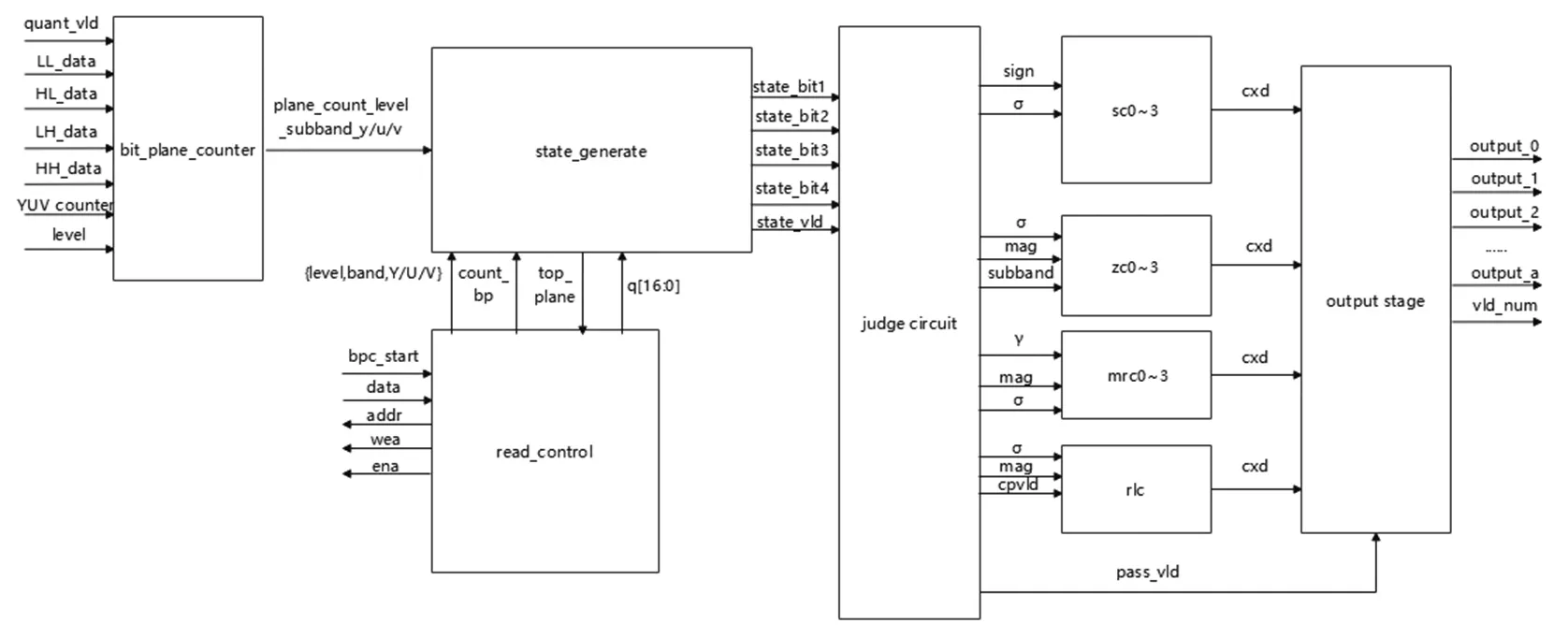

本文所设计的并行优化的位平面编码器电路结构如图4所示,电路主要由读地址控制器、比特平面计数器、状态预处理器、通道判决电路、原语编码电路和输出级电路构成。

图4 并行位平面编码器电路结构

电路上电时,位平面编码器处于空闲状态,等待小波量化系数输出完成后,小波变换核bpc_start端口将输出一个高电平脉冲,之后位平面编码器电路进入工作状态,读控制器开始输出地址信号,按照顺序从小波量化系数存储器中读取量化系数,并将读出的量化系数转发至state_generate状态预处理器中,状态经过预处理后送入通道判决电路,通道判决电路经过流水线时延后每一个周期输出一列四个比特的通道判决,以及对应的编码原语,送入相应的编码器之中,编码器的输出连同通道索引传至输出级电路,输出级电路根据各编码比特的通道判决决定各编码模块输出结果的有效性,并通过内部的排序电路将有效编码输出排至索引从0开始的连续端口上,同时输出有效数目。

3 对比分析

使用Matlab进行仿真,测试数据为32×32×8bit大小的码块,对编码所需时钟周期进行了仿真,串行方式下需要22528个时钟周期;本文所设计的位平面编码器仅需8564个时钟周期,存储资源使用量由1024bytes降至19bytes。