一种基于e-Flash工艺的DDS电路设计

王硕

(中国电子科技集团公司第十三研究所 河北省石家庄市 050001)

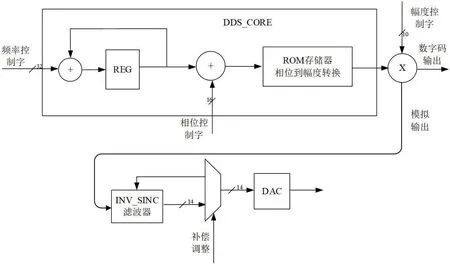

随着通信设备系统的发展,对于信号的中频的频率提出了更高的要求,对更定制,数字化,支持多种调制模式的频率合成器需求日益旺盛,目前国内设计数字频率合成器,其DDS(Direct Digital Synthesizer)中的DAC(Digital to Analog Converter)采样频率要求在100MHz 以上。数字频率合成器的原理简图如图1 所示。

图1:数字频率合成器的原理简图

基于锁相环频率源模块,其跳频速度和调制模式无法满足日益发展的通信系统需求,因此为了满足对更多形状的时钟进行直接合成,提高性能指标,随着数模混合电路工艺的发展,数字频率合成器应运而生。目前DDS 可以实现正弦波,三角波,锯齿波,方波,扫频,调幅,快速调频,捷变频等多种功能[1]。

1 e-Flash工艺

近年来,随着CMOS 电路尺寸的不断减小,性能逐步提升,与模拟、射频、存储器等拥有了更高的集成度。相比于Ⅲ-Ⅴ族化合物工艺,现在e-Flash 工艺可以实现射频电路、DDS 数字电路,ROM(Read-Only Memory)查找表电路,DAC 等模拟电路的一片式集成,从而有效的降低成本,同时可以实现高密度的存储器阵列,从而实现高性能的DDS 电路设计。为了应对高集成度的要求,需要将MCU(Micro Controller Unit)和DDS 电路进行单片集成,而MCU 必须使用Flash 作为可编程存储器,因此必须设计一款基于e-Flash 工艺的DDS 电路,以便提高系统的集成度,为后期系统的单片化,SoC(System on Chip)做准备。

本文所使用的e-Flash 工艺提供了6 层金属,4 层多晶硅栅,提供了浅槽隔离和深槽隔离来降低衬底之间的耦合,工艺还提供了顶层的厚金属,可实现高Q 值电感、多层金属板电容和多晶硅电阻等无源器件,同时支持ROM 存储器等设计。本文采用e-Flash 工艺设计了一款可生成三角波,正弦波,锯齿波,并带有调频、调幅、调相等多种功能的DDS 芯片,最高工作频率500MHz,模拟部分功耗34mA,数字部分功耗1mA/10MHz,芯片面积2*2 mm2。

2 存储器设计与应用

由于ROM 存储器的尺寸直接取决于存储器的内容,为了适配14Bit DAC,ROM 表中存储的数据位宽为14Bit。本工艺的ROM存储器,在全温下工作最差读取延时为3.5ns,因此为了满足延时的要求,需要使用2 块存储器进行分时读取,每块存储器的工作频率为250MHz[2]。

对存储器进行编码,在奇数周期读取1 号存储器数据,在偶数周期读取2 号存储器数据,通过时分复用技术,将之前电路的工作频率提高到原来的2 倍[3]。

3 数字信号发生器设计

根据信号处理的需求,本文设计了两种工作模式,单频点模式下产生需要频率功率信号,斜坡模式下产生所需扫描信号。

通过内置的数字斜坡信号发生器,可以实现幅度扫描,频率扫描,相位扫描。在本芯片设计中,为了方便配置,其扫描方向、起终点、扫描步长等均可通过寄存器配置,方便使用。

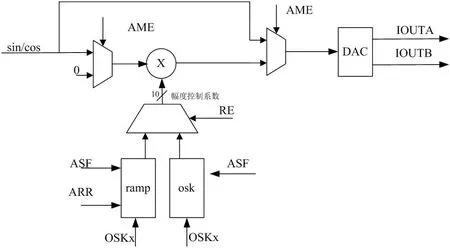

3.1 点频模式

通过上位机配置频率控制字(Frequency Control Words, FCW),相位控制字(Phase Control Words, PCW),幅度控制字(Amplitude Control Words, ACW)对电路输出的频率,相位,幅度进行调整。

其中参考时钟为Fref,PCW 用于控制正弦信号的起始相位,幅度控制位用于调整幅度范围。

其功能框图如图2 所示。

图2:DDS 核设计框图

DDS 核心电路是累加器,通过优化高速累加器的电路结构,使用高速并行加法器,成功实现了在0.13um 工艺上的单通道累加器运行在500MHz 的时钟下。

3.2 斜坡模式

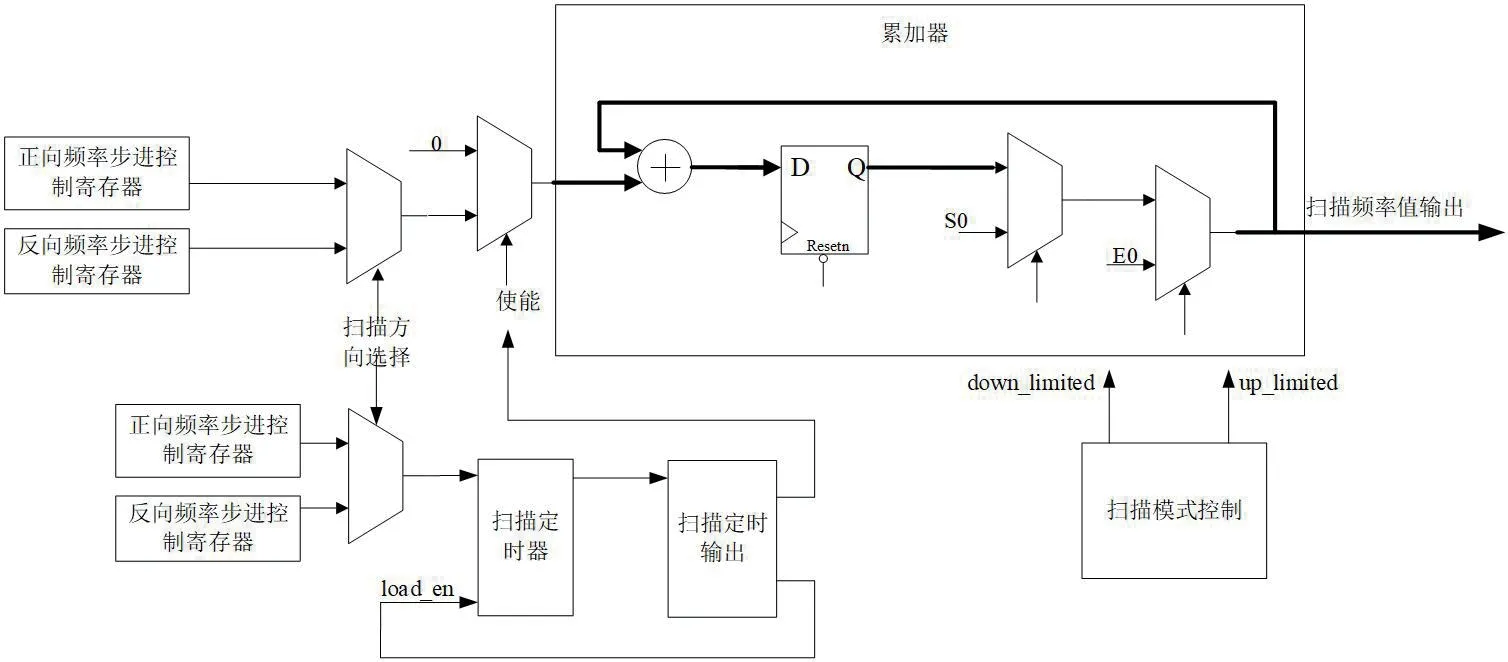

芯片内部集成了数字斜坡信号发生器,可以自由设置斜坡扫描的起点,终点的频率、相位、幅度。其中内部寄存器均可通过串口通信进行配置。其框图如图3 所示。

图3:数字斜坡发生器框图

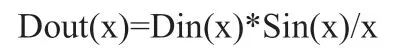

4 反Sinc滤波器设计

被采样的载波数据流是内置数模转换器(DAC)的输入信号。由于DAC 输出信号固有的零阶保持特性效应,DAC 的输出频谱会被SIN(x)/x(或Sinc)包络整形,由于其波形已知,所以可以对Sinc包络进行补偿。如果不进行补偿,则在第一奈奎斯特区间,对于设置为同样峰峰值的电压信号,输出信号频率在0.5 倍采样率其功率会下降3dB,影响信号功率平坦度。

此包络恢复功能由DAC 模块前的反Sinc 滤波器实现。反Sinc滤波器的作用相当于数字FIR 滤波器。其响应特性非常接近反Sinc包络。

通过反SINC 滤波功能。滤波器通过改变输入DAC 的数据,确保对Sinc 包络进行补偿,以避免频谱失真。

5 测试结果

芯片在标准e-Flash 工艺厂进行流片测试,流片所选工艺节点为0.13um 工艺,所选金属层数为6 层。在基准电路开启条件下,模拟部分电流为34mA。通过信号源为芯片提供400MHz 的时钟,芯片工作在400MHz 时,数字部分电流为40mA。

单频点模式下,可以输出单频点正弦信号通过频谱仪分析后的信号如图4 所示。

图4:宽带SFDR 测试图

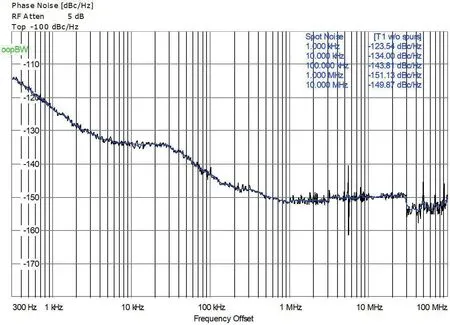

输入时钟500MHz,输出频率201MHz 时,窄带无杂散动态范围为-90dBc。如图5 所示。

图5:相位噪声测试结果

输入时钟500MHz,输出频率201MHz 时,相位噪声约-135dBc/Hz@10KHz。

6 结论

本文基于e-Flash 工艺,设计了一款用于SoC 系统的DDS 芯片。测试显示,在时钟500MHz,输出201MHz 的频率时,功率可覆盖0-8dBm,SFDR 范围为-53dBc,窄带(+/-250KHz)SFDR 为-90dBc。本芯片已在系统中得到了的应用,完全满足了系统对数字频率合成的指标要求,可以满足全温范围的工作,未来将继续展开多通道芯片的设计和多芯片的同步功能开发。