雷达杂波消除模块的模型化设计

苏刚 刘金海

摘 要:雷达杂波消除模块能最大限度降低杂波干扰,充分发挥雷达的工作性能。移动目标显示模块和恒虚警模块是雷达信号处理的两个主要模块。移动目标显示模块能成功分离雷达回波信号和干扰信号。分离出的回波信号有大量的残余信号,为了消除残余信号,必须对雷达信号进行恒虚警处理。借助FPGA开发工具,采用模型化方法设计雷达杂波消除模块,可以最大限度缩短设计周期、降低开发费用、节省硬件资源。

关键词:干扰信号;移动目标显示;恒虚警;模型化设计

中图分类号:TN957 文献标识码:A 文章编号:2096-4706(2021)05-0048-04

Modeling Design of Radar Clutter Elimination Module

SU Gang,LIU Jinhai

(School of Physics and Electronic Information,Dezhou University,Dezhou 253023,China)

Abstract:The radar clutter elimination module can reduce the clutter interference to the maximum extent and give full play to the radar working performance. Moving target display module and constant false alarm module are two main modules for radar signal processing. Moving target display module can successfully separate radar echo signal and interference signal. Separated echo signal has a large number of residual signals. In order to eliminate the residual signals,the radar signal must be carried out constant false alarm processing. With the help of FPGA development tools,the radar clutter elimination module is designed by modeling method,which can shorten the design cycle to the maximum extent,reduce the development cost and save hardware resources.

Keywords:interference signal;moving target display;constant false alarm;modeling design

0 引 言

近年来,通信技术的发展极大地扩展了数字信号处理的应用范围。以更高的速度和更低的成本实现越来越复杂的数字信号处理算法,日渐成为数字信号处理研究的重点[1]。雷达信号处理领域,对信号处理所需要的计算量提出了极高的要求[2]。传统的解决方案一般是采用多片DSP并联构成多处理器系统来实现,设计复杂度和系统功耗大幅度提升,使系统稳定性受到影响[3]。FPGA的集成度高、逻辑实现能力强、设计灵活性更好,在雷达信号处理领域的优势日渐显现,随着FPGA技术的进步,传统上的限制正在硬件和软件设计层次上逐渐被克服[4]。FPGA开发需要使用硬件描述语言,硬件描述语言提高了开发门槛,对通信专业从业者是一个巨大挑战。基于FPGA的数字电路模型化设计方法已被广泛应用于控制领域的复杂仿真和设计中,而在软件无线电领域尤其雷达信号处理领域模型化设计方法处于起步阶段,有待进一步推广应用。

杂波信号处理模块在雷达信号处理中起着十分重要的作用,是雷达信号处理的核心步骤之一,也是软件无线电技术的重要组成部分[5]。使用FPGA探索杂波处理模块的设计方法,可以为雷达信号处理提供新思路,可以解决传统设计方法工作量大、环节复杂、效率低的问题,也可为其他领域的信号处理方法提供借鉴。

1 模型化设计流程

数字电路设计若使用FPGA实现,设计周期短,易更改,无须介入实际物理层的布局布线,前期投入小,风险小。利用MATLAB软件的simulink功能,结合FPGA开发工具,可以实现数字电路的模型化设计[6]。DSP Builder是FPGA厂商开发的设计工具,把算法级和RTL级两种设计工具连接起来,最大限度地发挥了两种工具的优势,是数字电路模型化设计的必备工具[7]。DSP Builder依赖于数学分析工具MATLAB/simulink,利用simulink的Blockset,可以在simulink中进行图形化设计和仿真,通过Signal Compiler可以把MATLAB/simulink的设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd)及用于控制综合与编译的TCL脚本。而对后者的处理可以由FPGA开发软件QuartusⅡ来完成。DSP Builder支持系统、算法和硬件设计共享一个公共开发平台[8]。在算法友好的開发环境中帮助设计人员生成硬件描述语言,提供从上到下的模型化设计方案,从而缩短了FPGA开发周期。基于FPGA的数字电路模型化设计流程如图1所示。

2 移动目标显示模块

2.1 移动目标显示实现原理

与静止目标回波不同,运动目标会产生多普勒频移,运动目标回波的幅度和相位会随时间发生很大变化。移动目标显示(MTI)技术可以区分固定目标、慢速移动目标和快速运动目标。如图2所示,Sd(t)是运动目标回波信号,减去相邻回传周期内同一测距单位的信号Sd(t-Tr),固定目标将消失,慢速运动目标将大大减弱,快速运动目标的回波将保持不变,Δu(t)是得到的运动目标回波信号。后续对Δu(t)进行滤波处理,可以得到更纯净的信号。最早期的动目标显示滤波器为传统为一次对消及二次对消器,为了展宽滤波器凹口宽度从而增强杂波抑制能力可以通过增加对消次数的方式来实现。

两个脉冲分频器级联形成一个三脉冲分频器,固定三脉冲对消器的传递函数为:

H(z)=(1-z-1)(1-z-1)=(1-z-1)2 (1)

时域表达式为:

y(n)=x(n)-2x(n-1)+x(n-2) (2)

三脉冲对消器的结构如图3所示,三脉冲对消器的频率响应如图4所示。

MTI滤波模块通常用采用N阶横向FIR滤波器实现,N阶横向FIR滤波器如图5所示。其中x(n)为输入信号,h(n)为FIR滤波系数,y(n)为经过滤波后的信号;N表示FIR滤波器的抽头数,滤波器阶数为N-1。输入信号被发送到一组延迟单元,每个延迟单元的延迟时间对应于发射脉冲的重复时间。

2.2 MTI模型化设计

设置测试信号采样频率fs=24 MHz,中频f0=30 MHz,带宽B=5 MHz,时宽T=30 μs。设置T为脉冲恢复时间,构成脉冲宽度,则每个脉冲的数目就是一个点。移动目的地指示符意味着删除相同距离单位中的多个脉冲,即过滤相同距离单位中的多个脉冲,并且过滤系数分别为1、-2和1。MTI模块的模型化设计框图如图6所示。

2.3 MTI模块硬件级仿真

在算法得到验证后,可以使用Simulink中的Signal Compiler模块映射为MDL文件。启动QuartusⅡ,然后配置管脚,编译生成配置文件,利用此文件配置FPGA芯片,得到所需的MTI模块电路。在Simulink环境下,可以进行半实物仿真验证,仿真结果如图7所示。半实物仿真属于硬件级别仿真,更接近实际结果。与以往的算法级仿真不同,这种验证方法大大提高了仿真的效率和可靠性。该建模方法的算法仿真功能和与其他软件的协同功能,不仅节省了人力,而且缩短了开发周期。

3 恒虚警处理模块

3.1 恒虚警原理

雷达信号处理机由于受到干扰,往往会产生许多意想不到的处理结果。接收到的信号留下了大量的残余信号,雷达将这些残余信号误认为是有用信号。这意味着雷达回波信号具有很高的恒虚警(CFAR)概率。为了优化雷达信号的目标定位,将CFAR处理引入雷达信号处理系统中。如果虚警概率不是恒定的,处理器因虚警过多而过载,就需要对雷达信号进行CFAR处理。CFAR过程应该为雷达设置一个噪声阈值。当阈值确定后,CFAR概率会有明显的变化。

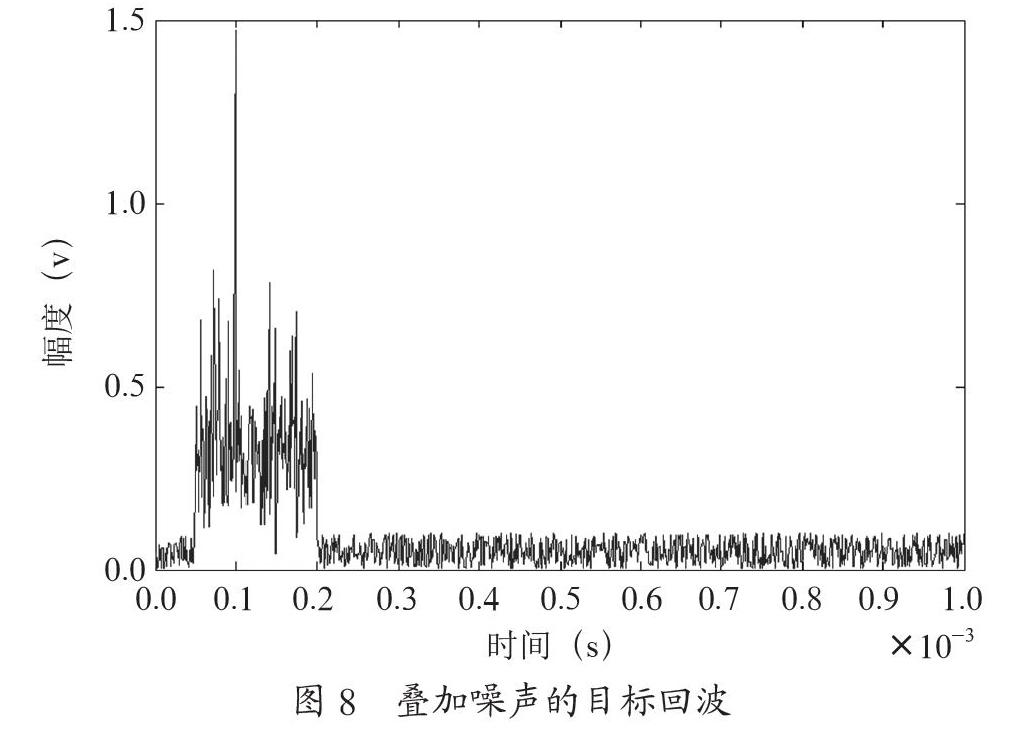

CFAR方法有两种:慢阈值CFAR和快门限CFAR。慢阈值CFAR电路用于处理受温度、电源等因素的影响而变化速率非常缓慢的内部噪声。快门限CFAR用于管理无序环境下随空间和时间而快速变化的信号。在低分辨率脉冲雷达信号处理中,杂波实际上是由多个独立单元回波的叠加引起的,因此这种无序的分布可视为瑞利分布。瑞利分布的特征与噪声的特征基本相似,叠加干扰信号的回波信号频谱如图8所示。CFAR具体实现方法是确定瑞利分布的平均值,然后用平均值对输出进行归一化。相邻小区平均CFAR电路的组成与CFAR电路结构相似。而相邻小区的平均CFAR率往往具有很强的边缘效应,边缘效应增加了虚警的可能性。

相邻单元平均CFAR电路是一种改进的信号处理方法,旨在消除无序环境中出现故障的可能性,如图9所示。在记录单元的相同范围内,选择N个参考单元并计算N个参考单元的平均值。此种处理方式在记录单元中两次确定平均值,然后选择两个平均值中的较大者作为列参考。如果一侧的提取点被弱无序占据,则该侧电路的平均值显著降低。如果一侧的提取点被强无序占据,则该侧电路的平均值显著升高。为了解决这个问题,可以在检测单元前后平均估计N个参考单元,并将平均估计的最大值作为输出。但是这样会严重降低杂波边缘外侧信号检测能力。

图10是一种降低耦合平均CFAR电路边缘外信号损耗的新方法——两侧单元平均选大CFAR电路。该电路在相邻距离单元的平均CFAR电路上进行了改进。当检测阈值固定时,虚警概率的提升往往是由噪声波动的增加引起的。根据参考单元数适当提高检测门限可以使输出虚警概率保持不变。

3.2 CFAR模块模型化设计

相邻单元平均CFAR检测方法从被检测目标邻近单元来获得杂波均值的样本。但是该方法存在很严重的杂波边缘内侧虚警增大的问题,所以一般采用改进后的两侧单元平均选大电路,如图11所示。在被识别单元格的左侧和右侧选择L单元格,在两侧计算L单元格的平均值,并选择平均值中的最大值作为输出。初始结果乘以阈值乘法器C作为检测阈值。目标两侧的自由统一是消除目标自身对阈值影响的保护单元。

3.3 CFAR模块硬件级仿真

通过对CFAR模型化设计进行仿真,得出了CFAR模块的仿真结果,仿真结果如图12所示。在硬件模块的算法得到正确验证后,可以使用Matlab中的SignalCompiler模块生成MDL文件。采用Altera的FPGA,选用VHDL语言,并自动生成一个可以打开并执行QuartusⅡ的项目文件。启动QuartusⅡ,打开本项目,可以进行模拟和时序仿真,然后配置管脚,编译生成配置文件,利用此文件配置FPGA芯片,得到所需的硬件电路。在Simulink环境下,进行半实物仿真验证。该仿真是基于FPGA的硬件级仿真,更接近实际结果。与以往的算法级仿真不同,这种验证方法大大提高了仿真的可靠性。采用QuartusⅡ直接对FPGA进行配置和验证,省去了HIL验证的三个步骤。该建模方法的算法仿真功能和与其他软件的协同功能,不仅节省了人力,而且缩短了开发周期。

4 结 论

雷达信号杂波处理是雷达信号处理中最重要的组成部分,MTI和CFAR相互协调,共同作用,精确分离出雷达回波信号。借助Matlab中的DSP builder模块进行模型化设计,然后利用FPGA芯片进行硬件级别仿真,真实可靠,事半功倍。DSP builder中的模块由Altera优化的IP核集成,与FPGA开发环境中的模块基本相同,而FPGA可以反复擦写配置。因此,该建模方法不仅节省了开发时间,而且在一定程度上节约了硬件资源。

模型化设计方法方兴未艾,现在集成电路的设计也可以参考模型化设计方法,而FPGA可以作为集成电路设计中的硬件仿真平台。应该看到的是DSP builder可以与SOPC开发结合起来,共同进行FPGA开发,所以模型化设计方法前景一片大好,FPGA工具会进一步提升信号处理的效率。

参考文献:

[1] 李小波.极化雷达目标调制模拟器设计及实现 [D].秦皇岛:燕山大学,2016.

[2] 孙大亮.可重构雷达信号处理系统的设计与实现 [D].大连:大连理工大学,2015.

[3] 肖达,刘辉,张玉华.数字下变频的零点漂移现象分析与抑制方法 [J].现代雷达,2021,43(1):71-75.

[4] 沈佳琪,靳璐.雷达信号处理中大数据量FFT实现分析 [J].电子技术与软件工程,2021(1):66-68.

[5] 周磊.中频数字化接收机的硬件研究与实现 [D].南京:南京邮电大学,2019.

[6] 付林,江伟伟,陆峻.基于矢量计算的雷达监测信号处理方法 [J].雷达与对抗,2020,40(4):5-6+37.

[7] 岳黎冬.中频信号采集及处理模块研制 [D].哈爾滨:哈尔滨工业大学,2020.

[8] 黄明慧.基于FPGA模型化设计的雷达信号处理的实现 [D].西安:西安电子科技大学,2010.

作者简介:苏刚(1988—),男,汉族,山东滨州人,通信工程师,助教,硕士,研究方向:信号处理理论及应用;刘金海(1981—),男,汉族,山东昌乐人,讲师,博士,研究方向:超宽带天线、相控阵天线和基站用高增益天线等。