FPGA在高压高速直线电机检测仪的应用研究

陶俊豪

( 中国人民解放军63801部队,四川 西昌 615042 )

0 引言

高速直线电机是一种将电能转换为高速直线运动机械能的传动装置,常用于高性能机床伺服系统、电磁推进器或磁悬浮定位平台上,控制精度可达μm量级,移动速度可达20m/s以上。在实际应用中,对直线电机进行机械性能检测,一般需要用光栅尺或磁栅尺对其位置进行编码,检测相对位置、速度、加速度等信息。此外,为了解电机的电性能,还需要测试相应位置的动态电压、电流等参数。由于电机运动速度较快,产生的正交编码、电参数数据量较大,需要在μs量级时间内进行快速数据采集与AD转换等,传统的单片机检测技术不再适用于电机测试与控制。

FPGA(Field-Programmable Gate Array)处理速度高达数百兆以上,具有高度灵活、可定制化特点,在高速实时信号处理系统中得到了广泛应用。本文以一种高压(220V工作)、高速直线电机测试仪器的设计为出发点,利用FPGA技术对其具体内容进行了研究与实现,重点研究其在电机速度、电机电压、电流检测方面的应用。

1 设计方案

直线电机的位置检测一般采用无接触式光栅尺或磁栅尺技术实现,两者差别在于测试精度和行程。由于本文的出发点是测试一种行程20mm直线电机的最大运动速度,精度要求不高,故采用低成本磁栅检测技术。磁栅尺选用上海平信机电制造有限公司的MR502C型磁栅尺,5V单电源供电,分辨率25μm,移动速度达25m/s,输出信号包含A、B、Z三路正交编码的差分信号。对正交编码器输出信号进行解调和计数的专用集成电路,如惠普公司 HCTL2000、HCT2016等产品不仅结构复杂,而且价格昂贵。采用FPGA技术较易实现滤波、解码、加减计数以及方向判别等功能,与外周电路连接便捷。在差分信号输入FPGA前需将其转换为CMOS或TTL电平以实现接口匹配。

高压电机的工作电压、电流采集利用高速隔离型16位ADC芯片AD7401实现,采用隔离式ADC不仅能消除电机运动带来的干扰,也能防止意外情况下电机高压信号串入FPGA低压信号采集处理电路,同时提高人员操作安全性。AD7401是Analog Devices公司推出的一款隔离式Sigma-Delta调制器,在20MHz外同步时钟情况下可输出16位隔离的无失真采样数据流,该数据流经FPGA进行Sinc3滤波后解码还原得到ADC数据。由于采集隔离供电,该芯片需要搭配隔离DC/DC电源模块供电。

在获取电机的正交编码和电压、电流等参数后,需将数据上传至上位机作处理,从而对电机综合性能进行分析。普通的串口传输技术波特率最高达1Mbps,传输速度慢,不适合高速数据采集处理;基于USB的传输技术虽然传输速度高达480Mbps,但接口传输复杂,数据在长距离传输中不可靠。本文采用基于千兆网络传输技术,传输速度高达1Gbps,接口简单,传输距离长,采用TCP技术后能保证可靠传输。

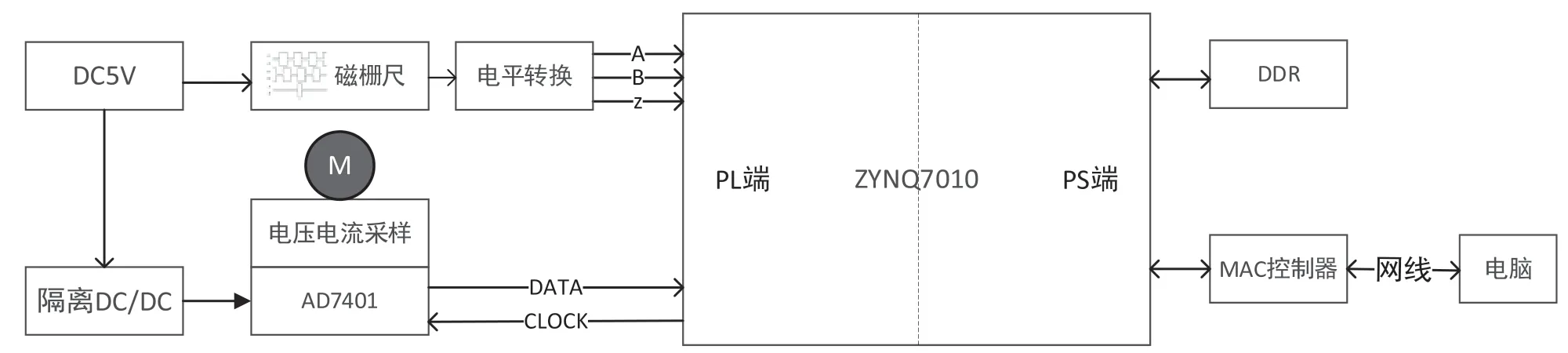

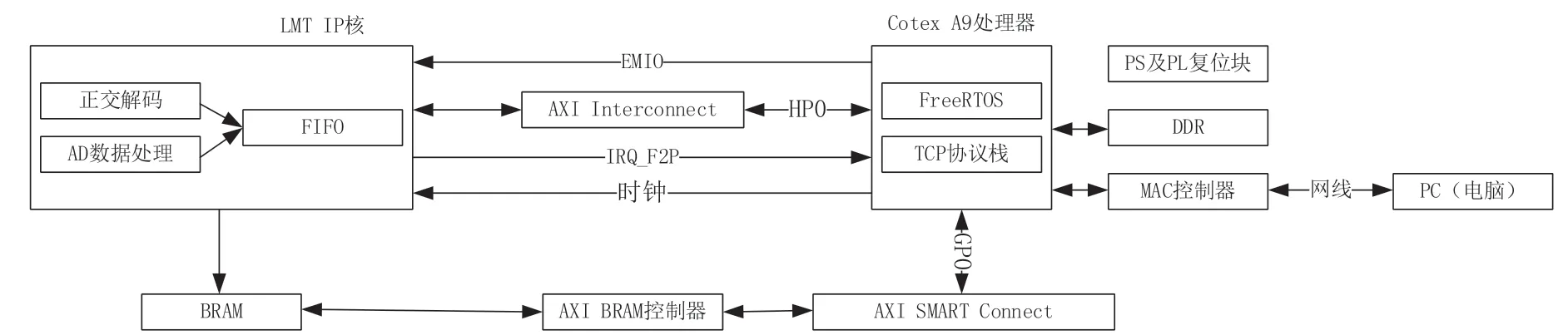

基于上述考虑,采用Xilinx公司推出的可扩展处理器平台架构ZYNQ7010芯片,该芯片将双核 ARM Cortex™-A9 处理器和 FPGA 可编程逻辑单元集成在一颗单芯片中,构成PS(Processing System)加 PL(Programmable Logic)的单芯片 SoC 解决方案。整个系统框图如图1所示。

图1 系统结构框图

由于高速电机在测试过程中产生大量数据,芯片自带的256K SRAM无法满足数据存储及传输要求,故使用DDR进行数据存储及传输。

2 电源及接口

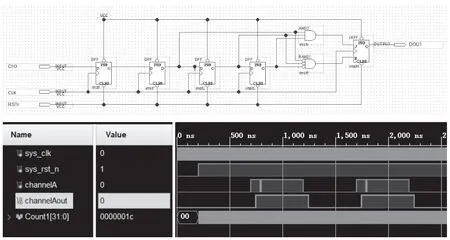

由于电机工作时通常产生大量噪声,因此在进行解码前需对采集到的正交信号进行滤波,以消除噪声干扰。在对磁栅尺输出的正交差分信号进行电平转换后,可采用数字滤波器进行噪声滤除。该滤波器由D触发器、JK触发器、三输入与门、与非门等逻辑门组成,可滤除频率大于时钟频率的杂波信号,数字滤波器及仿真波形如图2所示。

图2 数字滤波器及仿真波形

正交信号的解码由鉴相、四倍频、正反向计数等单元组成,其实现方式和仿真结果如图3所示。

图3 正交信号解码实现及仿真结果

鉴相用于判断电机前进方向,四倍频单元在正交信号的每个边沿进行计数因而频率是正交信号频率的四倍,该信号作为脉冲计数的依据。由于正交信号每个脉冲对应距离是固定的,故对四倍频信号根据方向进行计数可知电机所处位置。采用32位寄存器存储相对时间以及解码器计数值,电机运行时以第一个四倍频信号AB0上升沿作为时间的零点,在每个正交信号跳变沿记录相对时间和解码器计数值(表示相对位置),根据参数计算出电机速度和加速度等信息。

时间寄存器以1MHz的时钟进行同步计数,保证时间精度在1μs级别,提高速度计算精度。解码器计数值寄存器用最高位来表示运动方向信息,便于后续客户端解算。

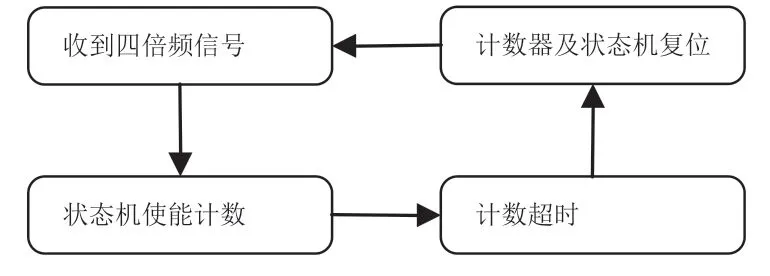

上述单元实现了正交信号的解码,但是在多次重复测试过程中正交计数器不能归零,相对时间寄存器也有溢出可能,为此需设计自复位逻辑电路,结构如图4所示。从第一次收到四倍频信号作为相对时刻0,从相对时刻0开始计算时间,超过规定时间对计数器及状态机进行复位,确保脉冲计数及相对时间的正确性。假设电机单次测试往复运动时间为100ms,可将复位时间设计为100ms以上。复位脉冲同时作为中断信号传递给处理器,表示数据采集完成。

图4 复位流程图

3 电压电流AD转换

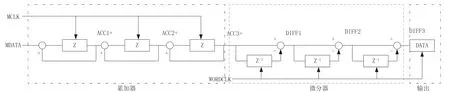

采样电路经AD7401输出至PL数据是经二阶sigma-delta (Σ-Δ)调制器调制的1位二进制数据流,需要合适的数字滤波器重建AD转换得到数值。这里采用一个Sinc3滤波器,滤波器的结构如图5所示。其中累加器采用递归型结构,以调制器时钟MCLKIN速度执行累加,实现IIR(递归型滤波器),同时利用计数器对MCLKIN进行256分频得到WORDCLK,该时钟速率也是AD转换器输出采样结果(16位)速率。WORDCLK提供至微分器以实现FIR(非递归型滤波器),即有限长单位冲激响应滤波器。WORDCLK同时驱动Sinc数据至16位输出寄存器。该16位采样数据在客户端电脑完成电压和电流数据解析。

图5 Sinc3滤波器

4 接口与通信

ZYNQ7010中PS与PL独立,无法直连进行数据通信,需要接口转换,故对其接口和通信模式进行了研究,最终通信模式如图6所示。AD转换后得到的电压电流数据和正交数据在ZYNQ7010的PL部分处理,可用vivado软件将其封装为基于AXI4总线的IP核,并对测试数据进行编码,以便与PS部分通信。

图6 PL与PS接口通信模式图

在PL端,IP核时钟由PS提供,涉及两个时钟,FCLK_CLK0供给S_AXI_HP0总线使用,FCLK_CLK1给PL端正交解码、AD采集数据使用。PL接收PS通过EMIO扩展接口发出的控制信号,包括控制电机测试开始与停止信号。电机测试过程中,由于传输数量线宽(128位)与AXI4总线线宽(32位)不一致,因此需要使用FIFO进行不同时钟域的数据缓存。IP核将FIFO编码数据通过AXI4 FULL总线传入CPU的S_AXI_HP0高速AXI总线,存入DDR指定位置。由于测试的数据量大且具有不确定性,为简化逻辑实现,测试完成后需将测试得到的数据量写入BRAM,便于CPU进行读取处理。PL解码器自复位信号通过中断接口IRQ_F2P向CPU发出中断请求,表征电机测试数据输入DDR与BRAM完成,同时将PL部分中的解码计数器清零。

在PS端,SDK软件移植FreeRTOS开源实时操作系统,为实现可靠的网络数据传输,移植了FreeRTOS+ TCP协议栈。操作系统运行后,初始化TCP协议栈及中断入口,生成两个任务:其一负责启停PL端电机测试、处理中断,通过M_AXI_GP0端口读取BRAM数值决定网络数据发送量,其二负责测试数据的网络传输,从DDR中读取BRAM指定大小的测试数据,采用基于TCP协议的服务器模式通过MAC控制器传输至千兆网,传输完成或超时后告知第一任务,以进行下一个测试。操作系统中需考虑意外导致TCP协议栈崩溃情况,一般在TCP服务器端网络传输任务中加入响应客户端重启ZYNQ7010指令函数。

在PC端,编写TCP通讯客户端,实时接收TCP数据包,运用多线程技术完成数据的实时存储。由于测试数据量较大,实时解算编码数据容易造成网络通讯缓慢,不利于实时检测,因此在所有测试完毕后再进行数据解算和处理,得到电机相关参数。

5 结语

在使用微相科技的MZ7010评估板基础上另行设计接口板,完成电压电流采集电路、正交编码器电平转换等功能,编写基于MFC的客户端程序,进行电机测试工作,实现了预期效果。