航天器嵌入式软件在轨维护及工程实现

纪春国,卢 丹,崔 阳,赵笙罡

(1.中国科学院微小卫星创新研究院,上海 201210;2.上海格思信息技术有限公司,上海 201210)

目前,世界各国航天事业飞速发展,航天在轨测控任务飞速增长,测控需求与日剧增。这就对航天测控分系统提出了更高的要求,主要体现在测控分系统的复杂度比之前有很大提升,传统航天测控分系统[1]模拟设备由于其设计复杂度高,调试、测试、联试难度大,周期长,再加上其大体积、高功耗的特点,很难适应航天测控分系统的要求,导致航天器在轨维护困难、在轨故障恢复工作难以快速实现,利用软件无线电技术[2]进行数字化处理已成趋势。采用数字化技术,利用可编程逻辑器件FPGA 和CPU 芯片进行设计[3],使设备简单化、轻型化、小型化、模块化,并能实现低功耗且调试周期大大缩短,可以满足多种测控需求。但是,由于采用了软件无线电技术,软件在空间辐照环境中长时间运行,必然会出现单粒子翻转现象,尤其对基于SRAM 型FPGA 更容易发生此现象,使得软件所实现的功能性能异常,从而导致测控分系统无法完成前向遥控指令的接收和反向遥测数据的发送,进而无法完成在轨测控任务,这就急需在轨动态维护嵌入式软件来及时补救由于单粒子翻转带来的损失[4]。

为了便于航天器嵌入式软件在轨重构,并使其具备在轨修改能力,提出了一种针对航天器嵌入式软件安全有效的在轨更新维护方法,该方案基于抗单粒子能力免疫反熔丝FPGA 实现在轨对DSP 和SRAM 型FPGA 程序的动态加载[5],从而实现在轨重构,并进行了工程实现。

1 方案设计

航天器测控分系统通过天馈系统接收由地面测控站发送的前向测量与遥控无线微波信号,首先进行射频带通滤波、下变频、中频滤波、放大、AGC,带通滤波后输出供基带AD 数字采集,AD 数字采集后在SRAM 型FPGA 中进行中频信号的捕获、跟踪、位同步、帧同步后进行译码,译码后提取遥控信号解析并执行;利用下行测量帧采样上行跟踪出来的测量信息,根据下行帧协议完成组帧后进行扩频、成型滤波、调制,同时对自身遥测进行组帧、扩频、成型滤波、调制输出给DA 进行数模变换到模拟中频信号后再进行中频滤波、放大、上变频到射频后,再进行滤波、驱放、滤波、末级功率放大输出到天线子系统,天线子系统向空间辐射无线微波信号,发送给地面测控站,地面测控站通过天线接收该无线信号,进行滤波、放大、下变频到中频后,发送给基带模块进行AD 采样,完成捕获跟踪,并解调出下行数据,提取出上行测量信息,与地面测控站上行发送的测量信息进行联合结算,共同完成对航天器的距离测量、速度测量和遥控遥测等功能,完成航天器的测定轨功能。

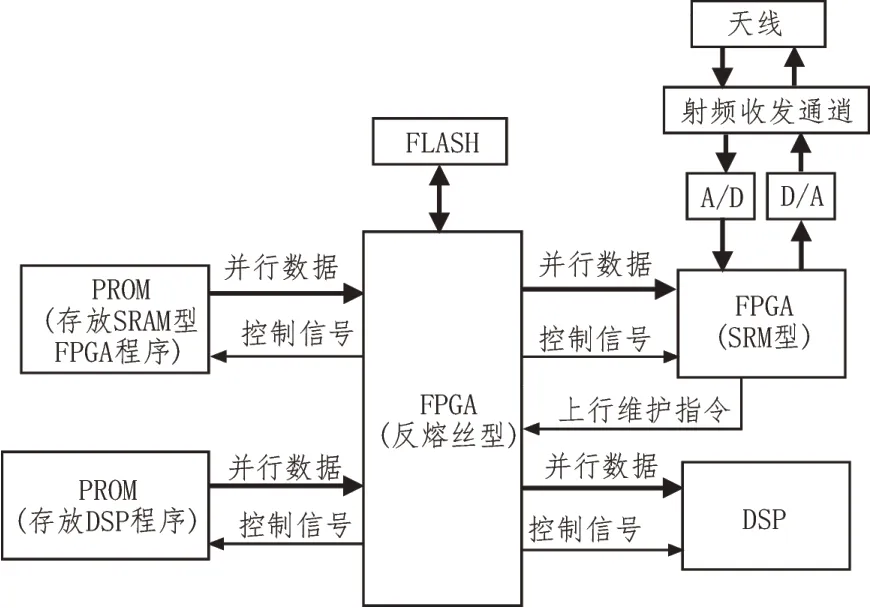

如图1 所示,由于反熔丝FPGA 可靠性较高,因此由其负责对SRAM 型FPGA 和DSP 程序的控制,其是该方案的重要组成部分,主要完成对SRAM 型FPGA 的全局配置和动态刷新功能,同时负责DSP 程序的重新加载。SRM 型FPGA 完成无线遥控指令的解调、解帧,并将上行维护指令发送给反熔丝型FPGA,由反熔丝型FPGA 完成对存放SRM 型FPGA程序和存放DSP 程序的PROM 进行在线动态加载[6],硬件实现框图如图1 所示。

图1 硬件实现框图

如图1 所示,SRAM 型FPGA 采用Xilinx 公司A7系列的低功耗FPGA XQ7A200T,该系列FPGA 是一款高性价比FPGA,具有高性能、低功耗、轻型化的特征,具有高速收发器及DSP 处理功能。该系列FPGA 支持1 Gbps DDR3,是Xilinx 公司低成本、低功耗应用的最佳选择器件,比如软件无线电(SDR)技术、机器人视觉、无线系统信号处理。A7 系列FPGA对高速串行收发器、高性能DSP、高吞吐量的低功耗应用模式进行了优化。XQ7A200T 片内资源包含215K 逻辑单元,13 Mb BRAM,740 个DSP 乘法器,16个收发器,每个收发器速度为6.6 Gb/s,4 个Gen2 PCIe 接口,500 个I/O 引脚[7]。

DSP 采用美国TI公司的C6000 系 列DSP 芯片TMS320C6713,是32 位高速浮点型DSP,时钟最高频率为300 MHz[8]。采用超长指令字结构,32 位单指令字长,每个指令包里包含8 个指令,总长度为256 位。每个256 位的指令包可分配到8 个处理单元,且8 个单元可以同时运行,最大处理能力达2.4 GIPS。采用二级缓存处理,4 kB 程序缓冲L1P,4 kB 数据缓冲L1D,256 kB 额外匹配内存L2[9]。32 位外部 存储器EMIF 接口,可与SRAM、EPROM、Flash、SBSRAM 和SDRAM 等器件进行无缝连接。具有DMA、EDMA、EMIF 等丰富的外设扩展总线,以及主机口、I/O 端口操作等功能,多通道SPI 串口,可以通过配置使能实现多种串行通信功能以及两个32位定时器等[10]。

反熔丝FPGA 主要完成的功能如下:

1)对SRAM 型FPGA 完成全局配置和动态刷新,并完成DSP 程序的动态加载;

2)接收SRAM 型FPGA 发送来的上行维护指令,完成在轨动态加载、全局复位等在轨维护;

3)监控SRAM 型FPGA 和DSP 是否有单粒子翻转,如果在不断电的情况下重新加载程序,则实现在线自动维护功能。

SRM 型FPGA 主要完成的功能如下:

1)对上行无线指令伪码采用滑动相关,载波采用串行搜索的方法,完成载波、伪码的二维捕获[11],完成二维捕获后,载波通过二阶FLL 辅助三阶PLL实现载波在高动态情况下的快速跟踪,伪码通过载波辅助二阶码环的方式进行跟踪,跟踪上以后进行位同步并解帧;对下行遥测信号进行组帧、扩频、成型滤波、调制;对下行测量信号进行组帧、扩频、成型滤波、调制后输出[12];

2)把解帧后的上行维护指令发送给反熔丝型FPGA,由该FPGA 完成指令解析并执行。

上行无线维护指令包括:

①在轨实现对SRAM 型FPGA 的动态加载;

②在轨实现对SRAM 型FPGA 的动态刷新;

③在轨实现DSP 的动态加载;

④在轨实现DSP 全局复位;

⑤在轨实现SRAM 型FPGA 全局复位。

1.1 SRAM型FPGA在轨维护方案

在XQ7A200T 和存储程序的PROM 芯片之间增加一片反熔丝FPGA,利用反熔丝芯片对单粒子免疫的能力充当该系统的主控器件,负责从PROM 芯片中读取帧数据并进行解析、校验,校验无误后写入FPGA 完成配置,同时读取XQ7A200T 的配置区,当发现回读的配置区数据有错误时,重新从RROM 中读取对应的配置区数据,对错误的数据进行重新配置,从而使XQ7A200T 正常工作。

主控器采用对单粒子免疫的反熔丝FPGA,通过slave selectmap 接口与XQ7A200T 器件进行连接,完成的功能有:

1)产生模拟XQ7A200T 器件的slave selectmap接口时序,用于配置XQ7A200T 器件;

2)产生模拟PROM 的读写接口时序,用于反熔丝FPGA 从PROM 中读取预存的程序数据;

3)通过固定方式从XQ7A200T FPGA 的配置区读取配置数据,同时读取预存在PROM 中的对应配置数据,二者读出数据后缓存于反熔丝FPGA 的寄存器组中;

4)对从XQ7A200T FPGA 的配置区读取的配置数据和从PROM 中读取的配置数据进行比对,若比对结果有误,用从PROM 中读取的配置数据更新FPGA 内的配置数据,即把从PROM 中读取的配置数据写入FPGA 相应的位置,从而完成重新配置。

反熔丝FPGA 功能主要有三部分:全局配置、单粒子翻转检测、重配置。

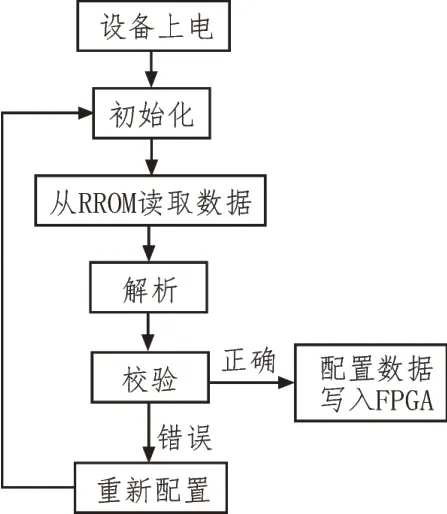

设备上电后,反熔丝FPGA 首先完成自身加载,加载成功后反熔丝FPGA 程序自动运行。给XQ7A 200T FPGA 复位,并使该芯片进入配置状态。当XQ7A200T FPGA 内部初始化完成后,在FPGA 芯片的int_b 引脚上输出高电平,然后把从RROM 中读出并解帧后的配置数据写入FPGA 配置区,把所有的配置数据全部写入FPGA后,FPGA在done引脚上输出配置成功标志,反熔丝FPGA 进入SEU 巡检状态,实时检测单粒子翻转情况,动态配置流程如图2所示[13]。

图2 动态配置流程图

在SEU 巡检过程中,反熔丝FPGA 不断检测XQ7A200T FPGA 内部配置区是否异常,通过往FAR 寄存器写入一个固定数据,然后回读该寄存器的值并与写入的数据进行比对,当比对结果正确,则反熔丝FPGA 开始依次按配置列读取XQ7A200T FPGA 配置区中的配置数据,并与从PROM 中读出并通过解帧后的配置数据进行CRC 校验,若回读的配置数据与从PROM 中读取的配置数据的CRC 结果相同,则认为该配置帧没有发生单粒子翻转现象,若CRC 结果不同,则认为该配置帧发生了单粒子翻转,则需要重新进行局部配置,即把从PROM中读出的该列的原始配置数据进行重配置,从而消除单粒子现象[14]。

为实现XQ7A200T FPGA 内控制类寄存器的准确性,反熔丝FPGA 定时100 ms 读取XQ7A200T FPGA 状态寄存器并进行正确性检查。

为保证反熔丝FPGA 可靠工作,对FPGA 程序进行三模冗余,对通过SPI 总线从XQ7A200T FPGA 寄存器内读出的锁定信息、配置状态信息、关键控制量、复位等重要信号进行三取二判决后再使用,从而保证反熔丝FPGA 不受单粒子翻转影响,使其正常工作。

反熔丝FPGA 软件上电初始化后,在500 ms 内完成管理模式设置、伪码抽头及初相配置、整机遥测量采集、组帧等工作。

1.2 DSP在轨维护方案

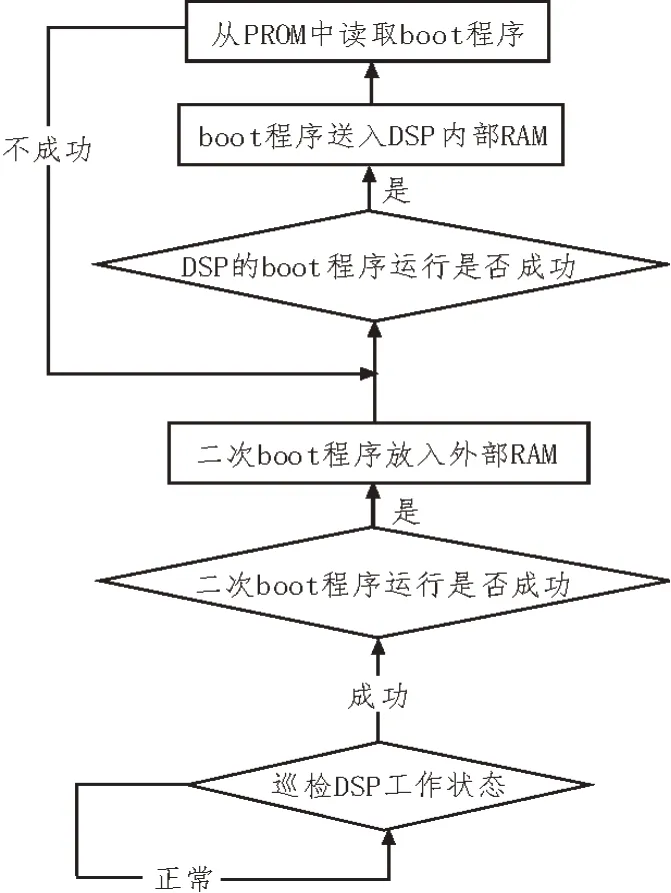

DSP 在轨维护流程图如图3 所示。

图3 反熔丝FPGA动态维护DSP流程图

反熔丝FPGA 动态加载DSP 程序流程如下[15]:

1)DSP 一次boot 程序通过反熔丝FPGA 读取PROM 中的数据,发送到DSP 内的SRAM 中;

2)DSP 运行引导程序,运行完该引导程序后,输出成功标志;

3)反熔丝FPGA 检测到该标志成功后,启动读取二次boot,从RPOM 中读取数据写入FPGA 的外挂SRAM 中,程序开始运行,并输出二次boot成功标志;

4)反熔丝FPGA 此后一直检测DSP 状态,发现异常就回到1),重新执行。

1.3 在轨FLASH程序修改方案

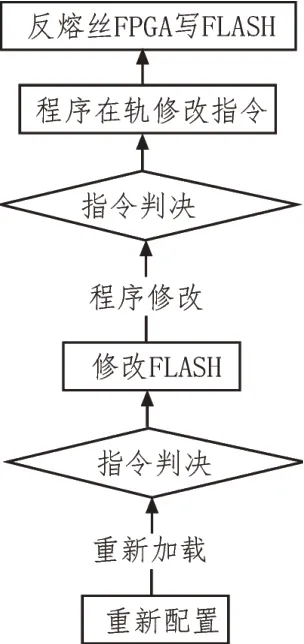

通过无线信道上行代码修改指令通知反熔丝FPGA,收到更新指令后,将对应模块的FLASH 区擦除,将新的代码写到对应的FLASH 空间,并重新加载程序,完成代码的更新[16],实现流程如图4 所示。

图4 在轨动态修改FLASH程序流程图

2 结论

航天器嵌入式软件在轨重新加载、动态修改是未来航天器在轨维护的主要发展方向。文中给出了在轨动态维护的方案,并加以应用,已得到了飞行试验验证,设计思想合理可行,能满足航天器软件在轨高可靠动态维护,提高了航天器嵌入式软件的稳健性,为顺利完成航天既定任务增加了保障。