基于FPGA的实时信号捕获算法设计与实现

王健

(中国电子科技集团公司第七研究所 广东省广州市 510220)

1 引言

信号捕获是指在无线通信接收机中接收信号进行连续不断的检测,判断何收到是有效信号的算法[1][2]。是自动增益控制、同步、信道估计及解调等后续信号处理算法的基础。在有效信号未捕获而进行后续的处理时,一方面噪声信号被当做有效信号而处理会导致错误的结果,尤其是增益控制和信道估计[3],另一方面接收机的工作在处理噪声而造成资源浪费,因此信号捕获是接收机不可缺少的部分。接收机在进行信号捕获时,实时信号捕获结果能够降低接收机信号处理的时延以及接收数据缓存资源。

2 信号捕获算法原理

信号捕获算法包括信号盲检测以及基于导频序列的信号捕获[4]。其中盲检测由于在低信噪比下性能较差而极少使用。本文采用基于导频序列的信号捕获算法。为了在接收机获得尽可能多的接收能量,导频序列应当具备良好的伪随机特征。本文采用伪随机序列(PN 序列)作为导频序列[5][6]。

接收机进行信号捕获采用基于滑动窗的信号相关的算法,定义导频序列长度为Ls,则该序列的相关值计算如下式所示:

如图1 所示为相关能量计算仿真结果,由图中可以看出在相关峰值处由多个能量值大于16,且其他位置能量明显小于16。

3 信号捕获算法实现

由公式(1)可以看出,捕获算法的运算量与序列长度成正比例关系,为了获得实时的运算结果,本文选择FPGA 实现该算法。由于FPGA 具备并行运算的能力,加上先进的流水线设计,本文的实现方案能在每一个采样点后立即得到该位置接收序列的相关能量值。

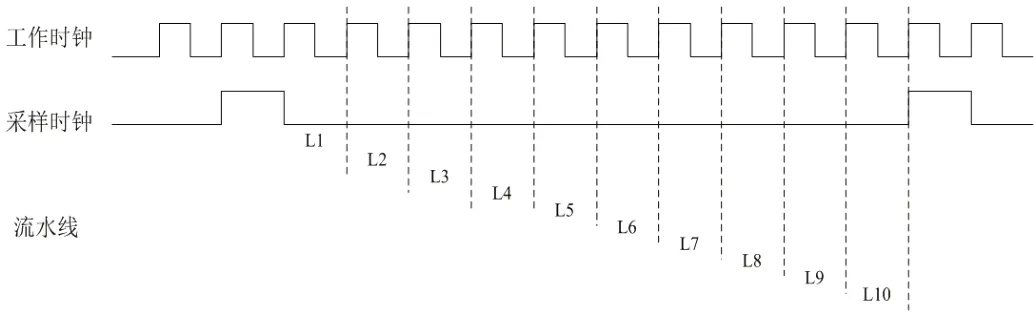

本文以导频序列长度为64 为例,FPGA 模块的工作时钟为采样时钟的10 倍,接收数据为正交IQ 数据[10],公式(1)的分子/分母并行计算,定义公式(1)表示如下:其中,X 表示分子计算,Y 表示分母计算,FPGA 流水线设计图2 所示,完成一次采样序列计算共需要10 级流水线。

图1:相关能量计算仿真

图2:流水线计算原理图

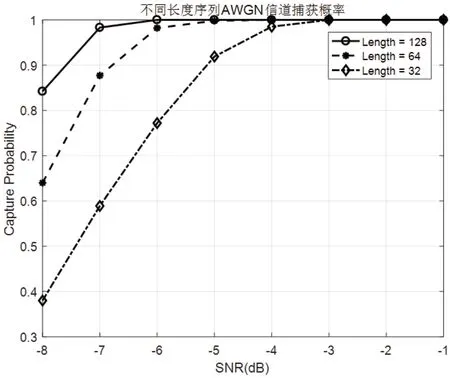

图3:不同序列长度捕获概率原理仿真结果

图2 中的各级流水线计算内容设计如表1 所示。

表1

4 结果分析

图4:FPGA 实现仿真结果

4.1 原理仿真

通过matlab 进行了信号捕获算法的原理性仿真,仿真结果如图3 所示,分别仿真了序列长度为16、32、64 时在AWGN 信道环境下的捕获概率性能。由图中可以看出随着序列长度的增加,在相同信噪比下,捕获概率大幅增加。因此尽可能选择长度较长的导频序列。

4.2 实现仿真

通过modelsim 软件对FPGA 实现进行了功能仿真,仿真结果如图4 所示,从图中可以看出在导频序列接收完毕后可以立刻得到相关峰值,表明实现的算法能够获得与原理仿真相同的结果,且在当前采样点内即可计算得出采样序列的计算结果,具有较高的实时性。

5 总结

本文设计了一种基于伪随机序列的实时信号捕获算法,并通过FPGA 进行了实现验证。算法原理仿真结果表明在低信噪比下,能够获得优良的信号捕获概率。实现结果表明能够获得高实时性的结果。未来可以通过算法优化以支持不同长度的导频序列。