一种应用于CAN 收发器的宽输入范围的迟滞比较器设计*

冯世勤,冯全源

(西南交通大学 微电子研究所,四川 成都 611756)

0 引言

CAN 总线作为一种现场总线,因为其可靠安全、实时通信和灵活控制的特点,在工程实践中广受工程师的欢迎[1]。CAN 总线整体由物理总线、收发器和控制单元三部分构成。CAN 收发器是负责MCU 或DSP 等CAN 控制单元和物理总线之间信号传递的结构[2]。CAN 总线上的信号CANH 和CANL 是摆幅为-12~12 V 的差分电压信号,而CAN 控制单元仅识别数字信号,所以CAN 收发器中的比较器需要将共模范围为-12~12 V 的模拟信号转化为0~5 V 的串行数字信号。CAN 收发器中比较器的性能对整个网络系统的安全性、可靠性和电磁兼容性起到了关键作用[3]。本文设计的比较器目的就是将总线信号CANH 和CANL 得到的差分信号VID 转化为数字信号,比较器输出的迟滞范围约为108.9 mV。

1 传统的迟滞比较器

模拟电路常见的结构中,迟滞比较器可以实现模拟信号到数字信号的转换,还可以降低电源噪声和外界干扰等因素对输出的影响,使得电路可以在复杂的环境中使用[4]。传统内部正反馈迟滞比较器如图1 所示。

图1 传统内部正反馈迟滞比较器

以图1(a)为例,内部正反馈迟滞比较器基本的工作原理为:电路中有两条反馈通路,第一条通路是A 点信号由共源极接法的MP1 反向放大回到A 点,属于串联电流负反馈;第二条通路是A 点信号由MP2、MP3 两级放大回到A 点,属于并联电压正反馈。设计时要保证正反馈系数大于负反馈系数,电路整体保持正反馈,这样电压传输曲线就会呈现出迟滞的特性[5]。

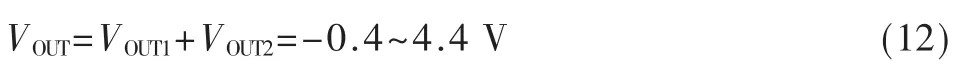

如图1(a)所示的使用NMOS 作为输入管的迟滞比较器,使MN1 处在饱和区有:

得到输入共模范围为:

由式(3)可知,输入电压最低为一个NMOS 过驱动电压和一个阈值电压,约为0.9 V。宽长比设置合理的话,输入共模范围最高可高于VDD。

但是即使使用PMOS 作为输入管,如图1(b)所示,输入共模范围为:

由式(4)可知,输入电平最低可以是负电压。

文献[6,7]同时使用NMOS 和PMOS 作为输入管,当NMOS 输入管截止的时候,PMOS 输入管还可以工作,同理PMOS 输入管截止的时候,NMOS 输入管还可以工作。这样可以使比较器获得轨到轨的输入共模范围。

但是以上结构仍然不能处理超过电源范围的电压,因此本文采取的方法是将-12~12 V 先转化为0~5 V 的电压,再进行比较。

2 本文提出的比较器结构

2.1 比较器整体架构

本文提出的比较器结构共分为三部分,如图2 所示。先是利用电阻将输入的差分电压和电源电压线性叠加,得到-0.4~4.4 V 的电压;第二级利用全差分运放钳位,稳定电压,这样就实现差模输入到共模输出的线性转换;有R0=R1=R2=R3,理想运放虚断,应用基尔霍夫电流定律可以得到:

图2 本文提出的比较器的整体架构图

因而稳定后的输出电压为:

又根据运放虚短的特性,Vi+=Vi-,因此:

从上式可知:差分信号VID并没有变化,只是承载的电平变大,可以增强差分信号对外界干扰的抵抗能力,变得更加稳定[8]。

最后一级是对尾电流进行温度补偿的迟滞比较器,比较得出数字信号。

2.2 电平线性转化

第一个模块实现的功能是将总线上的差分信号从-12~12 V 的电平转化到0~5 V 这一后级电路可以处理的电平范围内。

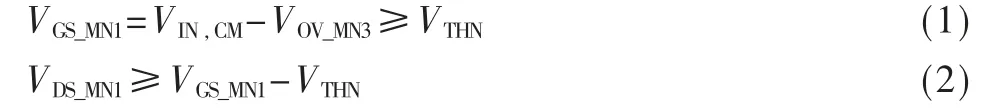

如图3 所示,采用电阻分压的方法将电源电压和输入信号进行线性叠加得到-0.4~4.4 V 的电压。在图1中,将其他部分电路视为一个负载,加上后级负载,这个电压可能会有微小的变化,但是负载变化对VH和VL影响一样,差分信号VH-VL基本消除了负载的影响。

图3 VIN 线性转化

设计有R0=R2,R1=2R0,利用叠加定理计算,可以得到如下结果。

令VIN=0,有:

令VDD=0,有:

所以得出:

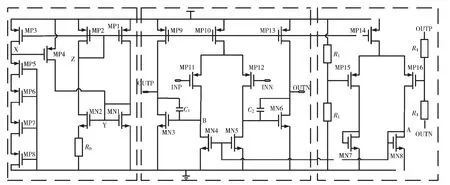

2.3 运放以及偏置电路

全差分运放相比单端输出的运放,具有输出摆幅大、共模抑制比好、能够有效抑制偶次谐波的优点[9];再加上运放需要高增益以保证高精度,因此本文设计的运放为采用密勒补偿的全差分两级运放。第一级为电流源做负载的差分输入级,采用PMOS 作为输入管。而使用电流源做负载可以提高电路的PSRR,同时可以提高增益[10]。只考虑沟道长度调制效应,且为简便计算,将NMOS 和PMOS 输出阻抗简化为rON和rOP,输入级增益为:

第二级为电流源做负载的共源极,进一步增大了增益,第二级增益为:

运放总的直流增益为:

为解决两级运放的稳定性问题,引入密勒补偿。密勒补偿不仅降低了所需的电容值,还带来了“极点分裂”效应,就是使两级间的极点向原点移动,使输出极点向远离原点的方向移动,提高了运放的相位裕度[11]。

全差分运放的共模输出电压不能通过差分信号的负反馈来控制,因此需要设计共模反馈电路保证共模点钳位在电源电压的一半即2.5 V。因为在高增益运算放大器中,顶部和底部电流源存在的随机失配会导致共模电平显著的变化,这种现象可能会导致运放的失效,因而需要采用共模反馈技术稳定运放的共模点[12]。先采用电阻分压的方法得到电源电压的一半即2.5 V 的参考电压,再用电阻分压的方法得到运放输出共模电压和参考电压进行比较,输出共模点大于2.5 V,MP16 所在支路电流减小,将二极管接法的MN8 视为恒定负载,负载上的压降减小,A 点电压减小,所以电流源MN4、MN5栅压下降,各自电流减小,等效阻抗rON增大,B 点电压增加,因为共源极增益为负,OUTP 和OUTN 电压减小。输出共模点小于2.5 V 的情况类似。这样就实现了通过共模反馈调节输出的共模电平,保证运放工作在线性区域[13]。

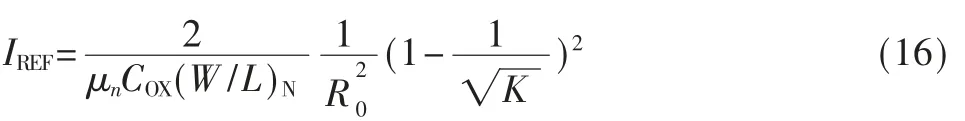

K为MN2与MN1宽长之比,(W/L)N是MN1的宽长比,与电源无关的偏置电流为:

启动电路可以使偏置电路摆脱零偏置点,进入正常工作状态[14]。本文的启动电路的工作原理是:电路未上电时,MP3 未开启,X 点为0,MP4 开启,慢慢拉高Y 点电位,MN1、MN2 开启,拉高了Z 点电位,从而开启了MP1、MP2,进一步开启了MP3,MP5~MP8 为二级管接法,因此X 点电位慢慢地拉高,将MP4 关断,实现了降低功耗的目的。

图4 本文采用运放的结构

2.4 简单温度补偿的迟滞比较器

如图5 所示,本文采用的迟滞比较器为两级,第一级和图1(a)所示输入级一样,使得电路整体呈现正反馈,第二级为电流源做负载的共源极放大电路的输出级,提供合理的输出摆幅和输出阻抗。偏置电路和运放中的类似,区别在于做了简单的温度补偿,采用R0、R1两个温度系数相反的电阻,减小了温度对偏置电流的影响,使得迟滞比较器中MN4 提供的尾电流受温度变化影响较小,从而补偿了比较器的迟滞范围。

图5 本文采用迟滞比较器的结构

3 仿真结果及分析

基于VIS 0.4 μm BCD 工艺,使用Hspice 对电路性能进行了仿真验证。

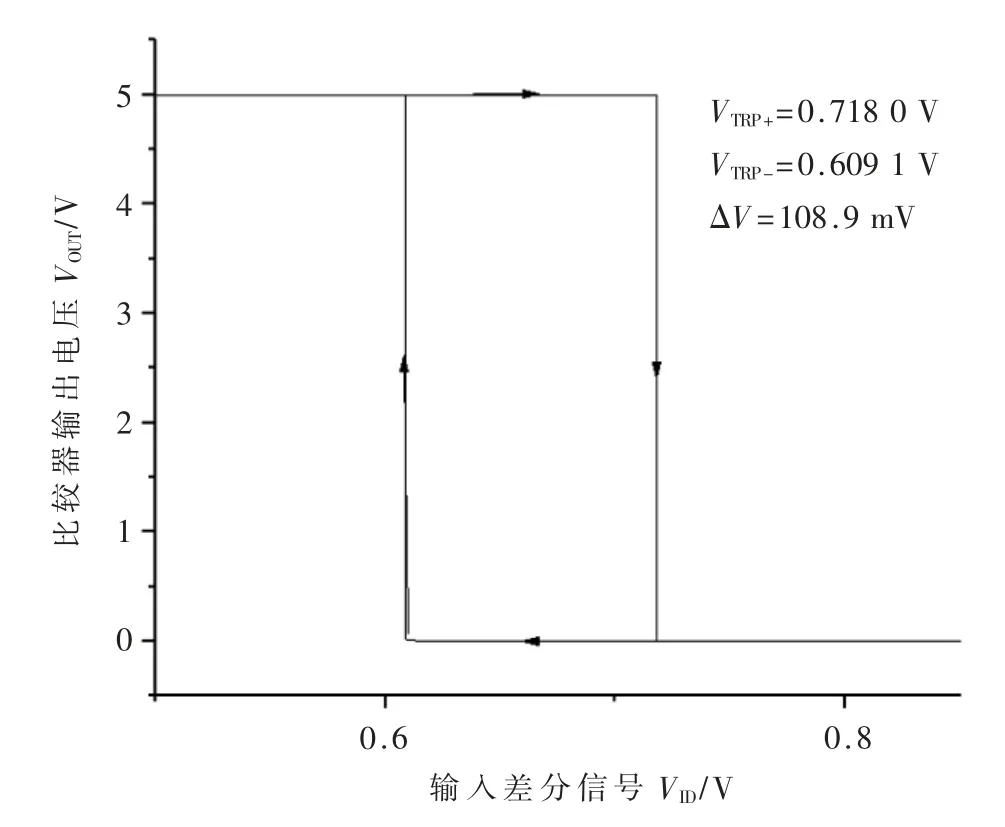

为了检验电路迟滞特性,首先通过直流仿真查看常温(即25 ℃),TT 工艺角下的迟滞曲线,如图6 所示,测量翻转阈值电压,可计算得到迟滞门限电压为108.9 mV。

图6 本文设计的比较器的迟滞特性曲线

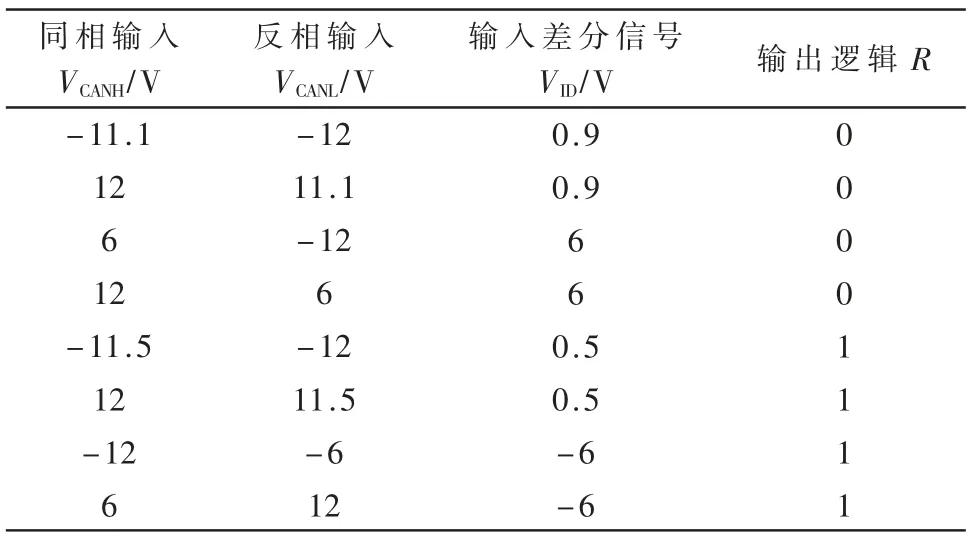

在电源电压5 V,温度为25 ℃下,进行瞬态仿真,表1展示了输入输出电压,说明本文所设计的比较器正确地将差分信号转化为数字信号。

表1 比较器逻辑功能仿真结果

TT 工艺角下,直流仿真-40 ℃~125 ℃内多个温度节点下的迟滞电压,拟合得到如图7 所示的曲线。

图7 迟滞门限电压随温度的变化

文献[15]设计的迟滞比较器的迟滞电压在0~85 ℃范围内温度系数为0.11 mV/℃。本文设计的迟滞比较器的迟滞门限电压在-40 ℃~125 ℃范围内的变化最大为9.16 mV,温度系数为0.055 5 mV/℃。说明本文对迟滞比较器尾电流的温度补偿有效。

4 结论

本文提出了一款宽输入范围的全差分迟滞比较器。通过仿真验证,电路能够将-12~12 V 范围内的差分输入信号准确地转化为数字信号。迟滞门限电压温度系数为0.055 5 mV/℃,满足工业级应用。下一步将研究减小器件失配对迟滞门限电压的影响。