TSV等效电路模型建立及分析

付颜龙 王圆 赵晓宇

摘 要:硅通孔技术(TSV)是一种实现三维集成电路的方法。为了加快三维集成电路的制造测试速度,必须对TSV结构精确建模。该文提出了一种利用CAD工具提取TSV电路模型的方法。通过三维全波模拟,可揭示常见的 TSV参数和故障对TSV电路模型的影响。该文方法所提取的模型表明,衬底电导率对TSV故障的表征有较大的影响,相对较大的针洞不会改变TSV特征参数。

关键词:三维集成电路 参数提取 TSV分析 TSV故障

中图分类号:TN40 文献标识码:A文章编号:1672-3791(2021)04(a)-0047-04

Establishment and Analysis of TSV Equivalent Circuit Model

FU Yanlong WANG Yuan ZHAO Xiaoyu

(Ordos Institute of Applied Technology, Ordos, Inner Mongolia Autonomous Region, 017000 China)

Abstract: Through Silicon Via (TSV) is a technology for realizing three-dimensional integrated circuits. In order to speed up the manufacturing and testing speed of 3D integrated circuits, TSV must be accurately modeled. This paper presents a method to extract TSV circuit model using CAD tools. Through the three-dimensional full-wave simulation, the influence of common TSV parameters and faults on the TSV circuit model is revealed. The extracted model shows that the substrate conductivity has a greater impact on the characterization of TSV faults, and relatively large pinholes will not change the TSV characteristic parameters.

Key Words: 3D integrated Circuit; Parameter Extraction; TSV Analysis; TSV Fault

传统CMOS工艺的尺度减小速度逐渐放缓,三维集成电路是摩尔定律之外(More than Moore)的一种可能选择[1-2]。硅通孔技术(Through Silicon Via,TSV)是三维集成电路的关键技术,它能够实现芯片之间的垂直连接,缩短延迟时间,并提供极为密集的IO连接[3]。随着TSV制造技术的发展,准确、高效地了解TSV电磁特性对于三维集成电路系统信号完整性至关重要[4-5]。开发有效的3D集成电路测试方法很有必要,以便尽量减少制造成本和测试时间。TSV存在诸如针孔和空洞类型的缺陷,这些缺陷会影响3D集成电路的性能[6-7]。TSV电路模型可以使用三维全波模擬,其中电场和磁场计算在整个三维结构使用麦克斯韦方程。与基于电路理论的模型相比,从全波仿真中提取的TSV模型有望揭示更多细节。

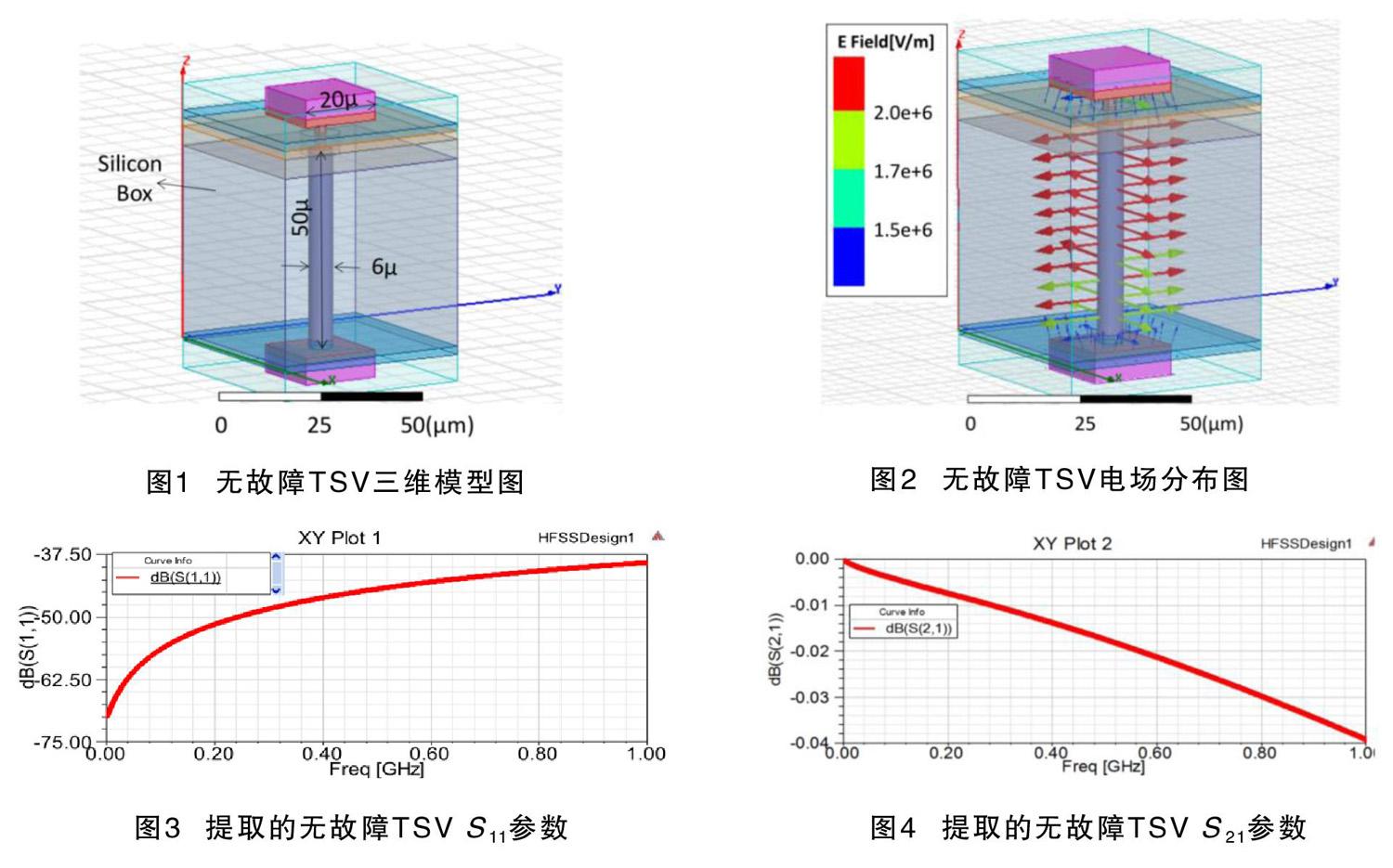

1 无故障TSV模型建立

在HFSS中建立无故障TSV模型(见图1)。

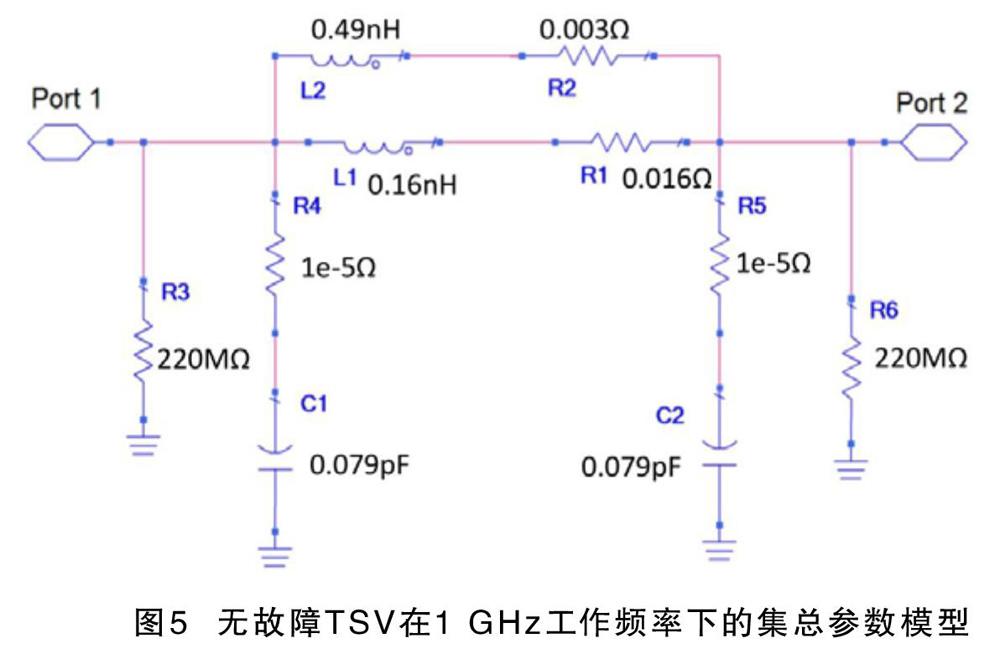

硅体的电阻率选择为1 000 Ω·m。该仿真实现的TSV是一个长50 μm,截面直径为5 μm的铜柱体,该铜柱体外围覆盖了一层厚度是100 nm的二氧化硅层,使 TSV与衬底绝缘。在TSV的顶部和底部施加激励。为了提取实现的TSV的s参数,将求解频率设置为1.00 GHz,扫描频率范围可以设置在1.00 MHz~1.00 GHz之间变化,步长为1.00 MHz。从图2可以看出,电场沿基片内TSV均匀分布。图3和图4分别显示了s11和s21参数的变化,当输入信号为1 GHz时s11的衰减小于0.04 dB。利用HFSS生成了一个关于TSV两端口等效SPICE模型。将该SPICE模型导入ADS环境,创建TSV等效电路模型。

如果选择不同的频率间隔或扫描频率进行仿真,则等效电路中元件的值将发生变化,但等效电路拓扑不受影响。电容表示TSV金属从其端子到介电层表面的电阻。为了提取图6中的TSV,需将衬底接地。图5中的R4和C1,主要是电容性的。TSV与衬底之间距离的变化会影响R4,但不影响起主要作用的C1。

图6中TSV的表面电流密度分布表明,电流均匀分布在TSV导体表面,衬底中没有有效电流。

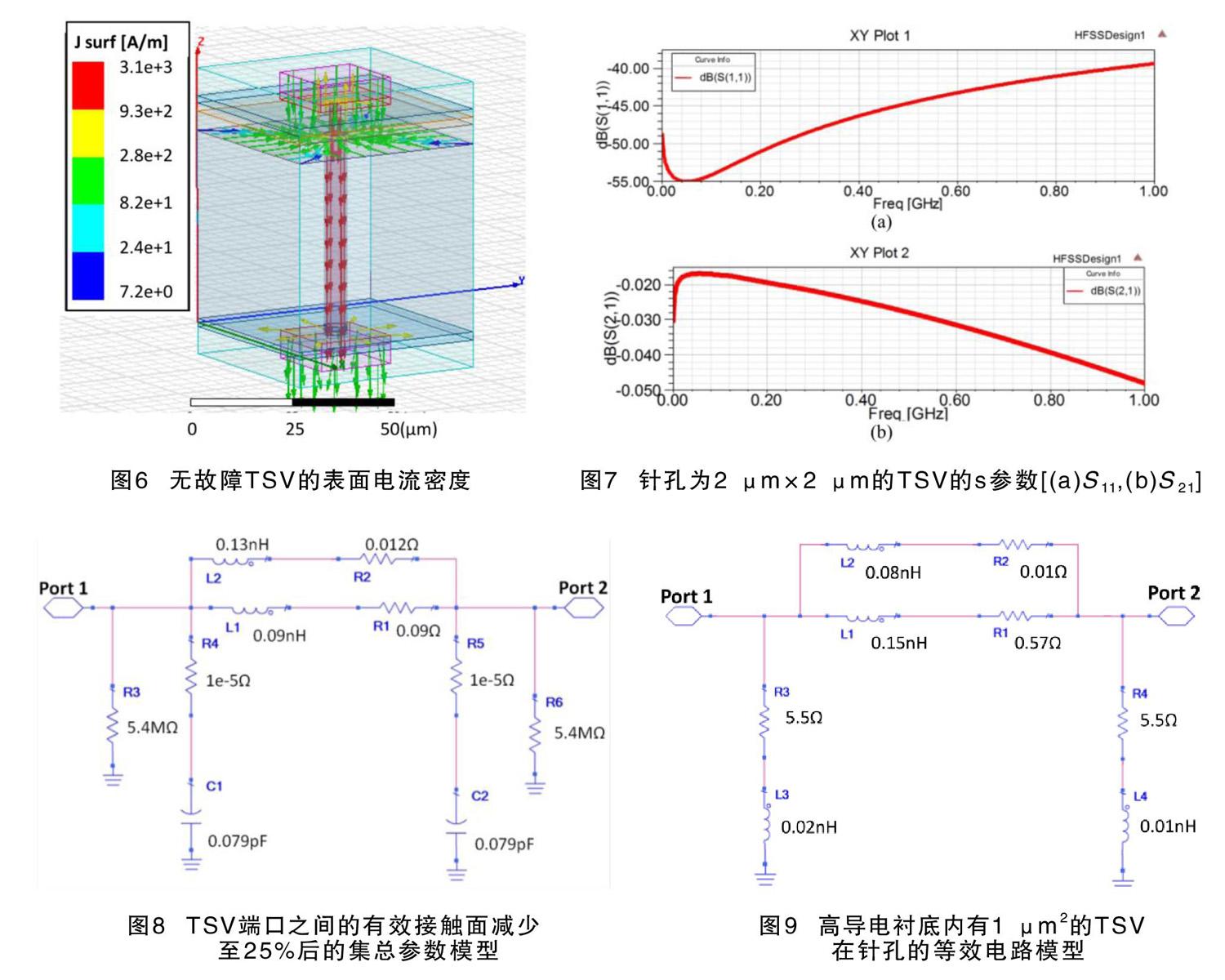

2 针孔TSV模型参数的影响

为研究针孔对TSV的影响,建立了一个尺寸为2 μm×2 μm的针孔,观察其对电场分布和TSV等效电路模型的影响。在与模拟无故障TSV相同的条件下进行了三维模拟。从图7(a)可以看出,衬底在针孔处的体积电流密度急剧增大。提取的电路模型原理图基本保持不变,只是TSV端子与地之间的阻抗R3和R6急剧下降到23 kΩ以下。

TSV表面和周围的衬底之间形成圆柱形电容器。针孔在TSV电容器板之间增加了一个电阻。如果增加的电阻与TSV电容的交流电阻相当,则模型中的TSV电容将会发生变化。对于低电导率的电阻衬底,由于针孔而引起的TSV电容的变化可以忽略不计。事实上,与通过针孔的传导电流相比,TSV与衬底之间的位移电流仍然是主导因素,因此TSV电容在电路模型中几乎保持不变。图7的针孔为2 μm×2 μm的TSV的S参数,与图5的无故障TSV的S参数相比,表明插入损耗和反射损耗都有明显的变化。

TSV端子对地电阻R3和R6,随着针孔尺寸的增大而减小,但二者不是线性关系。例如:当一个针孔的尺寸从1 μm2增加到4 μm2时,R3和R6从55 kΩ下降到23 kΩ,这些结果都是在TSV正中间的一个针孔得到的。通过仿真,确定了不同针孔位置对提取电路模型的影响。结果表明,针孔位置对电路模型的整体影响可以忽略。具有截面为3 μm直径的圆柱形空洞的TSV,从TSV表面向TSV内部延伸3 μm。从1 GHz解频下提取该TSV的电路模型如图8所示,从图中可以看出,其等效电路与图5的电路相同,且参数值几乎相同。空穴的存在对TSV电容和对地电阻均无影响。

TSV的内部不是交流电流的主要通道,因为大多数载流子通过一个TSV表面转移到另一个 TSV终端表面。尽管TSV中存在的空洞是一个可靠性问题,并破坏了其物理完整性,但在高频下,除非空洞足够大,以减少通过TSV的整体交流电流,否则TSV的电气性能不会受到明显影响。

3 衬底对TSV模型参数的影响

衬底电阻率对TSV模型参数有较大影响,如果使用高导电性衬底替代电阻衬底,从TSV端子到地面的电阻大幅下降。高导电衬底模型与电阻衬底模型的相比,R3和R6从220 MΩ大幅降至不足5.40 MΩ。衬底电导率对TSV故障模型的影响是显著的。在电阻衬底内的TSV上有一个4 μm2的针孔,可以将TSV端子对地的电阻从220 MΩ降低到小于23 kΩ。然而,在高导电性衬底TSV上,一个1 μm2的针孔可将端子对地电阻降低到约5.5 Ω,而且还改变了TSV等效电路模型(见图9)。

可以看出,电阻衬底TSV端子与地之间的高电阻R3和R6相应地被高导电衬底中TSV等效电路中的低电阻R3和R4替代,原因为高导电衬底TSV端子通过针孔形成了与地之间的低阻抗路径。电感L3、L4说明TSV端子与地之间的阻抗随频率增加而变大。

4 结语

TSV作为一种新型结构,在测试中面临着独特的挑战,需要新的测试技术来检测TSV参数故障。该文通过三维全波仿真,提取不同条件下的TSV等效电路模型。结果表明:(1)集总RLCG元件实现的无源模型在有限的频率范围内是有效的;(2)确定了针孔结构缺陷对TSV等效模型的影响,衬底电导率对TSV故障的表征有较大的影响;(3)无论衬底类型如何,在1 GHz频率下,即使是较大的针孔也不会明显改变TSV电阻或寄生电容。尽管等效电路模型中TSV对地电阻随针孔的大小变化较大,但不同针孔尺寸下TSV电容的变化幅度太小,无法用于故障检测。

参考文献

[1] Gambino J. BEOL Reliability for More-Than-Moore Devices[C]//2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA).2018:1-7.

[2] 羅心月.三维集成电路TSV阵列热特性研究[D].西安电子科技大学,2019.

[3] 姚瑶.3D存储器的内建自修复技术与TSV容错方法研究[D].合肥工业大学,2019.

[4] Apriyana A A A, Ye L, Seng T C. TSV with Embedded Capacitor for ASIC-HBM Power and Signal Integrity Improvement[C]//2019 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S),2019:1-2.

[5] 谈敏.基于复合激励的TSV故障非接触测试技术研究[D].桂林电子科技大学,2019.

[6] NI Tianming, YAO Yao, CHANG Hao, et al. LCHR-TSV: Novel low cost and highly repairable honeycomb-based TSV redundancy architecture for clustered faults[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2019,39(10):2938-2951.

[7] 方旭.三维集成电路中TSV测试与故障诊断方法研究[D].哈尔滨工业大学,2019.