通用型软、硬件监控平台的设计与开发

姚智文 王小波 付培建

摘要:为了解决通信系统中多个分机一体化的监控问题,设计和开发了基于NiosⅡ和FPGA的通用型软、硬件监控平台。该平台是以Altera公司研发生产的EP3C80系列FPGA芯片和发行的Nios ⅡIDE编译软件进行开发设计的多接口、多协议通用型监控平台。通过开发软件在FPGA硬件上建立嵌入式Nios Ⅱ软核处理器,根据需要添加基于AVALON总线的用户外设,构建网口/串口/ⅡC/SPI等接口,对设备内部多种硬件模块进行控制,使其能够按照正确的指令执行相应的操作,实现对应的各项功能。

关键词:Nios Ⅱ;FPGA;AVALON总线:通用型

中图分类号:TP391.4 文献标志码:A 文章编号:1008-1739(2021)11-60-4

0引言

通信系统由多个分机组成,每个分机形态都是分体式独立设备,除了要求能够通过设备本身的人机交互监控界面完成设备参数的设置、查询和维护功能之外,还能够接受通信系统中集中监控软件的管理控制,实现设各参数的远程监控设置和状态及参数的上报功能。

为有效节省硬件开发及软件编程成本,按照通用化、一体化和标准化的设计原则,设计与开发了一款基于Nios Ⅱ和FPGA的通用型软、硬件监控平台。该平台通过在FPGA硬件上实现基于AVALON总线的IP内核定制,并根据需要添加系统提供的外设,通过用户指令来实现各种应用的需求,最终实现设备相应的监控管理功能。

1系统设计

通用型监控平台设计主要由硬件和软计两部分组成。硬件设计开发使用Altium公司推出的一体化产品专业开发软件Altium Designer,实现原理图的设计、电路仿真、PCB的绘制编辑及拓扑逻辑布线等开发工作。

软件设计与开发利用Altera公司出品发行的Quartus Ⅱ和Nios Ⅱ IDE集成开发环境,根据实际需求,构建专用的32位嵌入式微处理器系统,在FPGA内部创建软核,同时完成存储和接口等电路的完整PLD设计,并利用自动生成适用于系统硬件的专用C/C++运行环境,完成代码指令的编辑、编译、调试和烧录等工作。

1.1硬件设计

监控平台的硬件设计利用Altium Designer软件,实现供电部分电路、FPGA外围电路、时钟电路、Sdram存储、Flash存储、A/D转换和对外接口等电路的原理图设计、仿真及PCB的绘制开发工作,主要电路组成如图1所示。

方案选用型号为EP3C80U48417的FPGA芯片作为主控制器,与供电电路、时钟电路、Sdram存储电路、Flash存储电路、JTAG调试接口电路、温度传感电路、A/D转换电路,以及对外通信LAN口、RS232/422/485串口、ⅡC接口、SPI接口和自定义扩展接口等电路构成整个监控平台的硬件部分。其中供电电路采用Linear公司生产的低噪声正线性稳压器——LT1963系列芯片。该型稳压器内部具有反向电池保护、电流限制、热限制和反向电流保护等保护电路,输出电压范围1.21~20V。采用3片LT1963稳压器,将+5V电源输入分别转换成+33,+2.5,+1.2V三路不同的电压,为其他电路提供稳定输出。

时钟电路主要采用型号为SCX011B-E20MCB的国产20 MHz低相位噪声晶体振荡器,搭配2个电容(容值分别为1000 pF和0.1μF)和一个330Q电阻,为主控单元FPGA芯片产生准确、可靠的时钟信号。

Sdram存储电路芯片选用Hynix公司出品的HY57V561620FTP同步动态随棚存储器,时钟速率选用133MHz(通过锁相环将20 MHz时钟源倍频所得)。该芯片具有空间存储量大、读写速度快、价格相对便宜等优点。

Flash存储电路由数据存储和程序存储2个部分组成。其中数据存储选用SPANSION公司出品的大容量、高性价比、支持16位数据传输的S29GL256P11FF102芯片作为内存Flash存储器。程序存储芯片选用Altera公司出品的64 Mbit EPCS64S116N芯片作为FPGA的配置存储器,用于存储编译后的程序。

A/D转换电路选用AD公司出品的16位高精度、低功耗、超小型QVN封装的可编程模数转换器ADS1115芯片,用于对外部模拟信号进行采集和转换。温度传感电路选用Maxim公司出品的DS18820Z作为温度采集芯片,该芯片具有体积小、功耗低、抗干扰强和精度高等特点。

对外通信接口电路包括LAN口(芯片选用WIZnet公司出品的高性能以太网接口芯片W5300)、串口(分别选用Maxim公司出品的高性能MAX3232、MAX3485和MAX3490等收发器)、串行总线ⅡC接口、全双工高速同步SPI接口和自定义扩展接口,实现与各种外设进行通信。其中自定义扩展接口在已有接口不满足使用需求的情况下,可通过增加各种IP核的方式进行扩展,体现监控平台的通用性和可扩展性。对外通信接口電路原理图如图2所示。

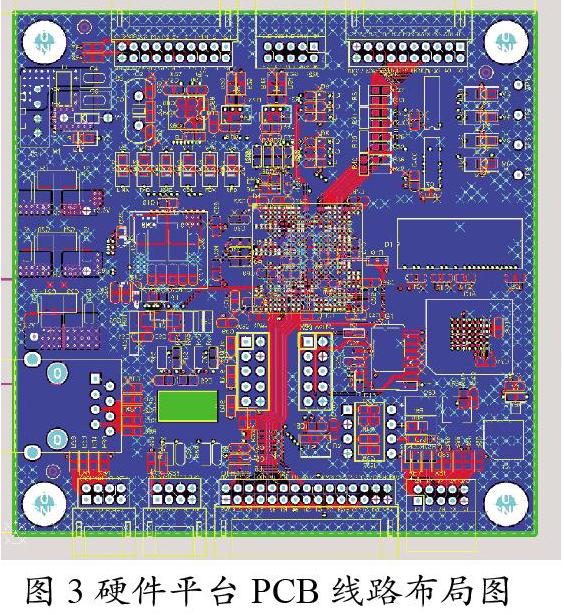

利用Altium Designer软件将各部分电路原理图设计完成后,对PCB线路布局进行绘制,如图3所示。

硬件平台的实际尺寸仅为900mm×900mm,由于布局非常紧凑,为了增加布线面积,通过定位系统及绝缘粘结材料交替互连的方法,硬件平台的PCB采用8层线路进行布线。

平台四角距离PCB板4.7mm处,分别留有孔径为3.5mm的接地过孔,可通过3mm螺钉固定于其他结构件上。平台四周分别有序布局供电输入、AD检测输入、通用10、串口、网口、指示灯、按键及显示屏等信号电器连接点位,可通过焊接在PCB上的相应连接器与外接信号连接,实现供电或指令通信。

1.2软件设计

监控平台的软件设计首先利用Quartos Ⅱ软件完成FPGA内部硬件时钟、各部分功能块的可编程逻辑设计。通过原理图输入和硬件描述语言输入的方式,建立与监控平台硬件部分相适应的软件工程,并根据监控平台的硬件配置进行软件系统设置和完成所有硬件电路的可编程逻辑设计,顺利通过编译,最终生成对应的输出文件,为软件代码开发提供良好基础。

Nios Ⅱ嵌入式软件设计包集成了一系列尖端的软件工具、实用工具、库文件以及驱动程序,这些工具及程序可以帮助软件开发人员根据实际需求快速构建软件系统框架,大大提升软件设计的开发效率。

方案利用Nios Ⅱ嵌入式软件设计包中基于Eclipse IDE架构的全集成开发环境Nios Ⅱ IDE,通过GNU开源编译环境,对监控软件系统架构、硬件驱动程序、对外接口及控制协议等进行设计与开发。其中对外接口及控制协议部分主要包括TCP-IP协议网口、基于RS232/422/485等3种电平的异步串口、ⅡC通信总线接口、串行外设总线SPI接口和自定义扩展接口及相关协议的程序开发。同时利用基于GDU的调试工具,对软件进行仿真和调试,并通过JTAG调试接口和目标设备的硬件相连,对具体设备上的硬件模块进行实际联调和联试,最终顺利实现嵌入式监控软件的各项功能。软件集成开发环境如图4所示。

最终开发完的嵌入式监控软件功能图如图5所示。

嵌入式监控软件有3个主要功能,分别是设置、查询和维护子功能。设置、查询和维护这3个子功能集合又可分解为响应的下一级子功能。例如站号设置子功能、告警查询子功能及网口参数维护子功能等。

按照通用化、一体化和标准化的设计原则,系统中各分体式独立设备前面板统一采用19264分辨率的点阵图形液晶显示器。用于提供友好的人机界面,接受用户指令,完成工作参数设置、查询和维护等操作。

2工程应用

嵌入式通用监控平台在设计之初,对各分机的应用需求进行了充分的调研和评估,最终对嵌入式监控平台进行了合理的通用化、标准化和一体化设计。利用Altium Designer软件、Quartus Ⅱ软件和Nios Ⅱ IDE集成开发环境对平台的软、硬件进行设计与开发,并通过在FPGA内部灵活构建基于Nios的SOPC系统和完整的可编程逻辑设计,搭建高效的软件框架,同时编写通用底层驱动程序,实现各种接口的应用开发和调试,大大减少调试工作量,缩短项目研制周期,同时提高了程序整体运行效率。经过与各分机进行充分联试及验证,最终该通用型监控平台在各分机使用良好,性能稳定可靠。

嵌入式通用监控平台不仅满足系统内不同分机一体化和通用性要求,而且大大节省研发成本及调试时间,缩短了项目周期。并且,嵌入式通用监控平台在各分机上顺利通过高低温、湿热和电磁兼容等试验,各项软、硬件功能及指标性能均符合要求,经得住实际运行的考验。

嵌入式监控平台实现了不同分机、不同需求的通用化、一体化及标准化的使用要求,并在多个项目中得到了推广和成功應用,监控平台的成功经验为类似项目中个性化监控平台设计提供了借鉴意义。

3结束语

通用型监控软、硬件平台基于Nios Ⅱ和FPGA进行开发与设计,综合考虑不同分机的实际使用需求,填补了公司通用型嵌入式监控软、硬件平台的空白,降低了研发成本和节省软、硬件的调试时间,大大缩短了项目周期,降低了研制成本。

本监控平台硬件易于安装,软件操作简便,可定制,通过该平台能够快速设置和查询设备的参数和状态信息,为公司其他项目提供了一套稳定、可靠的嵌入式通用监控平台,满足不同分机的通用需求。