阐述基于FPGA的高精度频率计的设计与实现

易显刚 黄虎城

摘要:随着电子技术的发展,频率计的应用越来越广泛,本文设计了一种基于FPGA的高精度频率计,该频率计以FPGA和单片机为核心,能够高精度的对信号频率进行测量,在测量范围、精度和稳定性方面都有优异的性能。

关键词:数字频率计;计数法;高精度

1 系统的整体设计

本文设计的高精度频率计硬件部分主要包括宽带通道放大器、高速比较器、单片机以及FPGA等几部分组成。系统的运行原理如下:单路正弦信号经过宽带通道放大器,由放大器进行放大,最大可以得到26dB的电压增益;在放大以后信号进入高度比较器,由其整形成方波信号,并且输入到FPGA,由FPGA将方波信号进行分频,然后计数,最终将结果发送给单片机;单片机在得到技术结果以后,会选择精度最高的结果,并根据其计算出频率、时间间隔和占空比等信息,并由液晶显示屏将结果显示出来。同时,单片机还能够对FPGA进行控制。为了提高信号传输的稳定性,在不同硬件模块之间,通过“双绞线”来进行信号传输。

2 系统的硬件设计

2.1 供电模块设计

本文设计的高精度频率的电源选择±5V的双电源;应用了AMS1117-3.3来获得3.3V的电压,这样可以保证电压稳定保持在3.3V,不受负载影响;接口芯片、FPGA和单片机的供电由FFC线、杜邦线和通用串行总线接口来完成。

2.2 宽带通道放大器

本系统采用OPA847作为宽带通道放大器,该芯片是一种宽带、极低噪声电压反馈运算放大器,具有较高的稳定性。其带宽可以达到3.9GHz;压摆率达到950V/μS;输入噪声0.85nV/√Hz。

2.3 高速比较器

本系统采用TLV3501芯片作为高速比较器,这是一种轨至轨高速比较器,轨至轨时间为4.5ns,比较速度非常快,能够比较的信号频率范围也比较大,可以达到100MHz。

在本系统中,采用了SOIC封装方式来进行OPA847和TLV3501的封装,并且应用了同样的引脚排列方式,通过这样的设计,能够使印刷电路板可以同时供这两块芯片兼容使用。印刷电路板中的信号传输线设计的尽可能的短,并且采用平面铜对底线进行了覆盖,采用了共点接地的方式。

2.4 FPGA

本系统中采用了Cyclone-EP4CE6E22C8N芯片,这种芯片的优点,其稳定工作晶振频率可以达到50MHz,可稳定倍频至100MHz,能够实现数据的并行处理。此外,该芯片的成本和功耗都比较低,因此应用这一芯片能够对系统的成本和功耗进行有效控制,提高设计的高精度频率计的应用范围。

2.5 放大器的稳定性设计

在本系统中,放大器是重要的组成部分,为了保证系统的功能,放大器需要达到绝对的稳定,因此其不仅要避免接近自激振荡条件,而且还留有一定的富裕量。对于放大器而言,其富裕量越大,其越南产生自激振荡。本系统中选择的放大器为OPA847,因此在选择放大电路参数时,应最大程度上距离其自激振荡条件远一些。

在系统运行过程中,不良接地、不充分的供电电源滤、输入杂散电容、高频噪声、前沿校正以及大容量容性负载都可能会影响到放大器的稳定性。因此本系统在设计过程中采用了针对性的设计,降低这些因素的影响。本频率计采用了整个系统完全共地的接地方式,通过电源旁路电容使电路的稳定性得到了显著的提升,电源和地之间采用了10μF的电容,并且并联了一个0.1μF的陶瓷电容;为了降低负载电容的影响,还在输出端增加了一个串联电路;选择的放大器本身具有极低噪声。选择了26dB的通带增益,也有利于其保持最佳稳定状态。

3 软件设计

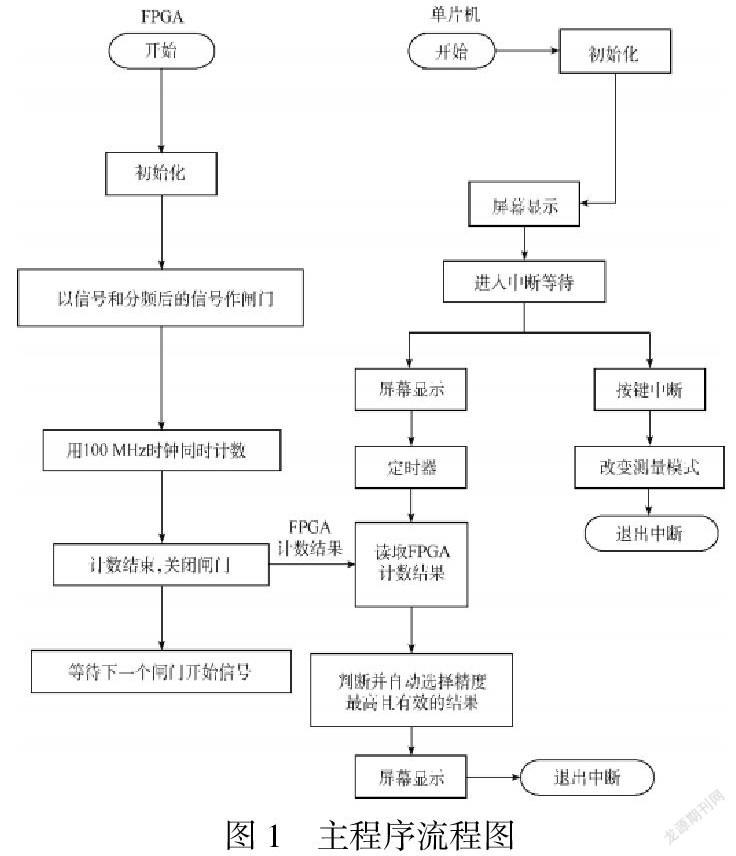

在控制程序的而设计方面,本文以MSP430F5529作为控制核心,由其来进行FPGA和显示等的控制;Cyclone-EP4CE6E22C8N为信号处理核心,进行方波信号分频和技术等工作。本系统应用了“多路并行计数法”,主程序流程图如图1中所示:

4 性能测试

4.1 频率和周期测量功能

通过向数字频率计输入有效值和频率不同的正弦波来对数字频率计的频率和周期测量功能进行测试发现,该频率计能够实现对1Hz~199MHz、10mVrms~1Vrms的正弦波能进行频率测量,相对误差在0.0001%,具有优异的性能。

4.2 时间间隔测量功能

通过向数字频率计输入两路同频同压有时间间隔的方波信号对时间间隔测量功能进行测试,结果显示其能够对100Hz~1MHz、50mV~1V的同频方波进行时间间隔测量。测量的范围可以达到1μs~100ms,相对误差在1%以内。

结论

本文以FPGA和单片机为核心设计了一个高精度频率计,通过测试发现,该频率计具有良好的频率和周期、时间间隔等的测量功能,在测量范围、精度和稳定性方面都有优异的性能。

參考文献

[1]王永良, 宋政湘. 基于FPGA的同步测周期高精度数字频率计的设计[J]. 电子设计应用, 2004(12):4.

[2]董勃, 王直, 于航,等. 基于FPGA的高精度频率计[J]. 计算机与现代化, 2021(6):5.

[3]宋思明, 陈铁军, 李垣燊,等. 基于FPGA的高精度数字频率计[J]. 信息通信, 2019(6):3.