基于FPGA的高精度频率计

董 勃,王 直,于 航,刘 博

(1.江苏科技大学计算机学院,江苏 镇江 212100; 2.江苏科技大学电子信息学院,江苏 镇江 212100)

0 引 言

伴随着计算机技术的发展,各行各业对传统数据采集系统的精度、实时性、带宽等性能提出了更高的要求[1-3]。频率检测仪器作为数据采集系统的一个重要分支,对于研究人员进行科学研究和电子工程师开发新产品起着至关重要的作用。然而传统的频率计通常采用分立元件设计,具有稳定性差、体积大、功耗高和不便携带等缺陷[4-6]。因此,一款具有高稳定性、高精度、高带宽、低功耗等特点的便携式频率计会有更大的应用市场。

现场可编程门阵列(Field Programmable Gate Array, FPGA)具有硬件电路软件化的特点,即能通过程序控制芯片内部产生特定的硬件电路,实现对所有信号和模块并行处理。而传统使用ARM(Advanced RISC Machines)芯片的频率计,不能对信号实现真正的并行处理。因此要想实现器件的多通道或高速运行,势必要增加芯片数量,否则频率计的实时性和精确性会大打折扣,但增加芯片数量又会增加功耗、价格并使得仪器体积增大。而FPGA所具有的特点使得在不增大仪器体积、功耗和成本的情况下,较容易实现所属器件的多通道和高速运行[7]。

频率信号的测量通常使用周期测频法或脉冲计数法[8-10]。周期测频法即使用定时器测量一个脉冲的周期T,用公式F=1/T计算频率,据此易得该方法检测频率的相对误差随着被测信号周期的增大而降低,故此方法适合于测量低频信号[11-12]。脉冲计数法即在闸门时间t内对被测信号进行计数n,最后利用公式F=n/t,即可得到待测频率值,该方法检测频率的相对误差随着被测信号频率的增大而降低,故此方法适合于测量高频信号[13-14]。

针对这2种频率检测方法的优势和不足,本文利用FPGA将待测信号以1 kHz频率为界限分割为低频和高频这2种信号,并利用最优的检测方法对待测信号进行检测。

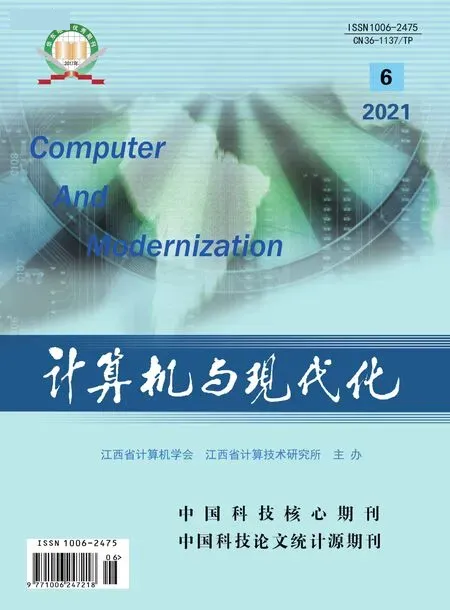

1 频率计总体结构

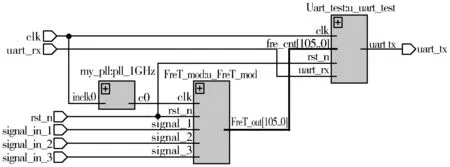

频率计的逻辑方案设计如图1所示,该频率计由外围的电压跟随器电路、串口通信电路以及FPGA上的分频器模块、频率计量模块和串口通信模块等组成。其基本工作流程为待测信号经过电压跟随模块的稳压,稳压后的信号经过分频器的识别后进入对应频率计量模块单元,最后通过串口将频率数据实时上传至上位机进行信号分析。

图1 频率计逻辑方案设计框图

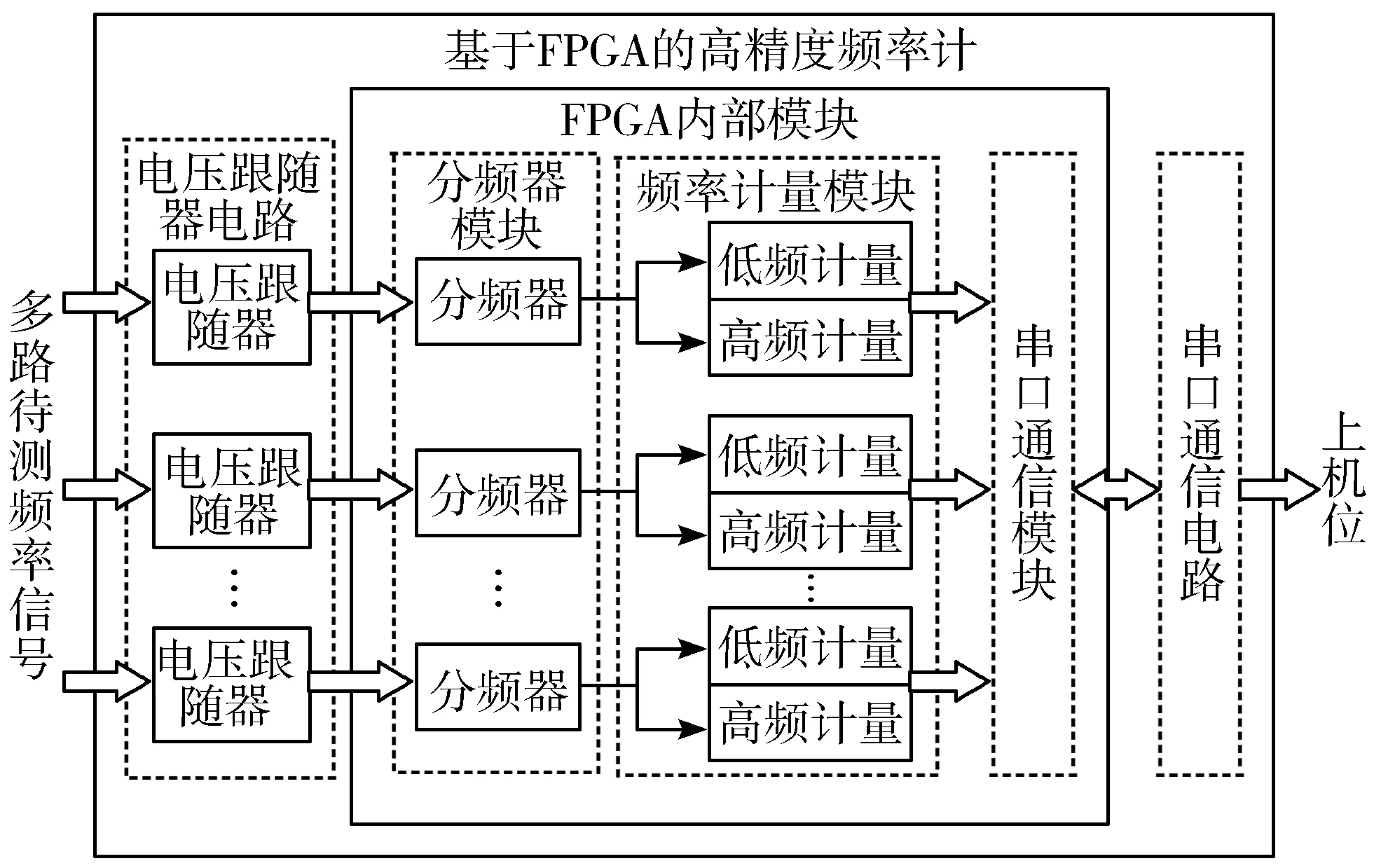

1.1 频率计硬件电路的选择与设计

待测频率信号较高时,信号本身的波动可能造成较大的检测误差;或检测器件可能引起待测信号衰减从而影响检测精度,故利用电压跟随器来起到隔离信号衰减和稳压的作用[15-16]。选取LT1490AHS8运算放大器作为电压跟随器模块的核心部件。该芯片具有低功耗、高带宽和双运放的特点。电压跟随器的原理图如图2所示。

图2 电压跟随器原理图

FPGA模块使用Altera公司生产的Cyclone Ⅳ作为仪器的控制核心。该型号的FPGA芯片拥有丰富的可配置逻辑块、可配置的IO口和强大的并行运算能力。该型号FPGA芯片工艺比较成熟,在频率信号处理上也具有很高的响应速度,且具有较强的灵活性、成本低、功耗低、稳定性高和体积小等优势[17-18]。

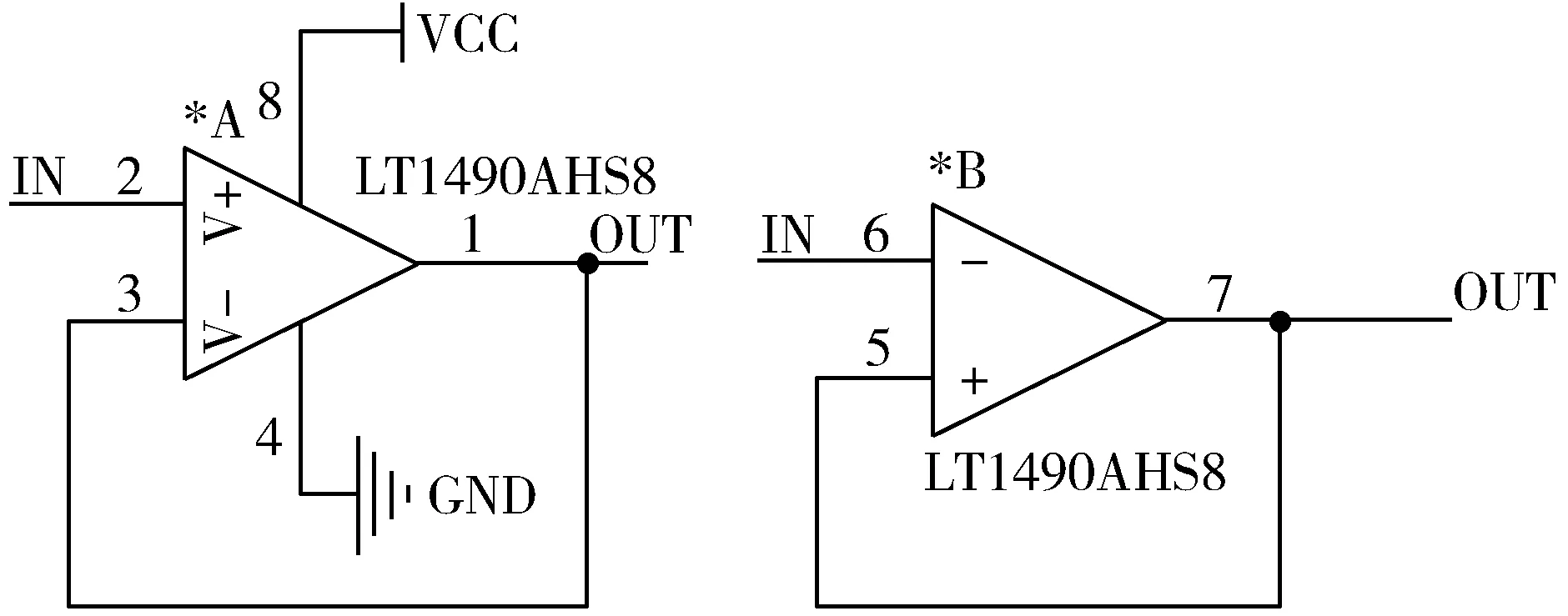

串口通信电路用来实时传输频率数据至上位机,该电路主要由CH340G及其外围的电阻、电容元件组成。由于CH340G芯片具有较高的性价比和可靠性,因而被广泛使用在各类通信和信号交换设备中[19-20]。串口通信电路的原理如图3所示。

图3 串口通信电路原理图

1.2 频率计软件设计

本文利用Quartus Ⅱ软件完成FPGA上各个模块的设计。FPGA设计流程包括设计输入、综合、功能仿真(前仿真)、实现、时序仿真(后仿真)、配置下载等6个步骤,其中综合这一步作为FPGA设计的中间环节,对整个设计电路的性能起着至关重要的作用,尤其是逻辑传输级(Register Transfer Level, RTL),综合在决定RAM资源的有效利用方面起关键作用[21-23]。利用Quartus软件的RTL图可以很方便地查看各个模块及其连通关系,还可以看到每个模块占用FPGA资源的大小,便于合理分配FPGA资源。FPGA的RTL如图4所示。

图4 FPGA的RTL图

图4中my_pll为锁相环,用来将系统时钟倍频到1 GHz,倍频后的频率作为频率测量模块的基本时钟。图4中Frequency_meters为频率测量模块,从图4中可以看出该频率计有3个频率检测通道。检测的频率数据通过FPGA的Uart_test串口模块控制硬件电路实时传送给上位机进行信号分析。

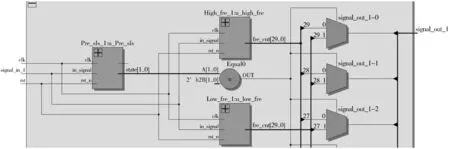

图5为检测通道1中的RTL图,每个检测通道都包含一个分频器模块和2个频率测量模块。分频器的分频采用在1 ms内检测待测信号振荡数的策略,若震荡数小于或等于100,则该待测信号被判定为低频信号,否则该待测信号被判定为高频信号。频率测量模块又分为低频测量模块和高频测量模块,其中低频测量模块采用周期测频法,即检测待测信号的周期,周期的倒数便为待测信号的频率;高频模块采用脉冲计数法,即在闸门时间内对被检测的待测信号计数,计数值除以闸门时间便为待测信号的频率。

图5 检测通道1的RTL图

通过分析FPGA上的资源占用情况,发现3个检测通道和串口通信模块一共占用了芯片逻辑器件总数的6%,说明该芯片至少可以同时容纳20个检测通道。并且由于FPGA方便移植的特点,使得通道的拓展也较为容易。

2 频率计功能和精度测试

为了检验频率计的功能和设计目标,分别做了低频信号多通道检测实验、高频信号多通道检测实验、从低频步进到高频的连续频率检测实验和频率计的最高带宽检测实验。

2.1 低频信号与高频测试

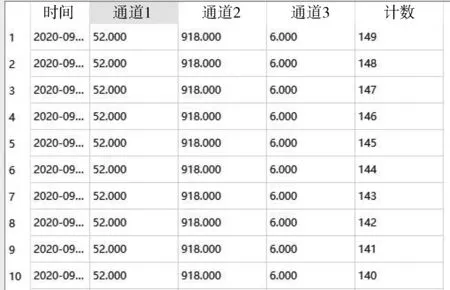

低频信号多通道检测实验的实验步骤:首先利用FPGA分别产生52 Hz、918 Hz和6 Hz这3个不同的低频信号,然后分别利用3个通道对测试信号进行检测。最后通过串口将检测到的频率数据上传至上位机进行数据分析。图6所示为上位机检测的低频信号。

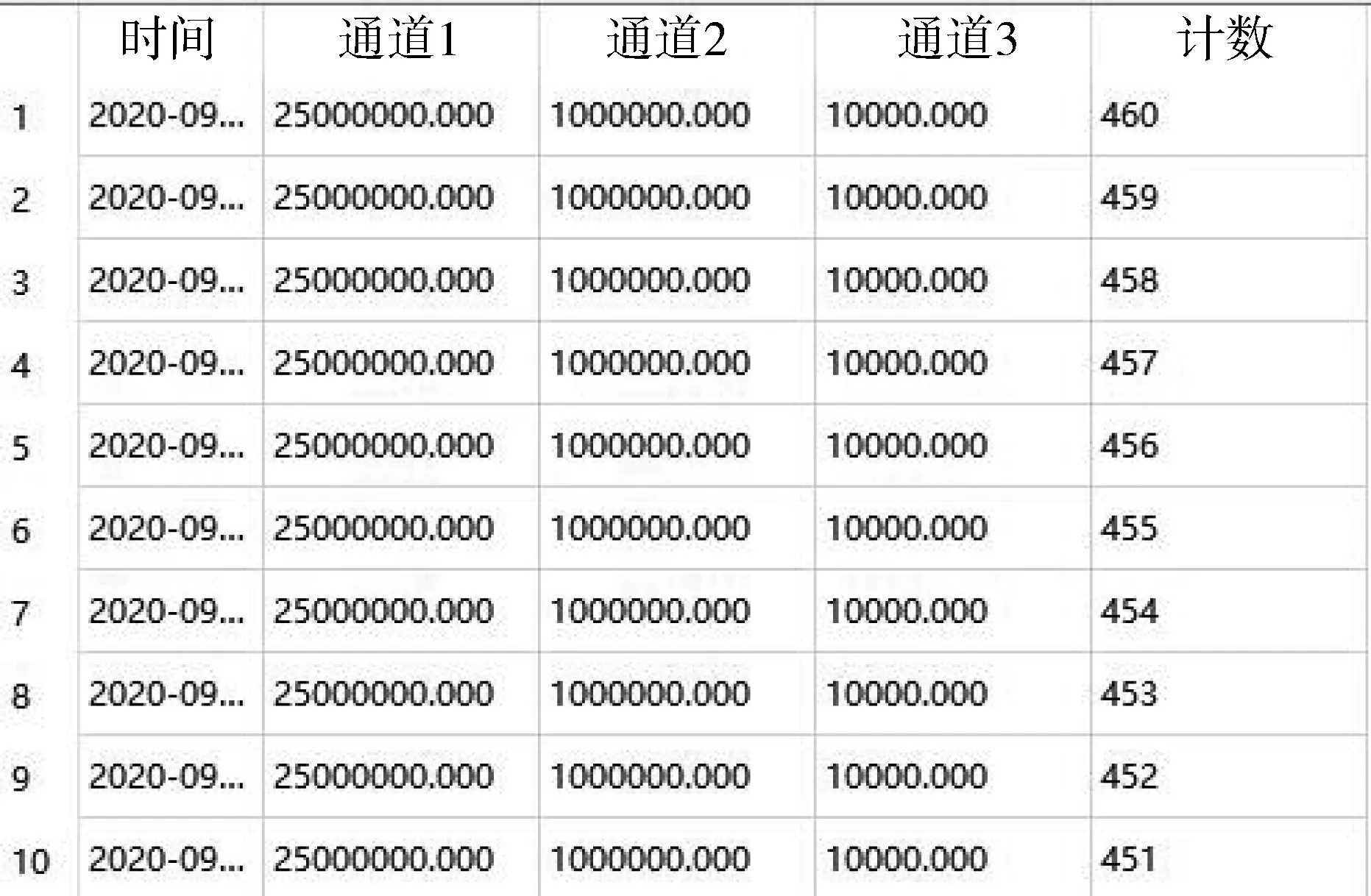

高频信号多通道检测实验的实验步骤:首先利用FPGA分别产生25 MHz、10 MHz和10 kHz这3个不同的高频信号,然后分别利用3个通道对测试信号进行检测。最后通过串口将检测到的频率数据上传至上位机进行数据分析。图7所示为上位机检测的高频信号。

通过观察图6和图7的数据后可以发现,频率计实际检测到高频和低频数据都与测试频率相同,说明了本文设计的频率计在低速和高速频率检测上具有较高的稳定性、精确度。同时还可以发现,频率计的3个检测通道在同时工作的情况下能做到互不影响。

图6 上位机检测到的低频测试信号

图7 上位机检测到的高频测试信号

2.2 连续信号测试

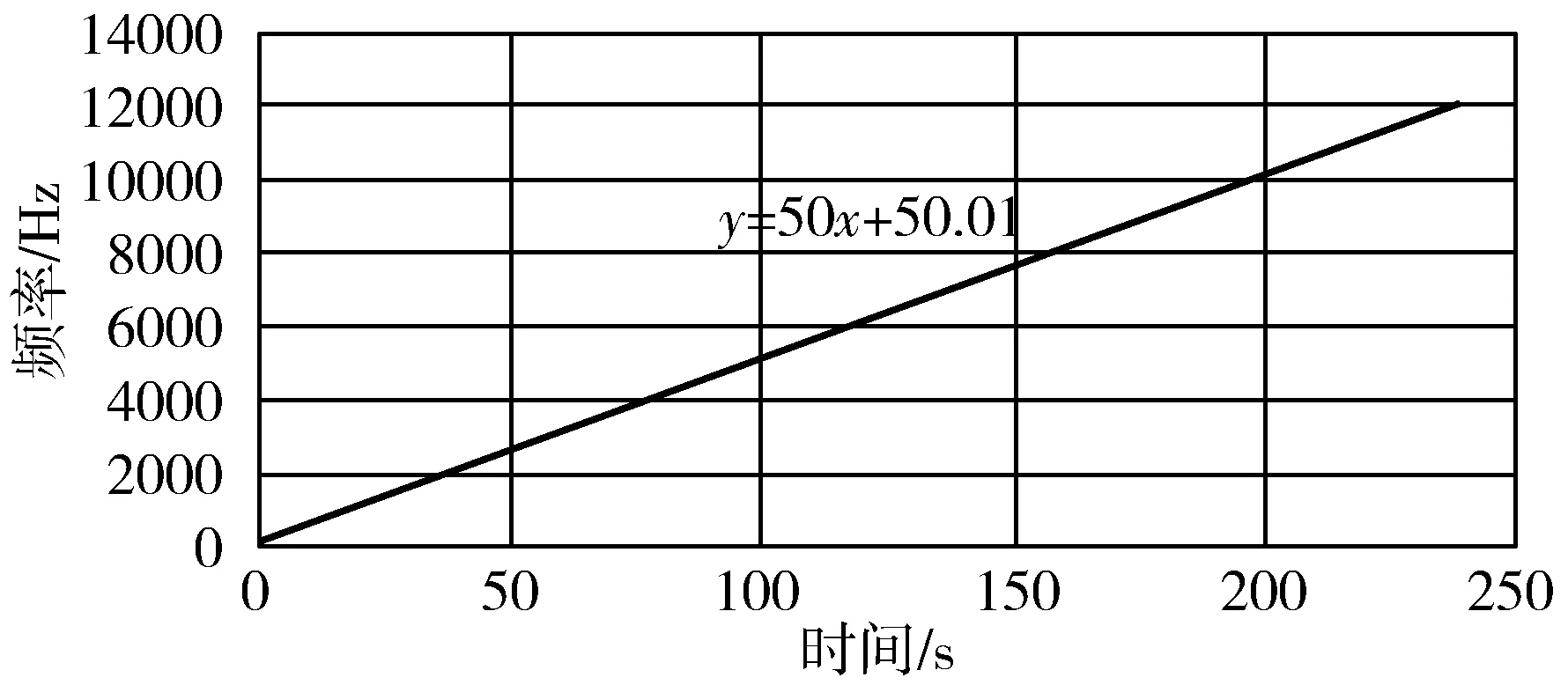

实验的步骤:首先利用FPGA产生100 Hz的频率,之后以每秒递增50 Hz的速率产生线性的频率信号。并将检测的频率数据导出,利用Excel的曲线拟合功能对检测频率进行曲线拟合。图8为频率计检测的频率信号曲线图。

图8 频率检测曲线图

从频率检测曲线图可以看出,频率计检测到的频率和时间组成的曲线具有很好的线性特点,图中的拟合公式y=50x+50.01正好验证了这一点。这个测试验证了频率计在检测连续变化的频率信号时也具有相当高的稳定性和精度。

2.3 频率计带宽测试

奈奎斯特采样定理说明了采样频率与待测信号频谱之间的关系,是连续模拟信号离散化的基本依据。它为采样率建立了一个足够的条件,该采样率允许离散采样序列从有限带宽的连续时间信号中捕获所有信息[24-25]。核心为采样率必须大于被测信号最高频率分量的2倍。

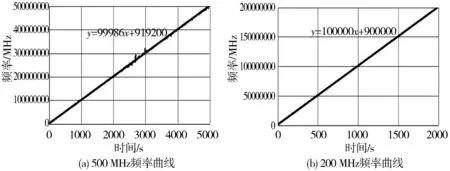

频率计使用经锁相环倍频为1 GHz的频率作为时钟信号,理论上最高检测带宽会达到500 MHz。由仪器产生1 MHz频率,并以此为开始以每秒100 kHz的速度步进到500 MHz,最后导出数据,用Excel拟合曲线并分析。

图9为最高检测频率为500 MHz和最高检测频率为200 MHz的频率曲线对比图。

图9 2种最高检测频率对比图

从图9中可以看出,最高检测频率为500 MHz的曲线从200 MHz后开始变得不规则,表明频率计在200 MHz之后有较多错误的检测数据;而最高检测频率为200 MHz的曲线则非常地规整。同时图9中2种曲线的拟合函数分别为y=99986x+919200和y=100000x+900000,其中最高频率为200 MHz的曲线与测试频率变化规律完全相同。

表明本文设计的频率计对0~200 MHz范围内的频率有很好的检测效果,而对200 MHz之后的待测信号可能产生较大的误差。

3 结束语

本文针对传统频率计的各种劣势做了针对性的改进和设计,实现了一款具有实用性和高性价比的高精度高带宽频率计。主要贡献如下:1)利用电压跟随器避免了检测仪器对待测信号造成的衰减,获取了比较稳定的待测信号;2)利用FPGA的灵活性和并行性,设计了多个检测通道,同时还提高了频率检测的稳定性和精度;3)可以通过串口实时地将信号上传给上位机,使得使用者可以利用电脑上的各种软件进行数据处理和分析。