基于FT2000中LBC外接存储器驱动程序设计

张鹏

(汉中职业技术学院汽车与机电工程学院,陕西汉中,723002)

1 LBC模块及开发环境介绍

LBC(Local Bus Controller)即局部总线控制器,其主要负责对外部存贮器的访问,该控制器提供了到多种类型存贮设备的接口,同时该控制器负责控制八个存贮体(bank),并由二个UPM机和一个GPCM机所共享,负责与Flash和nvRAM的通讯。

本设计的基本开发环境,即采用FT2000处理器Local Bus接口的八个存贮体不同片选模式,来访问外接存储器Flash和nvSRAM设备,以此实现对数据的各项读写擦等操作。FT2000芯片是一款集成了4个新一代高性能处理器内核FTC663的CPU,它采用乱序四发射超标量流水线,兼容64位ARMV8指令集并支持ARM64和ARM32两种执行模式,支持单精度、双精度浮点运算指令和ASIMD处理指令,支持硬件虚拟化。同时,该芯片适用于构建有更高性能、能耗比和安全需要的桌面终端、轻量级服务器和嵌入式低功耗产品。

2 外接存储器介绍及配置相关操作

本设计中外接外接Flash(Am29LV256M)和nvSRAM(STK14CA8)存储设备。

■2.1 Flash基本概述和操作

设计中应用 AM29LV256M(16M*16-Bit/32M*8Bit)芯片作为通用扇区Flash存储器,该款芯片具有高性能,低功耗,单电压支持读、擦、写等优点,同时,可通过BYTE引脚置位来选择支持16bit/8bit宽度的数据总线。

在LBC模块操作的初始化中,Flash支持GPCM(通用片选机)和UPM(可选寄存器)两种不同的控制机模式访问数据,并且,当寄存器BRn[7:5]配置为000时,即是GPCM模式,寄存器BRn[7:5]配置为100/101时,即是UPM模式。其中,GPCM模式为简单、性能较低的存贮器和内存映射设备提供使用接口,其不支持突发传输。在Flash的操作中,还需要对两个基本的寄存器组BRn和ORn配置,用来定义Flash的基地址和其地址屏蔽位。

而UPM模式可以用来产生较为灵活且用户定义控制信号的定时操作,该模式还可以通过软件启动定义读、写、突发读或突发写期间的外部控制信号。同时,在设计Flash操作中用UPM的核心内部RAM阵列,并通过这个阵列确定给定时钟周期在外部存贮器控制信号(字节选和片选)上驱动的信号线。

■2.2 nvSRAM概述及操作

设计中应用STK14CA8(128k*8)非易失性RAM存贮器作为另一存储设备,该芯片具有较高的存贮性能和快速的访问时间,同时可无限次进行Read、Write、Recall等操作。

类似外接设备Flash的操作,在LBC模块操作的初始化中,nvSRAM也支持GPCM(通用片选机)和UPM(可选寄存器)两种不同的控制机模式访问数据,且配置寄存器BRn[7:5]的模式也是相同。

其中,在GPCM模式下,首先必须对两个32位寄存器组基寄存器(BRn)和可选寄存器(ORn)进行配置,其中基寄存器(BRn)用于定义SRAM基地址和其地址屏蔽位AM,而最低的0bit位(V)即为BRn和ORn内容的有效位置位。而在UPM模式下,同样用到UPM的核心内部RAM阵列,在对RAM阵列中,每一个RAM阵列都包含64个32位字,根据每一个字提供的比特位访问外部SRAM总线时钟周期。

3 LBC模块的基本配置操作

本设计在LBC操作中,必须先对局部总线配置寄存器(LBCR)做出了相应配置,保证LBC处于空闲无数据传输状态,然后对LBCR寄存器操作,当LBCR[BUSY_MM]置1时LBC位空闲状态。

对于LBC初始化状态,由于接口层传入了不同外设的配置参数,故在初始化状态中需要做出,对传入不同片选和工作模式的设置、BRn寄存器和ORn寄存器各Bit位的配置、时钟分频和端口的配置等。对于不同的片选和工作模式,就是对外部的Flash和Sram分别选择八个存贮体bank当中的某两个进行的操作,接口层传入的参数也需要完成GPCM和UPM工作模式进行配置,并根据Flash和Sram中需要不同功能,配置寄存器BRn和寄存器ORn。

设计中的时钟分频,即LBC的系统时钟和外部设备总线时钟(LCLK[2:0])之间2、4、8的比率配置,该比率主要通过对时钟比率寄存器LCRR[CLKDIV]进行软件设置的。在考虑时钟分频后,需要结合外部地址延时周期寄存器LCRR[EADC]进行配置不同的循环延时周期数,用以满足访问外部设备数据/地址/片选/读写等不同信号线的保持时间。

在底层LBC的操作中,外部设备Flash和nvSram通过访问LBC模块进行正常的读写擦等操作,其中,设计需要LBC模块对不同外接设备端口大小进行读写,即进行LBC字节/字/双字读和写的函数操作。

4 LBC驱动存储器程序设计

■4.1 整体结构设计

(1)硬件总体结构

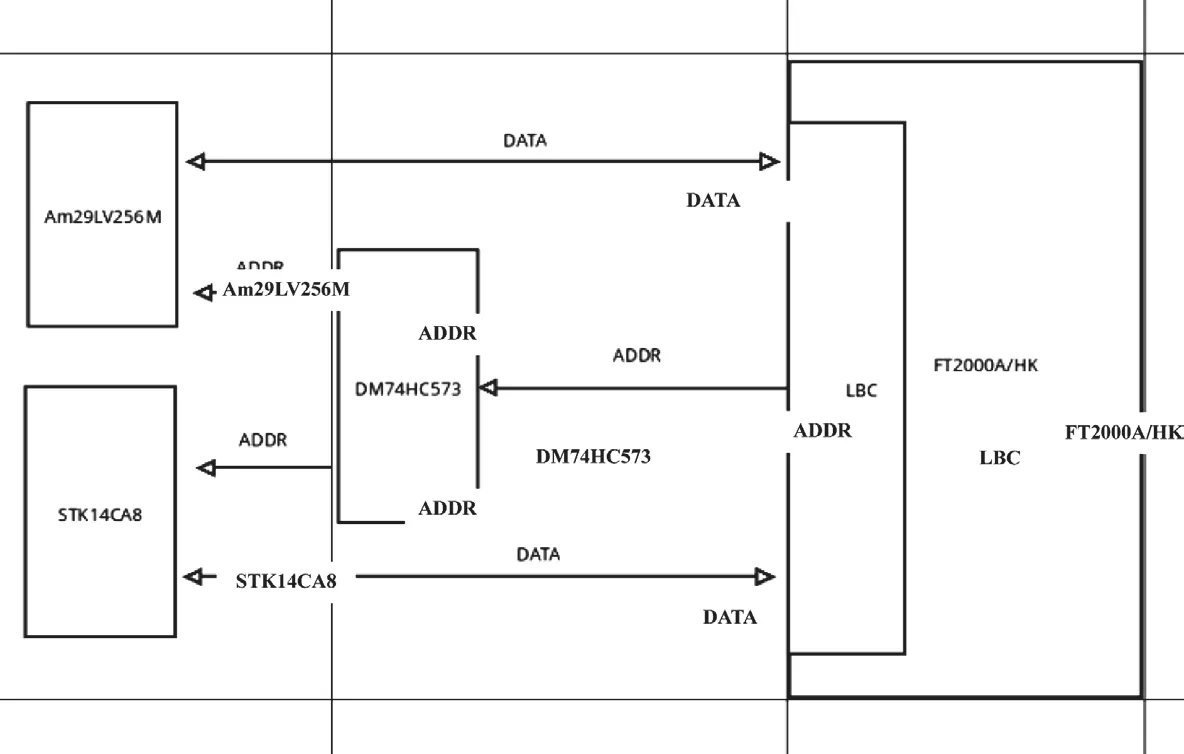

本设计LBC模块外接存储器件Flash(Am29LV256M)和nvSRAM(STK14CA8)的硬件连接方式如图1所示。在硬件连接中,首先将FT2000主控中LBC模块引出连接DM74HC573八路输出锁存器芯片,当LBC模块与Flash(Am29LV256M)和nvSRAM(STK14CA8)进行数据交换时,通过DM74HC573片选其中两路访问控制向Flash和nvSram写入指定地址,在存储器设备接收到主控发过来的地址数据时,直接向LBC模块反馈回读写擦相关数据。

图1 硬件总体结构

(2)软件设计框架

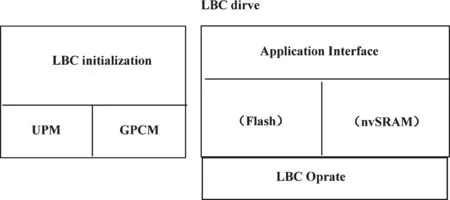

本设计软件部分总体分为三部分:LBC Initialization、LBC Oprate、Application Interface,如图2所示。

图2 软件设计框架

LBC Initialization:主要对LBC进行初始化配置,设置基地址偏移、片选有效、端口大小、选择UPM或GPCM控制机工作模式、设置操作时钟等配置。

LBC Oprate:主要实现对LBC总线的不同字节、字、双字的读写等操作。

Application Interface:主要是对外接Flash进行Read、Program、Erase等操作及Flash工作模式配置,对外接nvSRAM进行Read、Write、Store等操作。

■4.2 驱动程序设计流程

本设计基于上文硬件结构及软件设计框架,按照如下流程进行LBC驱动程序设计。

首先,对LBC模块进行初始化,其中包括LBC模块自由等待的相关配置操作,存储器的基本配置,LBC中基地址、片选、时钟分频的基本操作。

其次,完成LBC模式选择,当配置成GPCM模式时,直接进入Flash和nvSram存储器选择阶段,同时进行LBC模块端口bit位设置。当配置成UPM模式时,再次进行UPMA/UPMB操作,开始RAM 信号读写,Burst信号读写等操作,当UPM模式结束后,进入Flash和nvSram存储器选择阶段,同时进行LBC模块端口位设置。

然后,继续进行LCB模块数据交换操作,即分别对底层LBC中数据Byte、Word读写,Burst读写等操作。

最后,完成Flash和nvSram存储器的配置操作。

5 驱动程序仿真

在本设计中,通过Vivado仿真环境中进行软件波形仿真操作,同时借助串口调试工具打印数据,两种方式来验证Flash和nvSRAM不同工作模式下的数据读写擦等操作。在仿真中,首先在Vivado环境中完成相关配置生成SDK文件,同步在SDK生成的文件中,加载本设计的LBC驱动程序,进行编译,链接调试等步骤,生成.elf文件,进行波形仿真操作。

对于Flash操作,设计通过仿真环境,加入测试程序调试,分别进行了Flash的GPCM模式和UPM模式的片擦、扇区擦、读、写的操作仿真。

例如应用4分频/1 cycle 测试,测试代码如下:

Flash_LBC_Init_();

Flash_LBC_Chip_Erase(LBC_CS0);

Flash_LBC_Sector_Erase(LBC_CS0,0x00000002);

Flash_LBC_Program_Byte(LBC_CS0,0x-00000008,0x78);

Flash_LBC_Program_Word(LBC_CS0,0x-0000000A,0x5678);

Flash_LBC_Read_Byte(0x00000008,data1);

Flash_LBC_Read_Word(0x0000000A,data2);

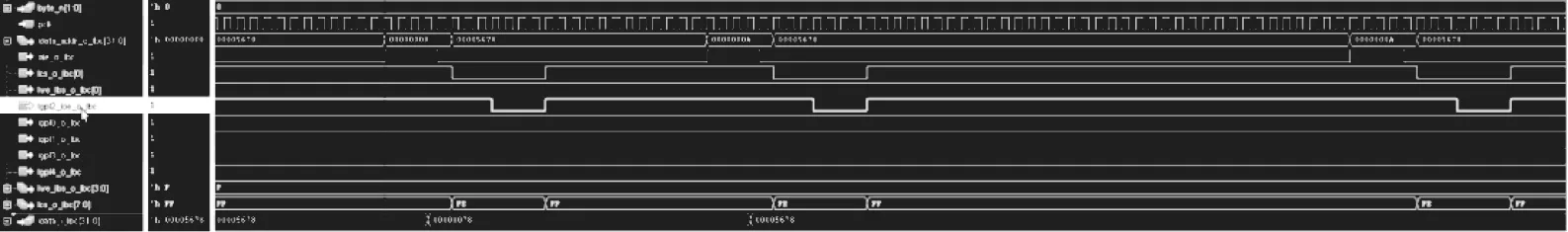

通过不同的测试程序,完成了GPCM和UPM两种模式下的全部操作,抓取地址数据波形,对比通过串口写入数据、读取数据、擦除数据打印结果,所有结果完全一致,最终驱动程序完成Flash的数据读写擦等操作。例如:Read_Byte/Word操作仿真波形如图3。

图3 Read_Byte/Word

同理,在nvSRAM操作中通过抓取地址数据波形,加入测试程序调试,分别进行了nvSRAM的GPCM模式及UPM模式的读、写、存贮等的操作,同步通过串口打印数据对比和波形仿真图抓取数据,数据结果一致,完成驱动nvSRAM的数据交换操作。

6 结语

本文完成了FT2000HK中LBC外接存储器驱动程序设计,通过文中对硬件及软件的介绍,让人们对存储器数据交换相关操作有了基本的了解,同时对外接存储设备驱动技术有了掌握。随着电子信息技术的飞速发展,数据的存储稳定性、容量已经成为直接决定数据安全、可靠的基本保障,而如何高效驱动存储器件在未来必将占据更重要的地位。