一种高速数据存储方法的设计与验证

赵 越,余红英,王一奇

(1.中北大学电气与控制工程学院,太原030051;2.山东航天电子技术研究所软件中心,烟台264010)

引 言

随着现代探测设备的发展和更新,设备获取的信息量变得更大,相应的要求存储的速率也要提高[1]。目前高速存储系统主要分为基于PC的数据采集存储系统和基于硬件平台的采集存储系统。计算机的体积限制了它在不同环境下的使用,而基于硬件平台的存储模块集成度高、体积小,可以在更多环境下应用。西安电子科技大学的安凯用2 GB的DDR3芯片作为缓存阵列,8块Micro SD卡作为存储介质,在800 MHz芯片时钟下实现了470 MB/s的存储速度[2],但芯片存储模块利用率不高。中北大学的石帅等在40 MB/s的芯片时钟下用一块FLASH芯片的两个片选使用交错式双页面编程方法实现了30 MB/s的存储速度,但没有给芯片足够的突发存储时间[3]。现有的高速采集存储系统大多通过使用存储速率更高的存储芯片来增加存储速度,在现有资源利用的角度没有做更深入的探究。本文设计的高速存储采集系统通过FPGA采集数据,用NAND FLASH芯片作为存储介质,通过FPGA直接操作NAND FLASH芯片,不仅能减小PCB占用面积,又能用流水线操作利用FLASH芯片的“Busy”时间[4]。双FIFO用“乒乓读写”技术,可以做到数据不间断的存储,保证数据的实时性和可靠性。2块NAND FLASH芯片有4个片选,通过FIFO乒乓读写结合四流水线操作可以完全发挥每一片NAND FLASH的性能,从而做到连续不间断的高速数据存储[5-6]。本系统在现有条件下,使用36 MB时钟仅用2块存储芯片就可以实现18 MB/s的存储速率,在使用同样存储速率的芯片时,流水线操作可以充分发挥FLASH芯片的性能。

1 存储系统设计方案

1.1 存储系统总体设计

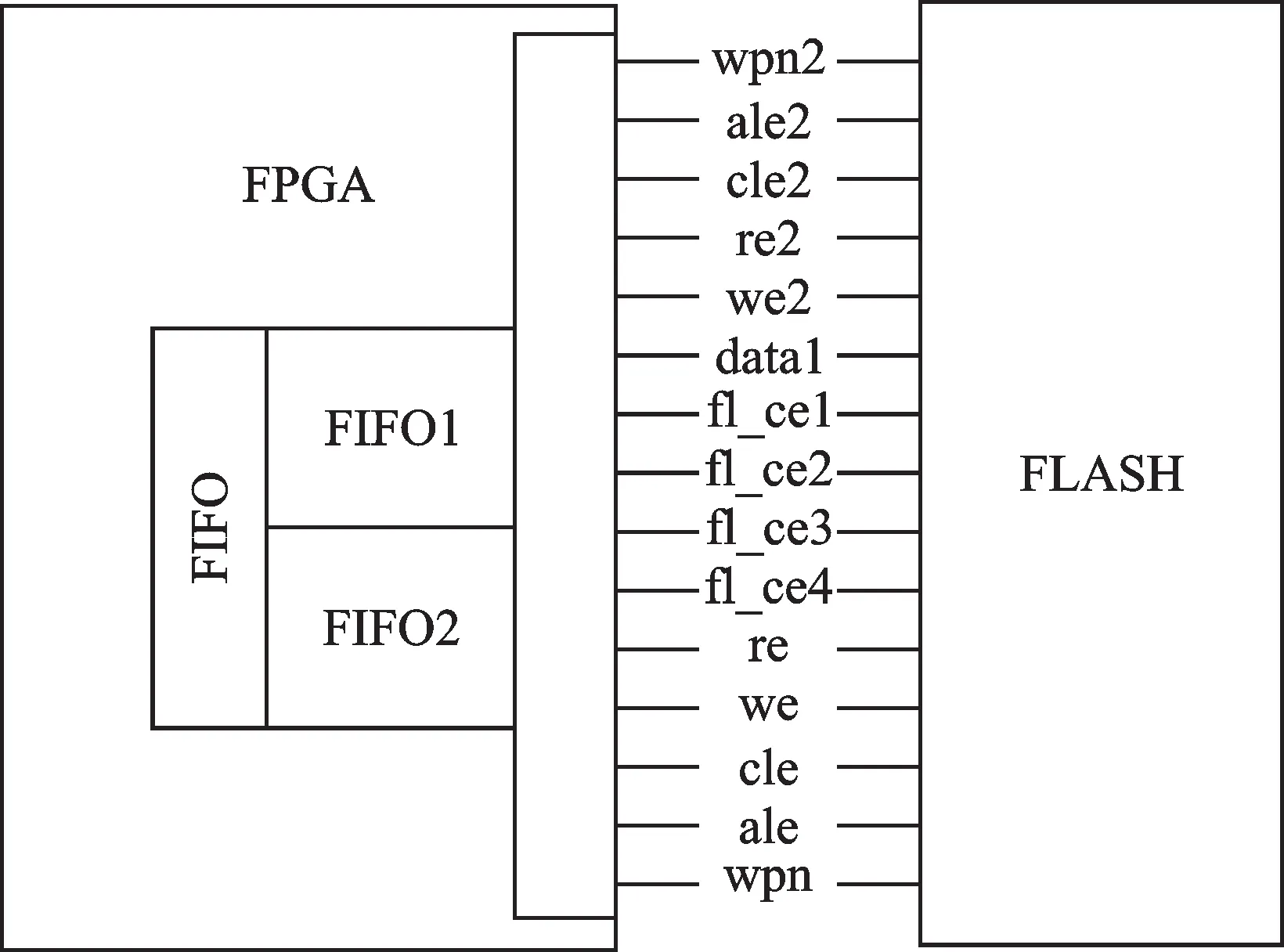

存储系统由FPGA、FIFO组成和FLASH芯片组成(见图1)。其中2个FIFO在“FIFO”模块中进行例化并控制两FIFO读写顺序。FPGA控制两FIFO的读写顺序,并将FIFO读出的数据依照4条流水线的顺序写入FLASH。

图1 存储系统设计Fig.1 Storage system design

1.2 FIFO乒乓操作和FLASH四流水线写入工作流程

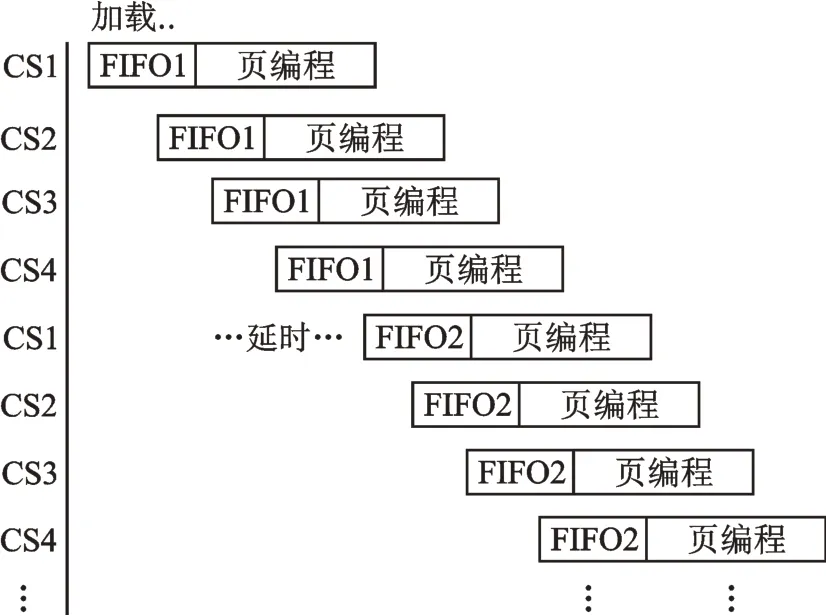

工作过程中,两个FIFO先写入相机接收到的数据,然后FIFO1数据读出,向第一片FLASH芯片写数据,完成后片选(Chip selection,CS)1需要进行内部编程,故进入忙碌时间。此时FIFO1向CS2写入数据,CS2加载完成后继续向CS3写入数据,第四步向CS4写入数据,至此FIFO1中的数据已全部读出。此时,若CS1的内部编程已完成,忙碌时间已过,则可以写入数据,进入第2个循环;否则按照实际情况在保证满足相机数据实时写入的条件下在CS4加载完成后添加延迟,等待CS1页编程完成,开始下一轮流水线操作。第二轮由FIFO2读出数据向4片FLASH芯片中写入,同时相机数据写入FIFO1。此过程不断循环,即为FIFO的乒乓读写和4条流水线数据存储的结合。四流水线写入的工作过程如图2所示。

图2 四流水线写入工作过程Fig.2 Four-line writing process

2 数据处理系统设计

设计系统的数据来源是18 MB/s相机数据,存储芯片的时钟为36 MHz。为了连续不间断且高速地存储相机返回的数据,系统采用了2个FIFO乒乓操作和4条流水线数据存储结合的设计[7]。

相机的时钟频率为18 MHz,1页内存的大小为4 KB,即4 096个字节。所以1页数据的传输时间t1(单位:μs)为

系统选择两块NAND FLASH芯片,4个片选端,采用四流水线设计。设计2个FIFO,每个FIFO的大小为16 KB,可以一次写入4页数据的同时缓存下面4页的数据[4]。相机传输4页数据的时间tc为

设计2个容量为16 KB的FIFO进行乒乓操作,当FIFO1进行写操作908μs时,FIFO2进行读操作908μs,读 出 来 的 数 据 同 步 写 入NAND FLASH;FIFO2进 行 写 操 作908 ns时,FIFO1进 行 读 操 作908 ns,依次循环,保证相机输入速率和NAND FLASH存储速率进行匹配,使红外相机的数据能连续地写入NAND FLASH中。

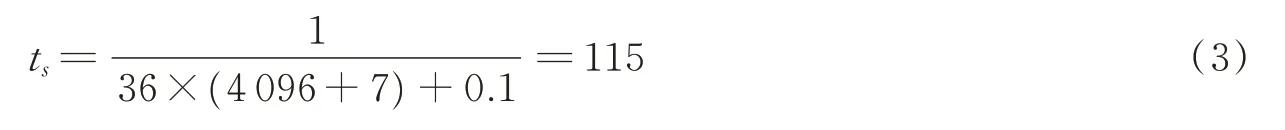

由于NAND FLASH采用36 MHz时钟,所以NAND FLASH写1页数据需要的时间为1个起始命令(80H),5位页地址,4 096位灰度图数据,1个停止命令(10H),1个0.1μs延迟[8-9]。

选用的NAND FLASH典型忙碌时间为200μs,最大忙碌时间为700μs[10]。只要保证下一次循环到CS1时CS1已经完成页编程操作,就可以保证四流水线操作的正确性,不浪费芯片性能[11]。按照最大忙碌时间700μs算,每片FLASH芯片完成加载所需的时间ts为

则4片FLASH加载完需要460μs。

芯片1忙碌完成的时间tb为

可见460μs<815μs,所以此时芯片1可能未加载完成,所以在每写完4片之后加1个400μs的延迟。所以四流水线模式写编程页(16 KB)的时间tq为

tq小于相机写入FIFO的时间tc,能保证相机数据实时写入NAND FLASH中,且满足相机传输的最大速率18 MB/s。在四流水线工作模式下Busy时间被很好地利用,极大地提高了存储速率和数据写入的连续性[12]。

3 实验验证

3.1 FIFO乒乓操作+四流水线写入FLASH的仿真验证

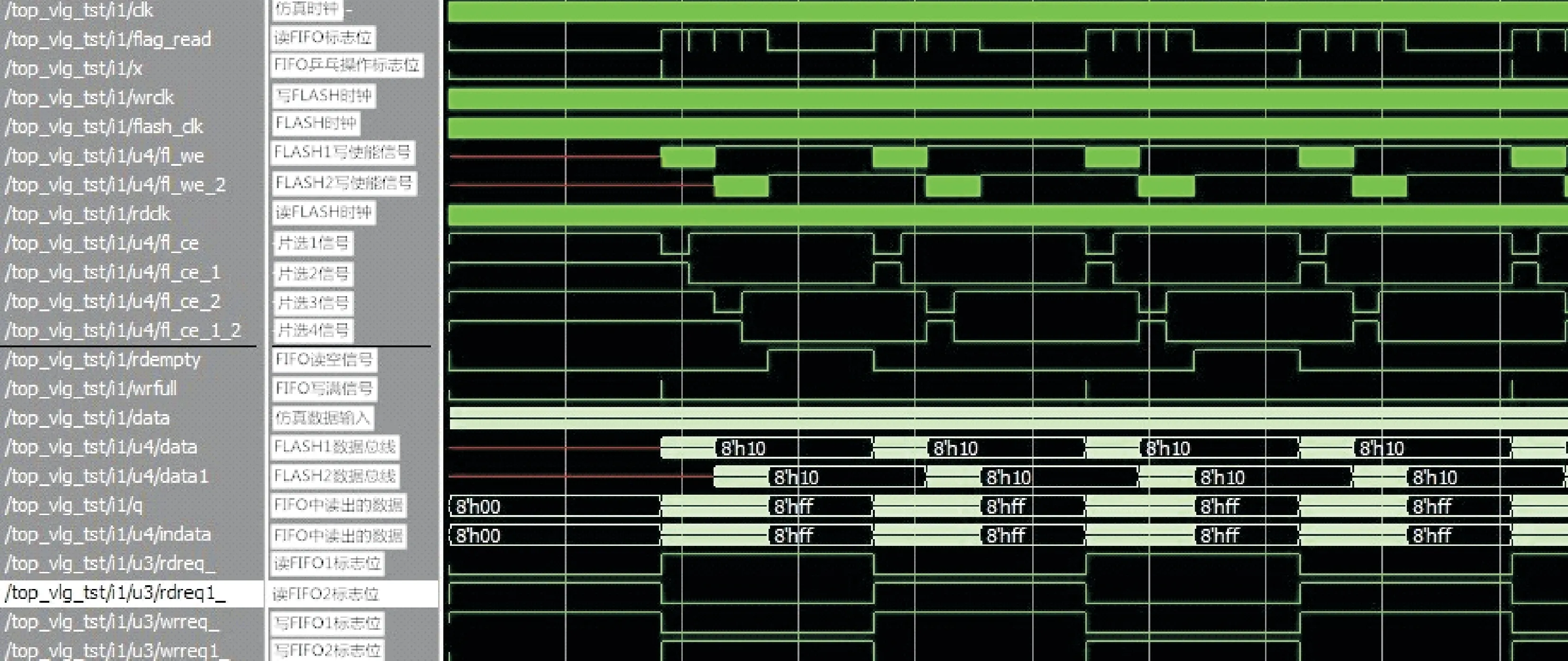

将一组连续的数据写入FIFO,再由FIFO写入FLASH(见图3)。其中flag_read是读FIFO的标志位,高电平代表读出;x是控制FIFO乒乓操作的标志位,上升沿代表切换FIFO;q和indata连在一起,是从FIFO读出的数据;U4/data是FLASH1的数据总线,u4/data1是FLASH2的数据总线;fl_ce、fl_ce_1、fl_ce_2、fl_ce_1_2是flash片选信号,低电平代表选中,分别代表芯片1到芯片4;rdreq_和rdreq1_是读FIFO的标志位,wrreq_和wrreq1_是写FIFO的标志位;fl_we和fl_we2是FLASH的写使能信号;其他信号是FLASH和写FIFO的时钟等。

图3 数据存储仿真时序图Fig.3 Data storage simulation sequence diagram

由图3可以看出,x的1个上升沿到来同时flag_read电平升高,开始读FIFO。fl_ce电平拉低,代表选中第一块FLASH的第一片存储芯片,即CS1,u4/data的数据开始随着时钟在fl_we的上升沿持续写入。rdreq_电平升高,说明读的是FIFO1中的数据。wrreq_1是低电平,FIFO2正在写入数据。每组flag_read的高电平中间有3个下降沿,是切换片选时FPGA对FLASH输入指令和地址的时间。CS1写完后fl_ce拉高,fl_ce_1电平拉低,直到CS2写完,开始写FLASH2,此时FLASH1的两个片选信号可以暂时不变,直到再次写FLASH1时根据流水线改变电平。u4/data和u4/data1是写FLASH的信号,所以结束后要给FLASH一个结束信号10H。

用上位机软件将红外图片转换为图像数据,并作为i1/data的数据;将程序下载到硬件系统中,待FLASH写入完成后连接上位机将FLASH中的数据读取并显示图像,结果如图4所示。

图4 仿真数据显示Fig.4 Simulation data display

通过仿真验证,FIFO乒乓读写和FLASH片选可以正确工作。

3.2 硬件系统的采集存储试验验证

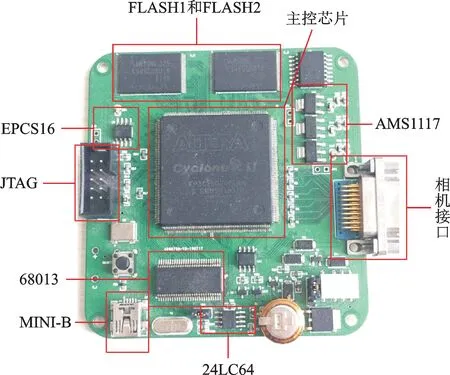

(1)硬件系统总体设计

相机采集存储系统由红外相机、FPGA主控系统、存储部分、电源部分和上位机组成(见图5)。

(2)硬件设计

电源模块主要由3个AMS1117分别给系统提供1.2 V、2.5 V和3.3 V的电源电压,供PCB上其他模块使用。

主控系统由主控芯片及其外围电路组成。主控芯片选用飓风3系的EP3C25Q240C8N,功耗较低,资源适合本系统;程序下载用10针JTAG下载口,程序固化在EPCS16里。

图5 硬件总体设计Fig.5 Overall design of hardware

红外相机的型号为LA6110,分辨率为640×512,探测帧频为50 Hz,时钟频率为18 MHz,输出的数字信号支持Camera Link协议。

为了得到完整的红外相机图像,突发存储速度需达到36 MB/s。存储系统由两块NAND FLASH组成,采用三星的K9WBG08U 1M,时钟频率36 MHz,其大小为4 GB,2个一共8 GB,每块NAND FLASH内部有2个片选端,可以通过片选来操作具体的片。1片有8 192个块,1块有64页,1页有4 KB的存 储容量。

USB2.0通信模块由MINI-B、68013和24LC64组成,可将FLASH中的数据传输到上位机。

将主控芯片、电源管理、存储芯片和接口等设计在1块9 cm×8 cm的PCB上,集成度更高,小体积的特点使本系统可以应用在更多场景。如图6所示为PCB的设计。

图6 系统PCB设计Fig.6 System PCB design

(3)硬件存储系统验证

编写一个伪随机码生成模块,生成9阶伪随机码[13]。将生成的伪随机数写入到NAND FLASH中,再用上位机读取出来,通过MATLAB仿真软件可以将原始码与上位机读出的伪随机码做相关检测,得到的误码率即为存储的误码率。用线性移位寄存器生成伪随机码,每次将9位2进制数的最高位提取输出,然后将伪随机数左移一位,最高位和第4位进行异或运算,并将结果补充至最低位。将FPGA生成的伪随机码写入NAND FLASH中,用上位机读出的数据如图7所示。

图7 上位机读出的数据Fig.7 Data read by the host computer

将读出的数据与原始码进行相关性检测试验,为方便观测,每次截取100 KB的数据进行相关检测(见图8)。所有数据完成检测后,误码率约为10-6,数据比较可靠,对本试验的影响可忽略。

图8 相关性检测试验结果Fig.8 Results of correlation test

将存储系统连接到红外相机,接通电源后红外相机数据存储到NAND FLASH中,然后连接上位机将NAND FLASH中的视频读出。上位机显示的相机图像如图9所示。

图9 上位机显示的相机图像Fig.9 Camera image displayed by the host computer

由图片可以看出,画面正常无坏点,纸盒上的“DDS”“仰卧板”等字样清晰可见。实验表明红外相机的图像得到正确的存储和读取。

4 结束语

经过试验验证,系统可以实现18 MB/s的红外相机数据实时存储。存储系统具有较强的适应性,在存储速率要求更高的条件下增加芯片数量,可以更好地

利用FLASH的Busy时间,在保证数据存储连续性的同时,在同样的芯片性能下达到更高的存储速度。若使用n组流水线,每组多个芯片流水处理,n组并行存储的方法,可以达到n倍FLASH时钟的存储速度。