基于RS422+LVDS高速长线通信的设计与实现

李建翔,王洪凯,杨玉华,刘东海,李秋媛

(1.中北大学,仪器科学与动态测试教育部重点实验室,电子测试国家重点实验室,山西太原 030051;2.北京航天长征飞行器研究所,北京 100076)

0 引言

近年来,在测试测量技术领域以及众多产品的测试系统中,面临着各种严苛的条件,对信号传输的稳定性提出了更高的要求[1],成为目前亟待解决的重要课题。由于并行传输成本高、占用资源大,且并行传输对线路之间的物理性质要求高,细微差别就可能导致数据不能同时抵达接收端,造成接收错误,所以远距离传输往往选用串行传输方式。常用的串行接口标准有RS232、RS422、CAN总线以及LVDS传输。

在本次任务方案中,设计了一种以FPGA为核心的高性能远距离低误码率的传输方案,本文主要研究对象为某接口通信链路的搭建及其可靠性的测试。综合考虑各种串行接口的优缺点,同时兼顾传输距离、成本以及可靠性等各方面因素,最终选择RS422及LVDS相结合的方式,并在其软件设计中分别加入校验字及校验码的设计,保证其传输的可靠性。

1 测试平台设计

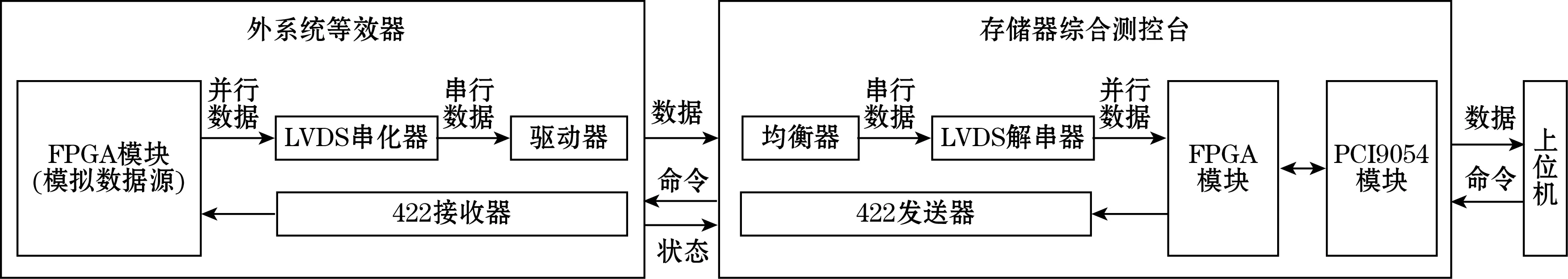

系统总体框图如图1所示。外系统等效器用于模拟外系统接口及功能仿真,实现对地面系统的全面覆盖性测试考核。其工作的主要流程是:上位机发送控制指令,经由PCI9054到达FPGA模块,422收发器模块用于转发指令并回传状态,控制对应的外系统等效器发送数据,该数据经过高速LVDS传回上位机,最后进行分析数据是否正确,以验证该方案可行性。

图1 总体框图

2 硬件电路设计

2.1 RS422指令收发与状态回传模块

RS422作为一种能够进行差分传输以及支持多点通信的数据传输协议,抗干扰能力比较强。在进行电路设计时,需要考虑避免信号异常而导致的接口损坏,同时避免设备间的互相干扰[2],所以采用隔离电路。传统电路往往采用RS422芯片、电源隔离芯片和光耦的方式,电路复杂且成本较高。而ADM2682E芯片可配置为半双工或全双工模式,内部集成了一个5 kV rms的隔离电源,省去了外部配置DC/DC模块[3],从而能够很大程度简化电路,降低成本。RS422接口电路如图2所示。

图2 指令收发与状态返回

在电路配置方面,应在ADM2682E芯片所有的电源引脚与地引脚之间并联1只大电容和1只小电容作为旁路电容,以起到降低噪声的作用[4]。

ADM2682E的输入端具备短路故障保护功能,能够在短路时保证接收器输出为高电平。或者如图2中所示,分别在输入端接上拉电阻RM以及下拉电阻RN,确保其正负压差大于200 mV(芯片门限电压),始终输出为高电平,保证芯片工作在稳态。为了防止芯片短路,在输出端各串接1只51 Ω的电阻。同时RS422还要求在终端跨接1只阻值约为其传输电缆阻抗的电阻,这里选用阻值为120 Ω的电阻,减小信号的反射,有效提高信号的可靠性。

2.2 LVDS发送端模块

LVDS(low voltage differential signaling)作为一种低压差分信号,能够在保证数据高速传输的同时,提供低功耗、低误码率、低串扰、高噪声抑制能力等其他传输模式不可兼备的优势,可以实现点对点以及一点对多点的连接[5]。LVDS传输技术本身具有很低的电压摆幅,因此能够很快地改变状态,提升信号的传输距离;与此同时其输出模式是低电流驱动,所以它具备很好的抗干扰性能。

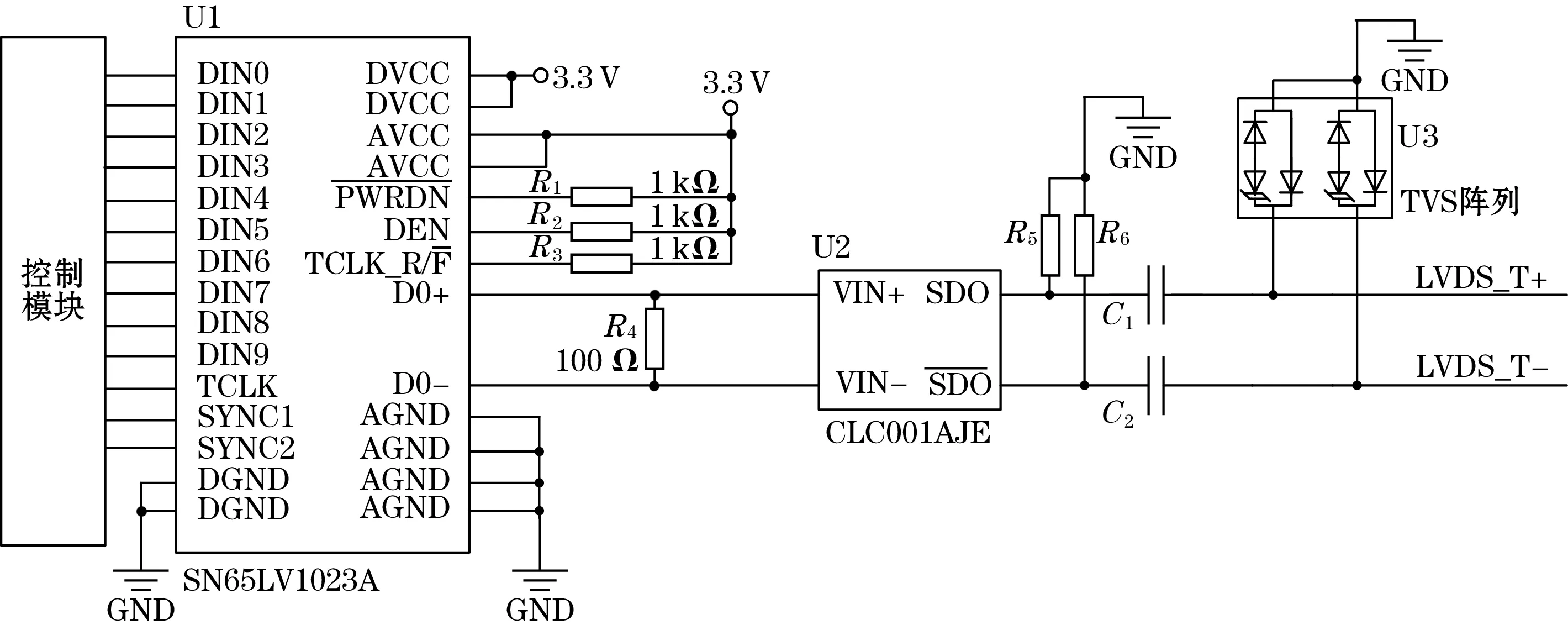

在LVDS传输链路发送端,选用SN65LV1023A串化器,将并行数据转化为串行数据,其串行传输速率能够覆盖100~660 Mbps,本身传输距离仅有十几m,为了满足远距离传输,在发送端增加高速电缆驱动器CLC001AJE,以此倍增差分信号的驱动能力。在端口处配合TVS阵列,增强传输线路保护能力。LVDS发送电路如图3所示。

图3 LVDS发送端电路

2.3 LVDS接收端模块

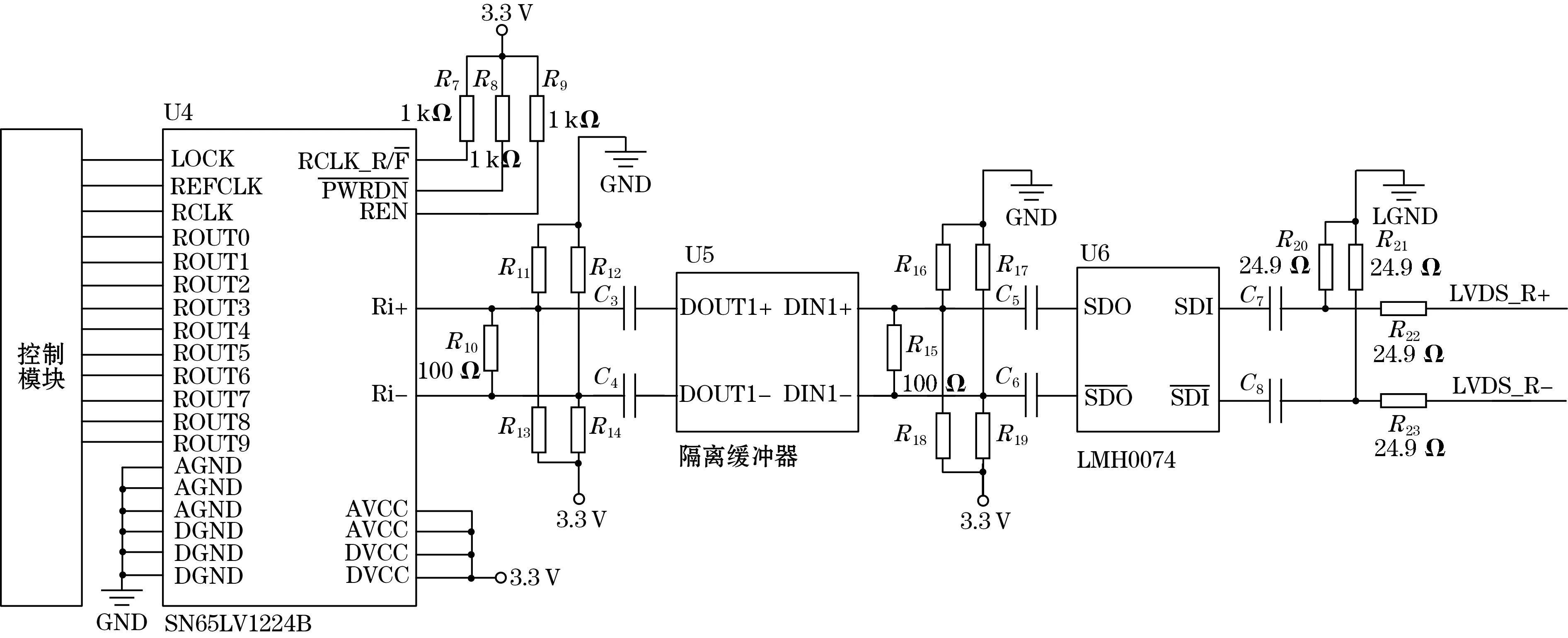

LVDS信号经过长距离传输后,信号会有一定程度的衰减,其衰减的程度与信号频率的平方根和电缆长度之积成正比[9],因此当接收端收到LVDS信号后,要对其幅频特性和相频特性进行修正和补偿。接收端电路设计如图4所示。LVDS信号经过90 m长电缆传输后先经自适应电缆均衡器LMH0074进行修正补偿,再经过LVDS隔离缓冲器输入到解串器SN65LV1224B,最后传输到FPGA模块。

图4 LVDS接收端电路

为了保证信号的可靠性,阻断外部干扰,在信号进入解串器前便进行隔离。通过串接1只LVDS隔离缓冲器,有效防止地信号的耦合性。其相较其他产品有更好的工作性能,数据速率可高达600 Mbps,并且具有极低抖动,有效抑制电源纹波和毛刺现象。C3、C4、C5、C6均为隔直电容,实现AC耦合,提供直流偏压,滤出直流分量。

自适应电缆均衡器LMH0074工作范围很广,可支持的速率能够覆盖125~540 Mbps范围,输出经过交流耦合后经电阻网络变为标准LVDS信号送入下一端口。在接收端分别在差分线串上接24.9 Ω的电阻用来匹配双绞线的线路阻抗;C7、C8作为隔直电容实现AC耦合。信号在发送端的波形如图5(a)所示,在经过90 m电缆传输后的波形如图5(b)所示,在接收端经过电缆均衡器LMH0074的波形如图5(c)所示。由图中可以看出,在LVDS信号经过电缆传输过后,其波形并不理想,而LMH0074能够自适应补偿衰减的信号,使衰减过的信号较好地与发送端保持一致,从而保证SN65LV1224B解串成功。

(a)LVDS发送端波形

3 软件可靠性设计

本文在对硬件电路设计的前提下,为了保证通信链路的可靠性,同时对嵌入式软件也做出抗干扰设计。在指令传输链路中加入校验字环节,提高指令识别的可靠性;在LVDS传输中加入半字节CRC校验环节,降低误码率。

3.1 指令收发可靠性设计

存储器综合测控台向外系统等效器发送命令,外系统等效器向存储器综合测控台反馈状态,传输码率为625 Kbps。

在指令内容较短时,譬如只有2个字节,往往采用三判二机制,即测控台连续发送3次命令,等效器正确检测到2次命令后,才可以执行该命令[11],有效防止因偶然性而导致的指令错误下发。而当指令内容稍长时,则采用校验字的方式,本次指令内容如表1所示,校验字内容采取指令内容按位异或方式计算求得。

表1 指令信息表

3.2 数据传输可靠性设计

循环冗余校验(cyclic redundancy check,CRC)是一组自行规定或使用国际标准的校验码,附在原始数据尾部,用于校验在传输过程中是否产生误码以及丢数[12]。

在硬件优化的前提下,在信号的传输过程中增加CRC校验的过程。本文综合硬件与软件相适应的考虑,选择半字节CRC查表法的校验方法,既能保证传输码的质量,也不会给硬件造成负担。半字节CRC查表法所构成的码值只有16种,简单可靠。其对应的校验码表如表2所示。

表2 CRC校验码表

LVDS数据在发送端的打包格式为4字节帧头+8 192字节数据(8 K数据)+4字节CRC校验码,共8200字节。其校验码的生成格式如下,先将寄存器内初始值设置为0,然后将数据按半字节依次移出,将移出的半字节与寄存器内的值相异或,将所得值查表得到新的表值再异或到寄存器中,循环往复,最终产生CRC校验码附于数据包后发送给接收端。

接收端收到数据后,要对数据进行校验确定其是否无误码。校验关键代码如下:

If Data_cnt=8199 then

if D_lvds_din & Check=CRC_out

then

Error_flag_q <= ’0’;

F_send_flag <= not F_send_flag;

F_wr_pt <= F_wr_pt+1;

当一包数据发送完毕后,即从0计数到8 199,需校验其数据码流(D_lvds_din)与校验码流(Check)是否与收到的数据(CRC_out)一致,若一致则Error_flag_q置0,继续接收下一包数据。利用ChipScope在线分析数据包如图6所示,收到数据与发送数据一致,校验成功,传输无误。

图6 CRC实时校验

数据在传输过程中会出现误码丢码的现象,此时Error_flag_q则会拉高,触发自动重传机制,要求发送端重新发送该包数据,为了避免出现一直发送同一包数据的情况,导致后续数据不能正常传输,在软件逻辑设计中规定同一包数据的自动重传指令最多发送3次,3次之内接收正确或者连续3次接收错误,则继续发送下一包数据,其关键代码如下:

if Error_flag_d =′1′ then

cc_sent_flag <= ′1′;

Send_cmd_CS<=

(X″5A″,X″54″,X″C9″,X″69″,X″39″,X″99″);∥

重传指令

若出现连续误码时,则如图7所示,接收端会发送3次重传指令。

4 实验验证与分析

通过上位机反复大量读取数据,测试其误码率,数据结构如图8所示,一包数据包括:包头2字节,用于识别数据包类别;包计数2字节,用于校验其连续性;数据有效内容1 019字节,不同数据包内数据内容不同;最后为1字节校验位,均为每包中有效数据之和,用于校验数据内容是否正确。

图8 数据结构

为了验证本设计的可靠性,在实验过程中用6段电缆组成90 m传输线路连接外系统等效器及存储器综合测控台,分别采用不同的速率对其可靠性进行验证,更改程序调整速率,通过多次试验测试,在不同情况下LVDS传输可靠性表现如表3所示。

表3 LVDS传输测试

结果表明:在90 m电缆下,通过软硬件的共同优化,数据可以达到240 Mbit/s的零误码传输。指令下发加入可靠性设计后均能100%正确动作,且经过驱动器及均衡器的作用,LVDS数据能够大幅提高长线传输的能力,但由于在软件中加入CRC校验等算法,实际速率相较理论速率会有一定的下降。

5 结束语

本文结合RS422和LVDS进行了一种通信传输链路的设计,在硬件电路满足技术要求的前提下,极大程度简化硬件电路;同时在软件设计中,指令收发模块和数据传输模块都进行了可靠性设计,在保证传输质量的前提下极大提高了传输速率。经验证,本设计能够满足任务要求,达到预期效果。