基于PFGA的相位检测系统设计

摘 要:传统的相位检测主要依靠模拟电路实现,响应速度很快,但精度不高。为了解决相位检测器因对环境较为敏感而影响其检测精度的问题,提出一种基于FPGA的相位检测系统。该系统由模拟电路和主控芯片FPGA组成,将模拟电路响应速度快、数字电路测量精度高的优点充分结合;将两路被测信号通入滤波器滤除干扰,然后通过过零比较电路将信号转换成方波,最后将方波输入FPGA中,使用高频脉冲进行插补计数,实现对信号相位的精确检测。

关键词:相位检测;FPGA;高频脉冲计数

中图分类号:TN763.3 文献标识码:A文章编号:2096-4706(2021)19-0060-04

Design of Phase Detection System Based on PFGA

LENG Congyang

(College of Mechanical Engineering, Chongqing University of Technology, Chongqing 400054, China)

Abstract: The traditional phase detection mainly depends on the analog circuit, which has fast response speed, but low precision. In order to solve the problem that the phase detector is sensitive to the environment and affects its detection accuracy, a phase detection system based on FPGA is proposed. The system is composed of analog circuit and main control chip FPGA, which fully combines the advantages of fast response speed of analog circuit and high measurement accuracy of digital circuit; the two measured signals are passed into the filter to filter out the interference, and then the signal is converted into square wave through the zero-crossing comparison circuit. Finally, the square wave is input into FPGA, and the high-frequency pulse is used for interpolation and counting to realize the accurate detection of signal phase.

Keywords: phase detection; FPGA; high-frequency pulse counting

0 引 言

當今世界,科学技术日新月异,相位检测技术的重要性日益凸显。随着国家对国防建设需求的不断提升,航空航天技术的不断发展,对相位检测技术的精度和抗干扰能力提出了更高的要求[1]。在传统的相位检测系统中,需要采用电容器和电阻器共同完成相位的检测,很难达到较高的精度,对于不同频率、不同类型的信号需要进行相应的调节才能实现相位检测,不但增加了检测者的工作量,而且不能满足高精密制造对高精度相位检测技术的需求[2]。董淑豪等提出一种结合运用DDS信号发生器和模拟电路的鉴相方法[3],将精度做到了0.000 1°,虽然精度很高,但是由于加入了DDS模块,使检测系统的制造成本大幅提高。本文提出一种基于现场可编程门阵列(Field Programmable Gate Array, FPGA)的数字相位检测系统,无须进行器件调节,就可以满足多种频率、多种类型信号的高精度检测,不但满足抗干扰要求,而且检测精度大大提高。

1 相位检测系统

本相位检测系统的工作原理是将有相位差的两路信号一起通过滤波器消除干扰因素,然后通过LM211过零比较模块将原信号变成两路有相位差的方波,将方波送入FPGA中进行异或运算,得到与相位差相对应的高电平长度和周期,最后将高电平时间和周期进行高频信号的插补,得到输入信号周期和相位差信号高电平长度的数字信息,通过串口将信息发送至上位机进行相位差的显示,实现两路信号相位差的高精度数字测量。整个检测系统的系统框图如图1所示。

2 高效滤波器模块

滤波电路可以消除输入信号的谐波成分,提高电路的抗干扰能力[4],为提高相位检测的准确性提供保障。为了使输入信号在高频段能够以较快的速率下降,从而提高滤波器的滤波效果,在一阶滤波器的基础上再增加一个RC低通滤波环节,形成二阶滤波电路。相较于一阶滤波电路,二阶滤波器的滤波效果更好,幅频特性更优。滤波器的具体电路如图2所示。

3 过零比较电路

通过过零比较器,可以将滤波器的输出信号转变为能在FPGA中进行运算的方波信号,交流信号分为零点以上的部分和零点以下的部分,通过电压比较器,将交流信号与零位电压相比较,大于零的部分置为高电平,低于零的部分置为低电平。本文选择LM211电压比较器,因为其响应时间较短并且准确度较高,能提高相位电压比较的速度和精度,进而提高相位检测精度。较宽的输入电压范围也让相位检测系统能够适用于更加复杂的使用环境,提高抗干扰能力。具体的电路设计和示波器显示输出波形如图3(a)、(b)所示。

4 FPGA程序设计和比相算法

4.1 相位差信号获取

将两路有相位差的电信号转换成对应的方波信号后,如何通过高精度的计算将信号之间的相位数据计算出来成为相位检测系统的关键。为了能将两路信号的相位差用电信号表示出来,在FPGA运算中,首先对两路信号进行二分频处理,将信号的周期扩大为原来的两倍,然后对周期扩大的信号进行异或处理,得到两个方波的信号差P,并且随着相位差的扩大,P的高电平时间越来越长,信号仿真如图4所示。

4.2 高频计数时钟设计

得到相位差波形后,使用FPGA的高频时钟进行计数,读出波形P的高电平时间就是方波信号a和方波信号b的相位差。为了得到更高精度的数据,理论上通入的时钟信号频率越大,计数的数值就越大,从而检测的精度也就越高。然而,由于FPGA受外部的晶振频率限制,一般石英晶体能提供50 MHz的工作频率,如果检测信号为10 kHz的正弦信号,相位检测的最大分辨率为:

(1)

在计数时钟的计数频率为50 MHz时,根据式(1)可以计算出相位检测的最大分辨率为0.072°。

在我们的日常生活用品制造业中,这种检测精度已经能够满足使用要求,但是在国防军工和航天航空等高精尖领域,这样的精度还远远不够。因此,结合FPGA的工作原理,利用FPGA中的锁相环技术进行倍频操作,提高检测精度[5,6]。锁相环(Phase-Locked Loop, PLL)是一种反馈控制电路,通过读取输入信号的频率和相位等参数信息,调节环路内部信号对应的参数。利用锁相环能够对输出信号和输入信号的频率进行主动跟踪的特性,一般将锁相环运用到闭环跟踪电路中。在现代电子信息技术中,为了使电路具有更高的振荡频率,通常采用石英晶体作为开发板等电子设备的振荡器,石英振荡器的振荡频率虽然较高,但是不能对频率进行调节,所以不能应用于一些需要频率发生变化的场景,利用锁相环、分频器、倍频器等频率合成技术,可以得到更多更稳定的振荡信号。本文利用锁相环进行5倍频生成250 MHz的高频信号,并通过锁相环的功能生成四路相位依次相差90°的不同相位时钟信号,用Verilog语言编写加法器,加法器将四路检测到的信号相位相加,得到精确的信号周期信息和两路信号的相位差信息。最后通过式(1)可以算出,通过改进计数时钟频率的相位检测系统在检测信号的频率为10 kHz时,其测量分辨率可以达到0.0036°。这在目前的高精尖制造中完全可以满足要求。

4.3 串口通信模块设计

通过有效的方式快速准确地将相位信息显示出来也是关键。由于相位信息的数据量不大,并且对速度的要求不高,所以采用通用的串口通信技术[7,8],将相位信息发送至上位机进行显示。借助通用异步串行收发通信技术可以和多种标准串行数据总线相连接,因为这种通信方式的数据结构非常简单,而且还可以根据需求改变数据位,通信协议也较为简洁,所以在工程中得到了广泛的应用。本文采用硬件编程语言Verilog[9],以状态机的方式进行顶层文件的设计,实现相位数据与上位机的通信连接。该数据发送模块采用57 600的波特率进行通信,应用50 MHz的时钟,需要对时钟进行55分频。状态转换图如图5所示。

整个数据发送模块又由五个状态构成,分别为空闲等待状态(IDLE)、起始发送状态(START)、移位等待状态(WAIT)、移位状态(SHIFT)和停止状态(STOP)。电路上电后进入复位模式,状态机进入空闲等待状态(IDLE),数据发送器等待发送使能信号Send-en的上升沿,当上升沿来临,发送器立即进入起始发送状态,开始对数据的起始位(即逻辑零)进行發送,同时进入等待的状态。满足发送条件时就对数据进行依次移位发送,对于任意的单个数据发送完成后立即回到等待状态,当一帧数据发送完成后进入停止状态,等待下一次的发送命令。

5 仿真模型和实验平台的搭建

在可编程片上系统(System on a Programmable Chip, SoPC)设计平台Quartus上进行仿真验证和实验程序编写。使用Verilog硬件编程语言分别编写输入信号稳定模块、方波分频模块、两个信号异或模块、计数时钟倍频模块和串口通信模块。其中,计数时钟倍频模块通过锁相环产生四路一次相差90°的五倍频信号,通过加法器功能将四路信号相加后,再利用串口通信模块将其发送至上位机进行相位信息的显示。Verilog程序设计总框图如图6所示。其中,PLL为时钟倍频模块,Count为将四路检测信号相加的加法器模块,Uart为串口通信模块。所搭建的实验测试平台如图7所示。

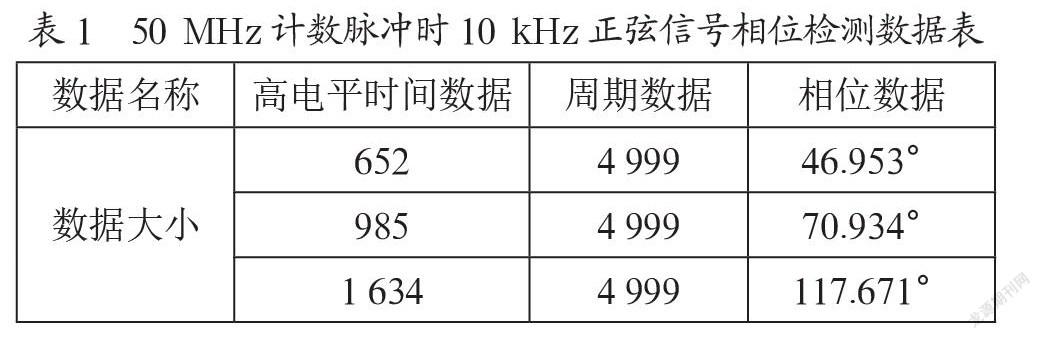

将有相位差的两路信号通入相位检测系统中,当采用FPGA晶振的原始计数频率(50 MHz)作为计数时钟时,实际测量精度数据如表1所示。

由表1可以看出数据的精度不高,计数脉冲频率较低,造成周期数据太少,影响检测精度。表2是采用锁相环倍频技术以及将四路检测信号通过Verilog硬件编程语言编写的加法器相加得到的相当于1 GHz计数时钟的相位检测数据。

由表2可以看出,相较于50 MHz的计数脉冲,通过高频计数处理的计数脉冲能将周期分成更多的数据点,得到更大的数据量,从而实现更高精度的测量。

6 结 论

这种基于FPGA的相位检测系统可用于对多种频率的信号进行相位检测,并且减少了模拟电路的使用,大大提高了整个系统的抗干扰能力,其中大部分的模块都是通过Verilog语言编程实现,方便后期的改进和调节。通过实验的数据可以得出,采用的计数脉冲频率越大,整个系统的稳定性越高,当输入信号为10 kHz时,其最大分辨率能达到0.003 6°,相位检测较为准确。

参考文献:

[1] 冯健朋,赵小勇.航空发动机振动不平衡相位检测方法研究 [J].燃气涡轮试验与研究,2018,31(3):38-42.

[2] 刘小康,彭凯,王先全,等.纳米时栅位移传感器的理论模型与误差分析 [J].仪器仪表学报,2014,35(5):1136-1142.

[3] 董淑豪,吴东岷.基于FPGA的高精度鉴相器实现 [J].电子技术应用,2020,46(10):57-60+78.

[4] 康学福.滤波电路频率特性的仿真分析 [J].国外电子测量技术,2014,33(1):40-42+49.

[5] 肖帅,孙建波,耿华,等.基于FPGA实现的可变模全数字锁相环 [J].电工技术学报,2012,27(4):153-158.

[6] 余成波,张林,龙曦.基于FPGA数字PLL谐振频率的跟踪研究 [J].重庆理工大学学报(自然科学),2019,33(4):141-146.

[7] 殷安龙,张持健,陈林,等.基于FPGA的多串口通信设计与实现 [J].电子设计工程,2016,24(17):45-47.

[8] 罗超,刘昌禄,胡敬营.一种基于FPGA的并行CRC及其UART实现 [J].电子测量技术,2016,39(2):147-150.

[9] 李浪,邹祎,李仁发,等.Verilog HDL语言的AES密码算法FPGA优化实现 [J].重庆大学学报,2014,37(6):56-64.

作者简介:冷从阳(1996-),男,汉族,重庆璧山人,硕士研究生在读,研究方向:智能仪器与传感器。