激光制导伪随机编码信号解码技术

曹晓荷,朱 斌*,尚建蓉,王升哲,郑 杰,范文瑞

(1.西南技术物理研究所,成都 610041;2.火箭军装备部驻成都地区第四军事代表室,成都 610000)

引 言

半主动激光制导技术具有命中精度高、结构简单、作战费效比低、战场灵活性好等特点,广泛应用于激光制导炸弹、低成本迫击炮弹及多模复合制导导弹中,是精确制导武器中常用的制导体制之一[1]。随着角度欺骗式干扰、高重频激光干扰等有源干扰技术的发展,半主动激光制导武器通常采用较复杂的编码技术和窄时间波门技术,以提高其抗干扰能力[2]。与周期型脉冲编码(包括精确频率码、脉冲调制编码、有限位随机周期码)、等差序列码相比,伪随机编码具有类似于随机信号的特征,在单次制导过程中(6s~30s时间)周期几乎不会重复,使得敌方较难精确识别与有效对抗,是激光制导系统常用的编码方式。

在同一战区内对多个目标进行攻击时多个目标指示器互相干扰,以及存在敌方有源干扰的作战环境下,采用激光编解码可有效提高激光制导武器系统的抗干扰能力和作战效能[3]。为保证激光制导武器的命中精度和可靠性,考虑编码方式抗干扰性的同时,还需保证解码的实时性和准确性。解码器需快速识别出激光制导编码信号,为控制系统提供准确的目标位置信息,才能实现对目标的快速精确捕获跟踪。因此,解码算法对码型类别、骨架周期、子序列脉冲间隔等参量的识别效果和解码时间是考量解码器的两个关键指标。常用的解码算法有:序列搜索法[4]原理相对简单,但运算量大、效率低且容错率小;LI等人提出的基于时间差分自相关矩阵的编码解算方法可确定循环帧周期、脉冲个数及分布参量[5],但解码时间较长,且易受干扰脉冲和漏脉冲的影响;SHAO等人[6]采用基于最小周期识别方法进行编码识别,可准确识别编码类型和骨架周期,但对不存在最小周期的伪随机码识别效果不佳;参考文献[7]~参考文献[9]中采用的基于自相关函数的解码方法只能识别周期型编码的帧周期,无法识别伪随机编码;参考文献[10]中提出的滑动匹配相关解码法,将接收到的子序列在预设编码脉冲中遍历进行滑动匹配,解码时间较长且易受干扰脉冲影响。

针对半主动激光导引头制导需求,本文中提出一种基于现场可编程门阵列(field-programmable gate array,FPGA)的激光伪随机编码信号解码器设计方案。解码过程中,在搜索识别阶段采用基于数字匹配滤波器的识别方法,对预设编码抽样序列和实时信号抽样序列计算互相关函数,计算结果为1,则匹配识别成功;锁定跟踪阶段,采用自适应扩展实时波门技术,根据上一波门中检测到的脉冲情况自适应设置下一实时波门的时刻和宽度,对目标持续跟踪。基于FPGA芯片实现解码器硬件设计,采用“数据链”的方式实现超大容量的数据存储和传输,采用状态机转换保证识别和跟踪的时序稳定性。

1 伪随机编码原理

伪随机编码通常采用线性反馈移位寄存器(linear feedback shift register,LFSR)生成,一种是根据线性反馈移位寄存器输出值(0或1)确定是否发射激光,称为LFSR调制码;一种根据线性移位寄存器当前状态值(0-1序列)确定脉冲间隔进行编码,称为LFSR状态码[11]。LFSR调制码存在最小脉冲间隔ΔTmin,用以ΔTmin为周期的干扰脉冲即可对其产生有效干扰。LFSR状态码不存在最小脉冲间隔,抗干扰能力更强[12],其编码方式为:

(1)

式中,ΔTi为第i(1≤i≤M-1)和i+1个脉冲之间的时间间隔;ΔT0为基准时间间隔;ΔTd为脉冲间隔增量;Tr为随机扰码;ki为脉冲间隔跳变数,由二进制序列[a1…as]的十进制值确定,序列由s级LFSR产生。

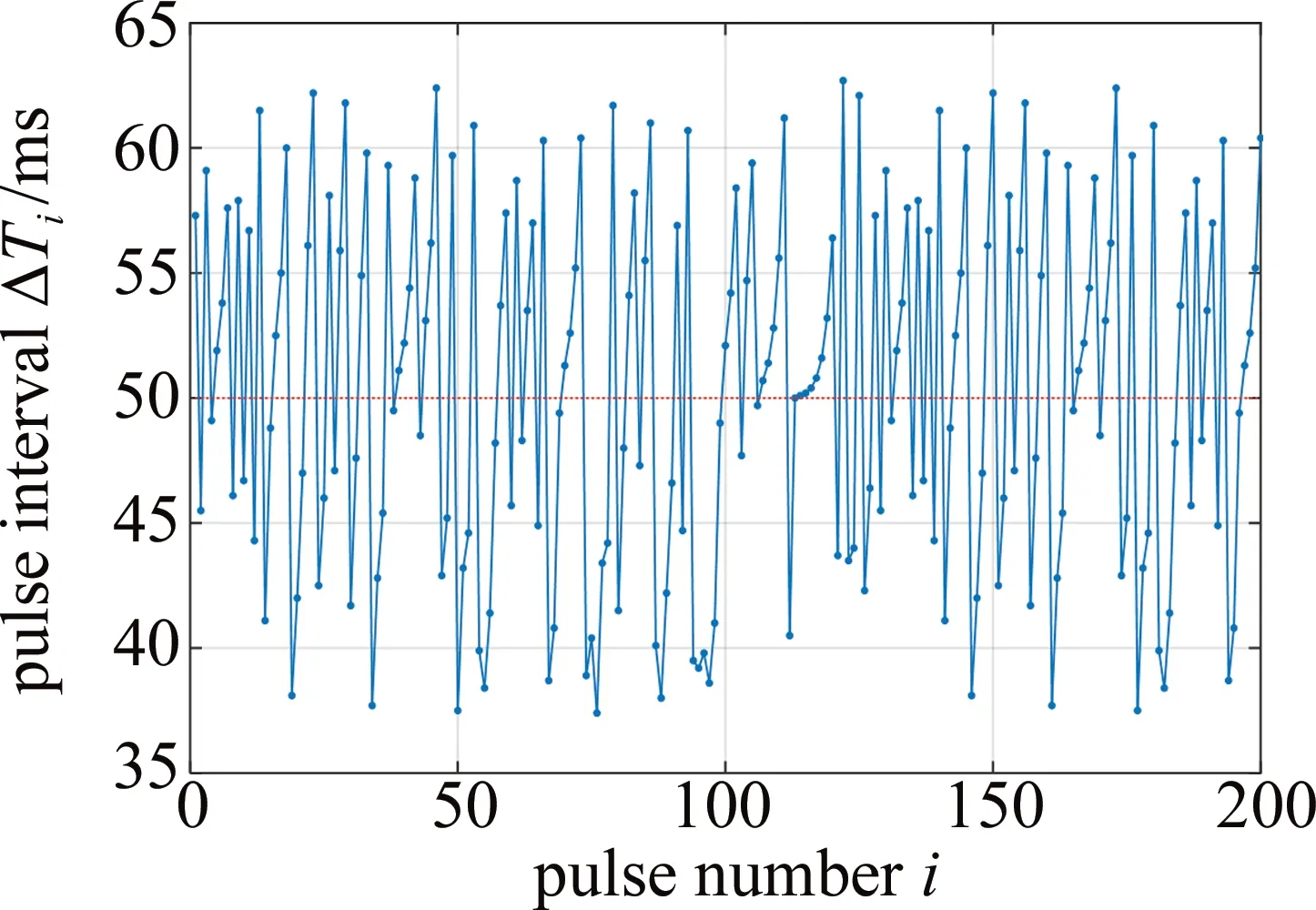

按照(1)式所述编码方式,在MATLAB软件中仿真生成LFSR状态码,设定线性反馈移位寄存器级数s=8,初始种子为[a1…a8]=01001001,反馈系数为[c1…c8]=11111110,ΔT0=50ms,ΔTd=0.1ms,结果如图1所示。以单次制导过程时间为10s,激光目标指示器发射指示激光频率为20Hz计算,共需200个激光脉冲用于导引头制导,LFSR状态码可满足制导过程中脉冲时间间隔不重复的需求。

Fig.1 Pulse intervals of LFSR status code

2 激光制导信号解码原理

在制导过程中,四象限探测器接收目标反射的激光回波,经放大电路、模数转换为方波脉冲序列送至信息处理单元;搜索识别阶段,解码器接收到综合控制器发送的码型参量后,采用基于数字匹配滤波器的识别方法,根据预设编码码字设置抽样窗口,对预设编码抽样序列和实时信号抽样序列计算互相关函数,计算结果为1,则匹配识别成功;捕获到导引信号后,进入锁定跟踪阶段,采用自适应扩展实时波门技术,根据导引信号匹配时刻及解析得到的编码参量设置时间波门,利用波门内截获的信号对目标进行持续跟踪[13]。

2.1 基于数字匹配滤波器的识别方法

数字匹配滤波器(digital matched filter,DMF)多用于扩频通信中对高速伪随机码的快速捕获,以实现信道同步[14-15]。基于数字匹配滤波器的编码识别方法具有搜索速度快、受干扰脉冲影响小的特点,在一个编码周期即可完成搜索。借鉴其解码原理,将其应用于激光制导LFSR状态码脉冲序列的解码识别过程中。

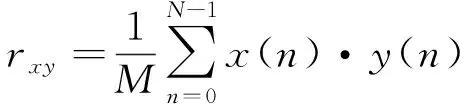

数字匹配滤波器主要由移位寄存器、与门组、多输入加法器和除法器组成,其基本结构如图2所示[14]。其中移位寄存器(shift register)A用于存储实时接收到的激光脉冲信号序列,移位寄存器B用于存储预设激光伪随机编码序列;与门组用于求取实时信号序列和预设编码序列的互相关性;然后将各与门的结果输入加法器及除法器中得到最终的互相关函数值rxy,计算公式如下:

(2)

Fig.2 Block diagram of digital matching filter

式中,x(n)为预设伪随机编码序列;y(n)为导引头接收到的实时脉冲信号序列;n为脉冲序列中离散化信号的编号;N为序列长度,即移位寄存器的长度;M为序列中存在的编码信号个数。若上式计算结果为rxy=1时,则表明匹配成功,捕获到导引信号。

为减小运算复杂度,对实时信号序列和预设编码序列进行抽样,考虑大气传输、编码晶体振荡器频率稳定度等因素,抽样窗口设定为脉冲时间间隔ΔTi±iδ的范围,对抽样序列计算互相关函数值如下:

(Ri∈[ΔTi-iδ,ΔTi+iδ])

(3)

式中,xR(n)为预设编码的抽样序列;yR(n)为实时信号的抽样序列;Ri为第i个抽样窗口范围;ΔTi为预设编码序列第i(i=1,2,…,M-1)个脉冲时间间隔;δ为脉冲到达时间不确定度。

2.2 基于扩展实时波门的锁定跟踪

2.2.1 时间波门技术原理 时间波门技术是激光解码锁定跟踪阶段常用的抗干扰手段,对特定频率的干扰脉冲,在保证制导信号进入波门的概率最大化前提下,波门宽度越窄,干扰脉冲进入波门的几率越小,则激光制导抗干扰能力越强。时间波门技术的原理为:根据预设编码序列和搜索识别阶段中导引信号匹配成功时刻,预测下一制导信号脉冲到达时刻,以该时刻为波门中心位置,以脉冲到达时间不确定度为最小波门半径设置波门,解码器只对波门内截获的信号进行处理[16]。时间波门技术主要分为固定波门和实时波门两类。

(4)

实时波门是以前一波门内检测到的制导脉冲时刻为时间同步点设置下一波门,波门宽度选取范围通常为5μs~20μs。以导引信号匹配成功时刻tm为第1个波门的时间同步点设置宽度为2δ的波门Tg,1′,然后以第1个波门内检测到的脉冲信号时刻tm+1为第2个波门的时间同步点设置宽度为2δ的波门Tg,2′,以此类推,以第k-1个波门内检测到的脉冲信号时刻tm+k-1为第k个波门的时间同步点设置宽度为2δ的波门Tg,k′,即:

(5)

固定波门采用一个时间同步点,具有累计误差,且波门宽度随时间成等差数列增长,导致随时间推移抗干扰性能下降,因此激光制导解码通常采用实时波门方案。在实时波门技术中,若采用首脉冲认定准则,当干扰脉冲P2′先于制导脉冲P2进入波门Tg,2,以干扰脉冲为时间同步点设置下一波门Tg,3,可能会导致下一制导脉冲P3落在实时波门之外,如图3所示。因此需对实时波门进行修正[18]。

Fig.3 Interference pulse’s effects on real-time gates

2.2.2 自适应扩展实时波门 针对实时波门受干扰脉冲影响出现漏检制导脉冲的情况,采用自适应扩展时间波门的方法避免存在干扰时导引头无法锁定跟踪目标。自适应扩展实时波门的基本原理如图4所示。常规波门宽度为2δ,不同情况下波门的设置准则为:(1)前一波门中只检测到一个脉冲信号Pk-1,则认定其为制导信号,以该脉冲时刻tm+k-1为同步点,在下一个编码脉冲时间间隔ΔTi+k处设置宽度为2δ的时间波门;(2)前一波门中检测到多个脉冲Pk,1,Pk,2,…Pk,l时,则分别以波门内的首脉冲时刻tm+k,1和末脉冲时刻tm+k,l为同步点,在下一个编码脉冲时间间隔ΔTi+k+1处设置两个宽度为2δ的时间波门,最终形成的波门宽度为2δ+ε,ε为前一波门中首末脉冲的时间差;(3)前一波门中未检测到脉冲信号时,则以最近一次检测到的脉冲时刻tm+k+1为同步点,在累计两个编码脉冲时间间隔ΔTi+k+2+ΔTi+k+3处设置宽度为4δ的时间波门。若连续两次在波门内未检测到脉冲信号,则回到搜索识别阶段重新进行匹配识别。

Fig.4 Adaptive extended real-time gate

3 基于FPGA的解码器设计

激光导引头信息处理单元多采用数字信号处理器(digital signal processor,DSP)结合FPGA及相关外设电路的架构,难以实现小型化设计,其中FPGA主要用于对接口电路和时序的控制,信号处理算法则在DSP中实现[19]。随着大规模集成电路设计和工艺水平的提高,FPGA的内部资源日益丰富,信号处理功能更强大,并且具有并行计算实时性好、便于二次开发灵活性好等特点,基于单片FPGA芯片即可完成整个信息处理单元的功能设计。

基于FPGA的解码器总体框架如图5所示。由复位模块(reset)、时钟分频模块(phase locked loop,PLL)、串口通信模块(universal asynchronous receiver/transmitter,UART)、数据缓存模块(shift register)、编码识别模块(code matching)及波门跟踪模块(time-gate tracking)组成。系统主芯片选用Altera公司的Cyclone III系列EP3C120F484I7型FPGA,采用Verilog HDL语言进行开发设计。外设电路包括EPCS64 FLASH存储器、60MHz晶振、RS232串口收发器、模数(analog-to-digital,A/D)转换器等。

Fig.5 Block diagram of the decoder system

复位模块根据系统运行时间标志位“time_flag”、输入信号无效标志位“data_invalid”及编码码字更新标志位“T_change”,对系统进行复位及初始化。时钟分频模块调用锁相环IP核“ALTPLL”,将晶振时钟分频得到1MHz的系统主时钟、串口通信时钟等,在1MHz主时钟下对输入的导引信号和随机干扰脉冲进行采样,即脉冲宽度为1μs。串口通信模块负责与综合控制器的通信,接收码型参量,并将其转换为脉冲时间间隔。数据缓存模块调用双口RAM IP核实现超长移位寄存器,满足基于数字匹配滤波器的识别算法的数据存储量需求。编码识别模块和波门跟踪模块首先根据码型参量和识别算法完成码型匹配,判断是否接收到导引信号,匹配成功后进入开波门流程。

3.1 数据缓存模块

数据缓存模块的设计有两个关键点:超大数据存储量和可变长度。

3.1.1 超长移位寄存器的设计 在1MHz主时钟下,以导引信号采用4位编码、基准时间间隔为50ms计算,至少需要缓存150000个数据。自行编写的超长移位寄存器可能出现时序紊乱的问题,故调用双口RAM IP核“RAM:2-PORT”,读写操作均在主时钟上升沿进行。

3.1.2 可变长度的实现 按照LFSR状态码编码方式,级数s=8时导引信号的脉冲时间间隔变化范围为±(0.1ms~12.7ms),串口通信模块接收到LFSR状态码编码码字参量后,解析出子序列脉冲间隔跳变数提供给数据缓存模块。设ki为8位脉冲间隔跳变数,其最高位为符号位,其余7位为跳变的绝对值;基准时间间隔ΔT0=50000,则子序列脉冲时间间隔为:

(6)

然后由ΔTi来控制相应随机存取存储器(random access memory,RAM)的读写地址范围,每个clk上升沿读写地址+1,当读写地址等于ΔTi时,将读写地址清零。

3.1.3 数据传输方式 采用“数据链”的方式实现移位寄存器中的数据传输,整个移位寄存器由随机存取存储器(random access memory,RAM)和window拼接而成,数据链中数据的传输方式如图6所示。将window 0~window 3中数据输出,即完成(3)式中对脉冲信号序列的抽样。

Fig.6 Data link transmission method

3.2 编码识别及波门跟踪模块

编码识别及波门跟踪模块使用状态机来实现,状态机分为5个状态:(1)初始状态(s0);(2)编码识别状态(s1);(3)正常波门状态(s2);(4)扩展波门状态(s3);(5)两倍波门状态(s4)。状态机转换具体流程如图7所示。

初始状态(s0):等待移位寄存器中数据存满,则进入编码识别状态。

编码识别状态(s1):检测抽样窗口window 0~window 3中是否同时有脉冲,即对每个窗口中的数据按位求“或”运算,再将“或”运算的结果求“与”,最终结果为1则表示检测到导引信号,将解码标志位flag_decode置高,并用计数器timer 0记录匹配成功时刻,进入正常波门状态,否则继续编码识别状态。

正常波门状态(s2):以导引信号匹配成功时刻timer 0为同步点,在其后[ΔTi+k-δ,ΔTi+k+δ]时刻处将波门信号gate置高,波门宽度为5μs;首先判断波门内是否检测到脉冲信号,若未检测到脉冲,则进入两倍波门状态(s4);若检测到脉冲,则将脉冲标志位flag_pulse置高,进一步判断脉冲个数:若检测到脉冲个数为1,则用计数器timer 1记录脉冲时刻,作为下一波门同步点,继续正常波门状态;若检测到脉冲个数大于1,则分别用timer 1和timer 2记录首、末脉冲时刻,转至扩宽波门状态(s3)。

Fig.7 Flow chart of the state machine transition

扩宽波门状态(s3):以上一波门内记录的首脉冲时刻timer 1为同步点,在其后[ΔTi+k+1-δ,ΔTi+k+1+δ+ε]时刻处将波门信号gate置高,波门宽度为(5+ε)μs。

两倍波门状态(s4):以最近一次记录的脉冲时刻timer 1为同步点,在其后[ΔTi+k+ΔTi+k+1-2δ,ΔTi+k+ΔTi+k+1+2δ]时刻处将波门信号gate置高,波门宽度为9μs;若在波门内检测到目标信号脉冲,则将flag_pulse置高并记录脉冲时刻,返回正常波门状态;否则返回编码识别状态(s1),对编码重新识别。

4 系统测试结果

4.1 仿真测试结果

在ModelSim软件中进行仿真测试,编写Test bench测试文件作为激励输入,对解码器功能进行验证,设定ΔT1=500,ΔT2=700,ΔT3=400,仿真测试结果如图8所示。图8a为制导信号编码匹配成功时刻波形,图8b为下一脉冲时间间隔开波门时刻波形。数字匹配滤波器基于并行运算对脉冲序列进行识别,在接收到一组编码序列的当前周期即完成一次匹配滤波运算,且每接收到一个新的输入信号进行一次匹配运算,即最小在1个周期内即可实现码型参量解算,解码实时性较好。而采用基于自相关函数+序列搜索法、基于滑动匹配相关法等串行方法进行解码,至少需要接收到2~4个周期脉冲序列后才能有效解码。

Fig.8 Simulation test results in ModelSim

4.2 系统实测结果

利用信号发生器产生宽度1μs、周期50ms±(0.1ms~10ms)的制导脉冲和100kHz的高重频干扰脉冲信号作为系统输入信号,采用实时信号分析工具SignalTap Ⅱ对FPGA的输入输出管脚及任意内部信号进行逻辑分析,信号采样时钟设置为2MHz,测试结果如图9所示。由参考文献[13]中的干扰概率计算方法可知,波门宽度为10μs且采用首脉冲检测准则时,100kHz的高重频干扰脉冲对制导信号干扰成功的概率为100%。而本文中解码器的正常波门宽度为5μs,小于高重频干扰信号周期10μs,且采用自适应扩展波门技术,将干扰成功概率降低至50%,进一步提高了导引头的抗干扰性能。

Fig.9 Real-time test results in SignalTap Ⅱ

5 结 论

LFSR状态码在单次制导过程中可实现脉冲时间间隔不重复,使得敌方难以精确识别与有效对抗,采用LFSR状态编码可有效提高激光导引头抗干扰性能。针对激光制导LFSR状态编码信号,采用基于数字匹配滤波的识别方法进行编码识别,在一组编码周期内即可完成码型匹配,相比于滑动匹配相关等方法解码时间短。且采用抽样窗口对脉冲序列抽样后再计算互相关函数值,减少了运算复杂度。采用自适应扩展实时波门对目标锁定跟踪,避免了干扰脉冲超前于制导脉冲信号进入波门造成漏检的情况,提高了解码器的抗干扰能力。常规波门宽度为5μs,可有效对抗100kHz的高重频脉冲干扰。解码器硬件方案采用基于单片FPGA的信息处理系统实现,具有体积小、成本低、开发周期短和实时性强等优点,可满足小型化半主动激光导引头应用需求。