S波段四通道小型化数字阵列平台设计

中国电子科技集团公司第十研究所 荀海恩

数字阵列作为数字波束形成技术的硬件平台,要求具有低尺寸、重量和功耗等优点。本文实现了一种S波段四通道的数字阵列通用平台。该平台收发组件基于零中频架构的集成宽带射频收发器;天线采用微带形式;发射链路引入数字预失真技术,IMD3指标改善了30dB。该数字阵列平台具有集成化程度高,高灵活性,通用性强,小型化,低功耗,等优点。

高性能数字器件的出现,极大地推动了数字阵列和数字波束形成(DBF)技术的应用。因数字阵列具有高灵活度、高精度、快速扫描、低副瓣等优点,广泛应用于航空航天、军事通信、电子战以及移动通信等诸多领域。因此,数字阵列成为国内外研究的热点。

本文设计了一种S波段四通道的数字阵列通用平台。作为数字阵列的核心,其收发组件采用零中频架构的集成宽带射频收发器,实现了从数字域到射频域的转换,不仅缩小了系统尺寸,简化了系统架构,降低了系统功耗,而且极大地提高了系统灵活性。

1 系统集成化设计

数字阵列的设计按照自顶向下的思想,根据系统指标以及集成化、小型化的需求,按照功能划分为数字收发组件、射频放大滤波以及阵列天线三个主要模块。

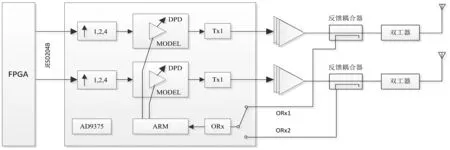

数字收发组件是整个数字阵列的核心,其性能指标和尺寸决定了整个数字阵列的优劣,其原理框图见图1。从图1所示可以看出,数字收发组件包含了2个集成宽带射频收发器、ARM、FPFA、满足JESD204B协议的专用时钟芯片、电源变换和上电时序控制网络以及外部接口等。

图1 数字收发组件原理框图

集成收发器和FPGA之间的数据接口为高速串行接口JESD204B,相比于传统的LVDS和LVCOMS等并行接口,其接口数量大为减少,配置更加灵活。相比于传统的中频采样架构,该方案省去了中频滤波器、镜像抑制滤波器以及变频器等分立器件,极大地缩小了系统尺寸。

2 数字预失真

射频功率放大器不仅是发射链路中功率消耗最大的器件,而且其非线性还会影响系统信号传输的质量。为了克服功率放大器效率和线性度之间的矛盾,本文利用数字预失真技术在保持系统高效的同时,还可以改善其线性度指标。

在本设计中,利用AD9375中集成的DPD内核,完成发射链路末级射频功率放大器的线性化校准。其实现方案见图2所示。与传统数字预失真方案相比,该方案不仅减少了集成接口带宽,将SERDES的线路数量减少了50%,缩小了系统的外形尺寸,而且DPD功耗低于100mW,是基于FPGA方案的十分之一。

图2 基于AD9375的预失真方案

3 数字化设计

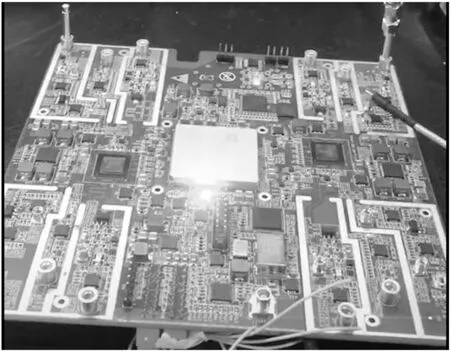

作为整个收发系统的核心,数字收发组件的设计直接影响了整个系统的性能。由于该数字收发组件的印制板上包含了高速数字信号、射频信号、电源信号等各种信号,因此印制板设计时,必须考虑不同信号域的隔离以及电磁兼容问题。本文在设计时将电路中的关键信号和功能进行优先级划分。其中,最重要的是射频线和JESD204B的阻抗匹配和隔离度;其次为芯片的电源域的划分;最后为控制线路等线路的走线设计。数字收发组件的实物图见图3所示。

图3 数字收发组件实物图

4 实物测试

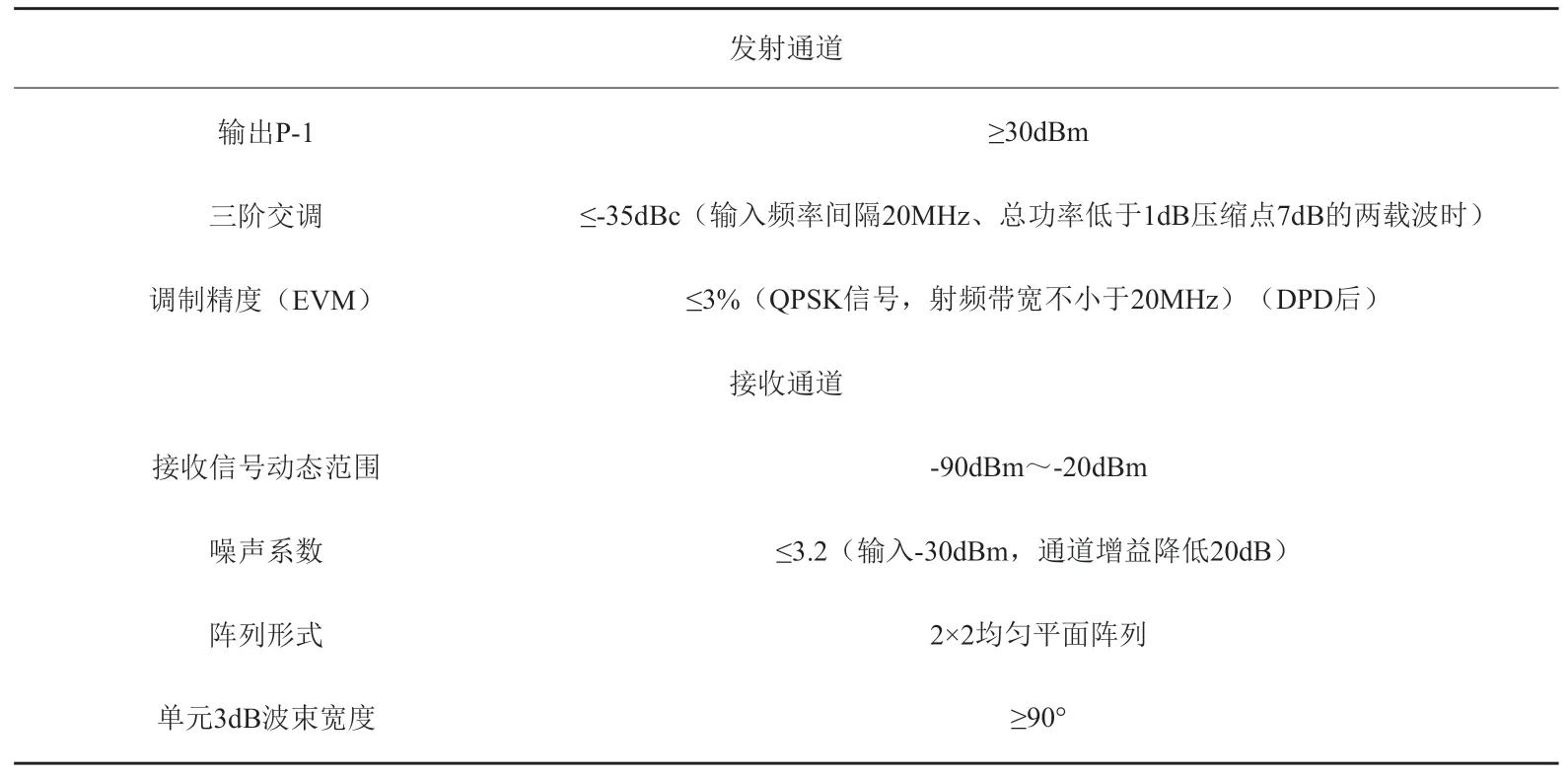

本文S波段四通道小型化数字阵列通用平台关键指标的测试结果见表1所示。

表1 关键指标测试结果

本文设计了一种S波段四通道的数字阵列通用平台。收发组件采用零中频架构的集成宽带射频收发器,阵列天线采用微带平板设计,相比于传统方案,尺寸减小40%以上,功耗降低30%以上,同时具有集成度高,通用性强等优点。此外,该设计针对发射链路末级射频功率放大器采用了数字预失真技术,且数字预失真在射频集成收发器内部实现,在功耗和性能方面相较于传统DPD方案都有了极大地提高。