一种CMOS集成基准电压源的电路设计

贵州电子信息职业技术学院 舒 梅

基准电压源在模拟及数、模混合集成电路设计中,是非常重要的电路模块之一,这类器件的发展对基准的噪声、启动速度、电源纹波抑制比(PSRR)等提出了非常高的要求。通过巧妙设计的带隙基准电压以其与工艺、电源电压、温度变化几乎无关的特性,广泛应用在DC-DC转换器、发射电路、LDO线性稳压器及高精度A/D和D/A转换器等多种集成电路中。本文在传统的带隙基准电路基础上,对基准电压源提出了一些具体要求及相应的设计指标,最终完成了一种以CMOS为主的集成基准电压源的电路设计。

1 设计思路

本设计是以传统的带隙基准电路为基础,辅以相关的启动电路、电压箝位电路、输出缓冲电路来实现高精度、低温度系数、强带负载能力的设计目的。

由于基准电路存在两个平衡点,一个是零点,另一个是正常平衡点。为了避免上电后电路工作在零点,需要给它设计一个启动电路,保证电路在上电后工作在正常平衡点。在核心带隙基准电路中基准电压的产生是靠电流镜中的镜像电流流经电阻和二极管连接的PNP管形成的,这样一来,电流镜的失配就会对输出基准的精度产生很大的影响,在本设计中的电压箝位电路就是为了降低电流镜的失配。在传统带隙基准电路中,基准电压是由镜像电流流经一个电阻产生的电压叠加在一个VBE上形成的,这样的基准输岀电阻比较高,在使用中需要在基准和后续电路之间加一个缓冲器,这样就限制了基准源使用的灵活性。所以在本设计中为了实现基准输出带负载能力强的指标,在带隙基准的输出级加了一个单位增益的输出缓冲级,但是这样会使电路的PSRR降低。

通过以上的分析,得出具体的基准构架如图1所示。

图1 基准源电压的基本构架

2 子电路的设计

本设计中包括基准核心产生电路、启动电路、电压钳位电路和输出缓冲电路。以下对它们进行逐一介绍。

2.1 基准核心产生电路

我们都知道在集成电路中,与电源电压无关的常用标准有如下的三类:

(1)由NPN管反向击穿BE结构成的齐纳二极管的击穿电压VZ,VZ= 6~9V,它的温度系数为:

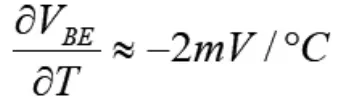

(2)BE结二极管的正向压降VBE,VBE= 0.6~0.8V,它通过对温度求导,其温度系数为:

(3)等效热电压Vt,Vt= 26mV,其温度系数为:

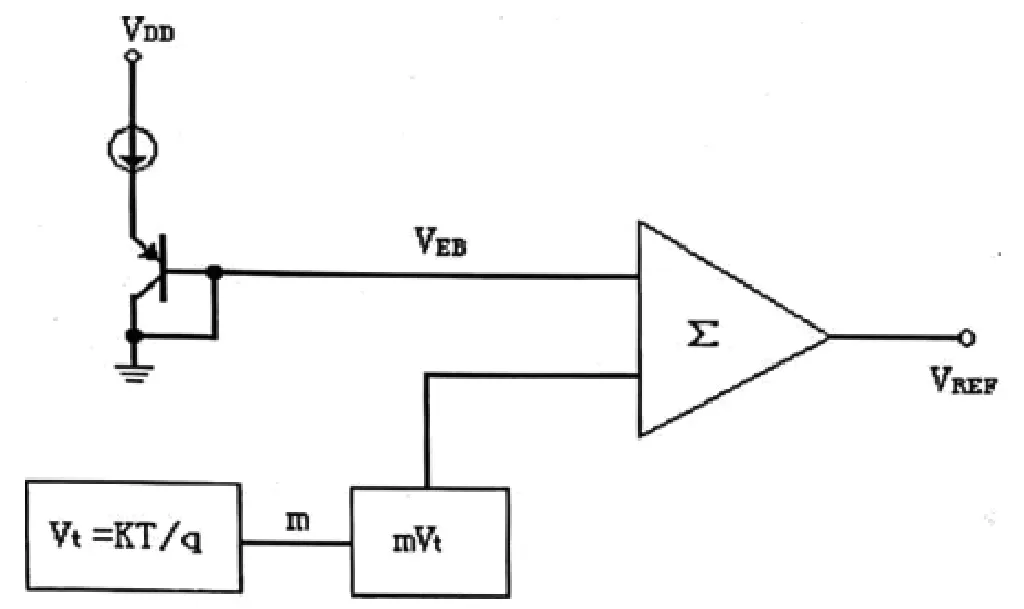

图2 带隙基准电压源原理框图

由此可见,这三种标准电压的温度系数有正也有负。利用VZ、Vt和VBE的温度系数符号正好相反,以及集成电路中元器件之间匹配和温度跟踪较好的特点,将这三种标准电压进行不同的组合,可以得到不同的对电源电压及温度不敏感的基准电压。

图2所示是带隙基准电压源的原理框图,从图中可以看出,基准电压VREF由具有负温度系数(约为-2mV/℃)的E-B结电压VEB和具有正温度系数的热电压Vt通过线性叠加,从而实现了室温下具有零温度系数的基准输岀。从框图中可以看出VREF=VEB+mVt,与电源电压无关。

图3所示为带隙基准核心电路的具体实现电路,下面进行简单的说明。图中由M1、M2、M3组成的镜像电流源,使流过三个管的电流相等,均为I;由M4、M5组成的电压钳制电路,使A、B两点的电压能够保持一致。电压钳制电路和镜像电流源在一起组成了一个PTAT源,通过用它的正温度系数去补偿P-N结的负温度系数,得到了基本上不随温度变化的基准电压。

经过分析计算得出在-20℃~100℃的温度范围内,基准电压VREF的变化过程为:

图3 带隙基准核心电路

1.256128227V~1.2568V~1.255377591V,其最大偏差为0.001422409V,这个值是很小的,说明该基准电压源的温度特性比较好。

2.2 启动隔离电路

由于前面的核心电路在电源接通以后,所有的晶体管都有可能传输零电流,那么该电路就可能会无限期的保持中断,将导致整个电路无法正常工作。为了避免电路上电后可能会工作在平衡零点,就需要用一个启动电路来保证上电后电路能进入正常工作状态。在电路达到正常工作平衡点后,需要有一条支路把启动电路和基准核心电路隔离开,避免因为启动电路输出点对基准核心电路中的电压钳制作用而破坏电路的功能,所以这部分电路叫做启动隔离电路。

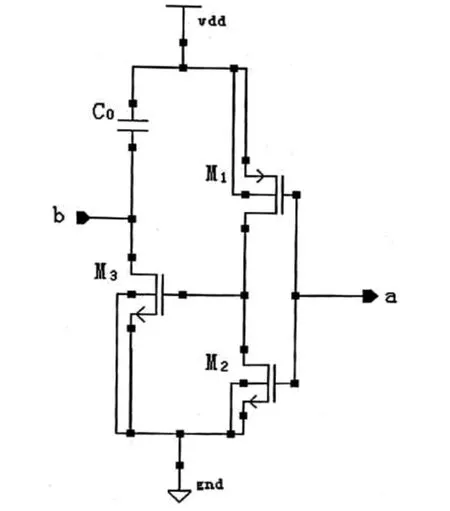

图4 启动隔离电路

本设计中的启动隔离电路如图4所示,电路中a点电压取自带隙核心电路中电阻R1的上端,b点输出电压接到电流镜的栅级。电路刚上电的瞬间,a点为低电位,经过M1和M2组成的反相器后得到一高电平驱动M3管导通,电源开始对电容C0充电,b点电位开始上升,驱动带隙核心电路中的电流镜支路,从而驱使整个电路进入正常工作状态。当电路达到稳态后,a点取样来的电压为高电平,经反相器后使M3管关断,因为这时电路已进入稳定工作状态,电容C0对直流电源vdd呈现为断路,b点和启动电路隔离开来,达到了启动隔离的作用。

这一启动隔离电路的优点是原理简单,逻辑思路明确。其缺点是电容C0的存在会使电路的启动时间受到限制,并且在电路中引入电容会使芯片电路的版图面积增加。

2.3 电压箝位电路

在前面介绍的带隙基准核心电路中,电流镜中的电压箝位是靠由M4、M5管构成的NMOS镜像电流源实现的,这是利用镜像电流源能降低对电源电压的敏感度原理来实现的。但是这个电压箝位电路过于简单,不能很好的钳制两条电流镜支路上的电压,从而会引起电流镜的失配。

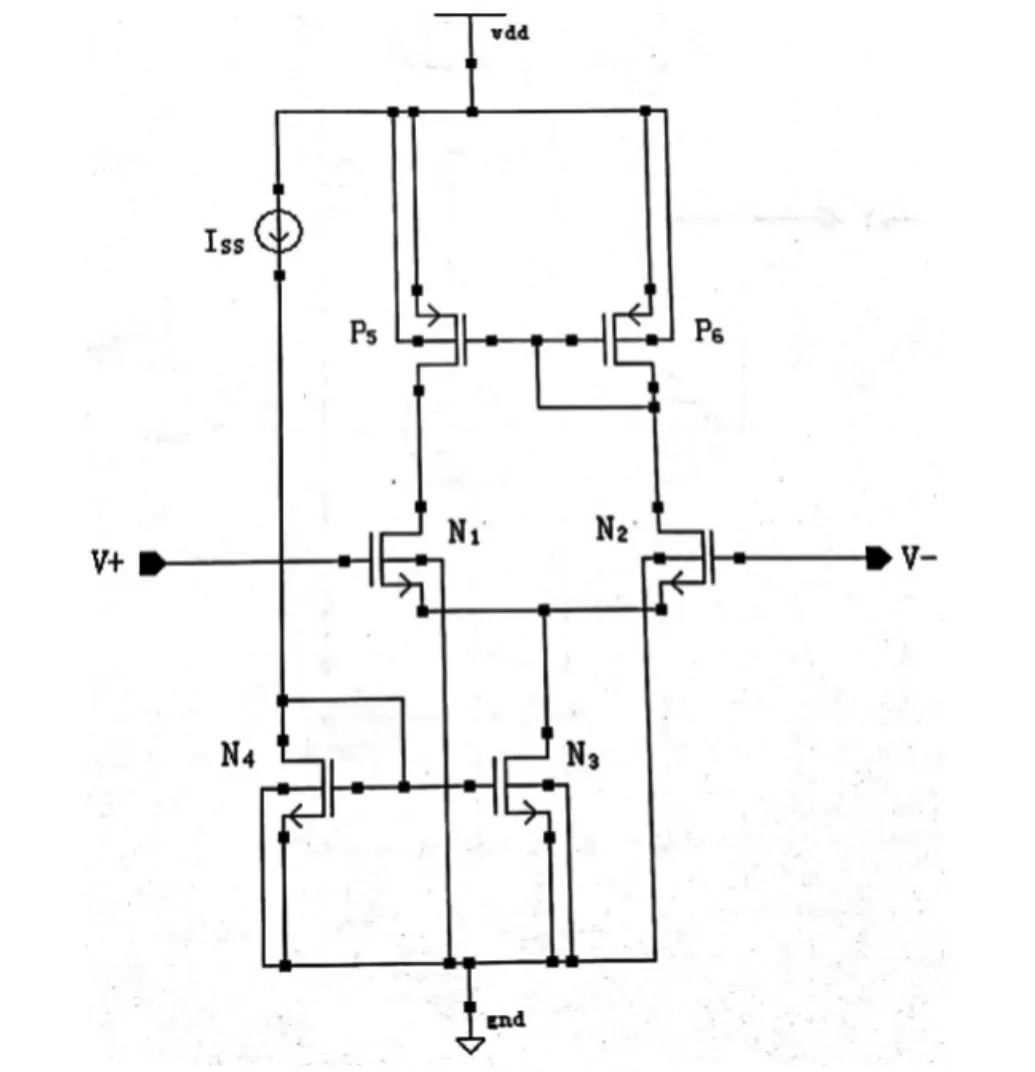

我们知道,运算放大器的两个输入端之间只存在很小的失调电压,它们之间可以看作是虚短路的,这样就可将两点的电压钳制的很好。鉴于本设计对精度的要求不是特别高,该电压钳制电路用差分放大器就能达到指标要求。如图5所示,P5、P6构成的PMOS镜像电流源为差分放大器的有源负载,N3、N4构成的NMOS镜像电流源为差分对提供偏置电流,偏置电流Iss由带隙基准核心电路中的电流镜镜像而来。差分对的输出取自N1管的漏级,该输出接到各条电流镜支路中PMOS管的栅级,形成一个反馈回路。这样可改善普通电流镜电路中由于其中一条支路的PMOS器件栅源互连所带来的电流失配。

图5 电压箝位电路

图6 单位增益的输出缓冲级

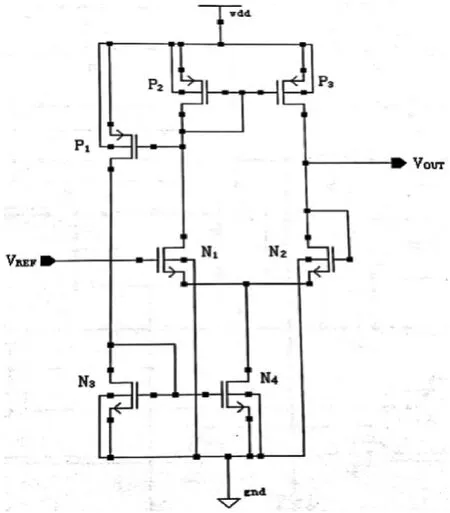

2.4 输出缓冲级

如图6所示,本设计中的输出缓冲级采用的是一个单位增益的差分放大器,这级电路具有正的温度系数,要得到低温度系数的输岀电压,需要调节前级电路的温度系数来补偿这一正温度系数。从图6中可以看出,加了这一级后,当电路达到稳态工作时,各MOS管均工作在饱和状态,输出电阻很小,电路的输岀驱动能力得到了提高。

结语:总的来说,本设计基本完成了对整个“CMOS集成基准电压源”的设计,若在后期的工作中对设计做进一步的完善,则所得到的芯片将基本上都具有CMOS集成基准电压源所具有的“高精度、低温度系数、强输出驱动能力”等功能。由于受制造工艺的影响,芯片的性能可能和设计所要求的技术指标略有偏差。