水下环形组网网络中时延测量及调整策略

宋文生 王琨 曹伟军 付传宝

摘要:针对海洋探测、安防、监控等领域多节点水声信号采集及同步传输需求,使用XilinxSpartan6FPGA采用伪随机序列和数字相关技术对各个节点的传输时延精确测量,在岸上信号处理单元对测量结果汇总、分析,并根据测量结果对信号进行时延调整,实现所有节点信号水下采集信号的同步输出。根据FPGA的处理能力,其测量及调整精度可达3ns,经调整后的多个节点之间的信号输出时延误差满足系统后续信号处理要求。

关键词:级联组网;m序列;数字相关技术;环形组网;时延测量;时延调整

随着水下探测、监控、安防需求的进一步扩大,各国水下探测的距离、分辨率要求不断提升,对水声信号采集的可靠性、实时性、一致性要求也越来越高,本文针对水下信号采集的新需求,提出采用双环自愈环形组网方式提高系统可靠性,同时通过采用m序列、数字相关技术及先进先出(FIFO)存储器实现系统时延参数的实时调整,解决了环形网络中由于可变传输路由引起的信号传输时延不固定的问题,实现了系统中所有节点信号的同步输出。

1系统架设

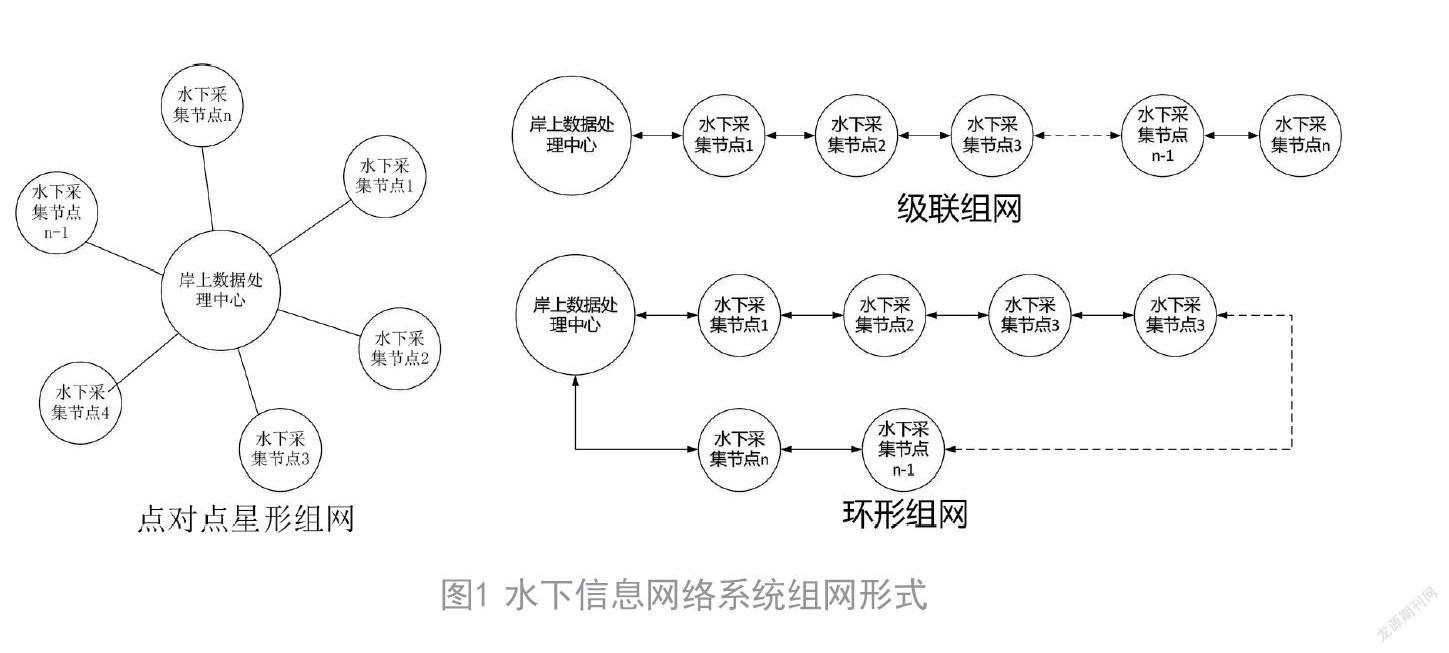

根据探测精度及系统实时性的要求,水下监测、采集系统一般由1个岸上数据处理中心加n个水下信号监测、采集节点组成。水下采集节点的数量与水下监测系统的范围及精度要求有关;水下采集节点与岸上信号处理单元的组网方式通常有如下三种:点对点星形/并联组网[1]、级联组网和环形组网。各种组网方式如图1所示。

在点对点星形组网模式下,水下节点与岸上节点之间采用点对点的直接连接方式,其数据通过水下与岸上节点之间独立、专用的数据通道传输,系统架设完成后其传输时延为1个固定值;级联组网模式下,各个水下节点采用数据逐级级联上传的方式传输,在系统架设完成后其信传输链路固定,因此其传输时延也为1个固定值。在这2种组网方式下,信号路径、时延固定,但是点对点组网方式一旦监测范围扩大、节点增加,其架设成本成线性增加;而级联组网形式由于采用逐级上传,水下任意1个节点故障都会导致后续所有节点数据无法正常上传。

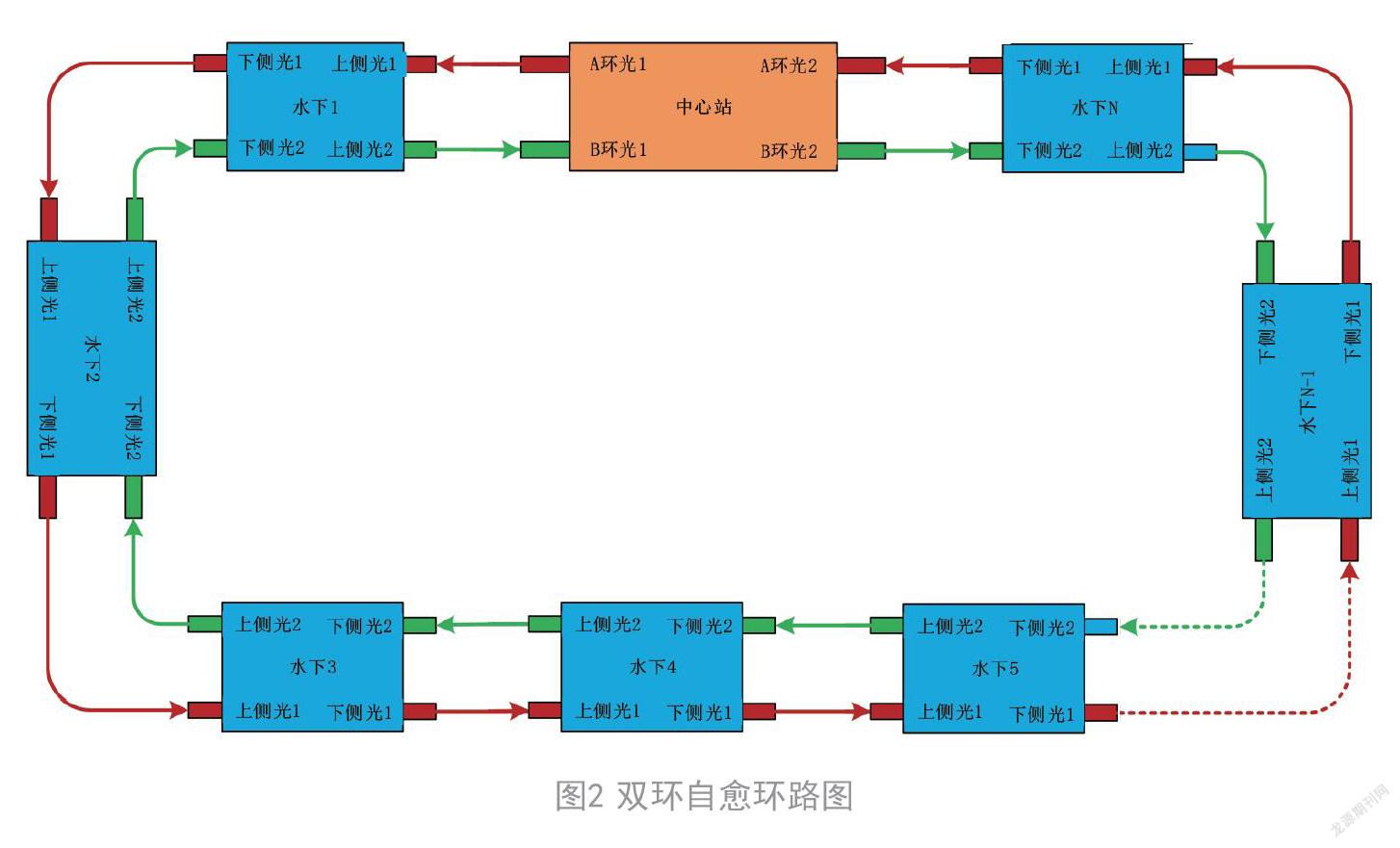

环形组网也是采用水下节点逐级上传的方式,与级联组网方式的不同之处在于:级联组网水下末端节点N只与N-1个水下节点相连,而环形组网方式末端节点N一端与N-1个水下节点相连,另一端与岸上节点相连,岸上节点、N个水下节点逐级首尾相连形成1个闭合的数据传输环路,只需要1芯首尾互相连接光纤,在采用波分复用的情况下就可以搭建顺时针和逆时针方向两个完整的双环自愈数据传输环路[2],如图2所示。

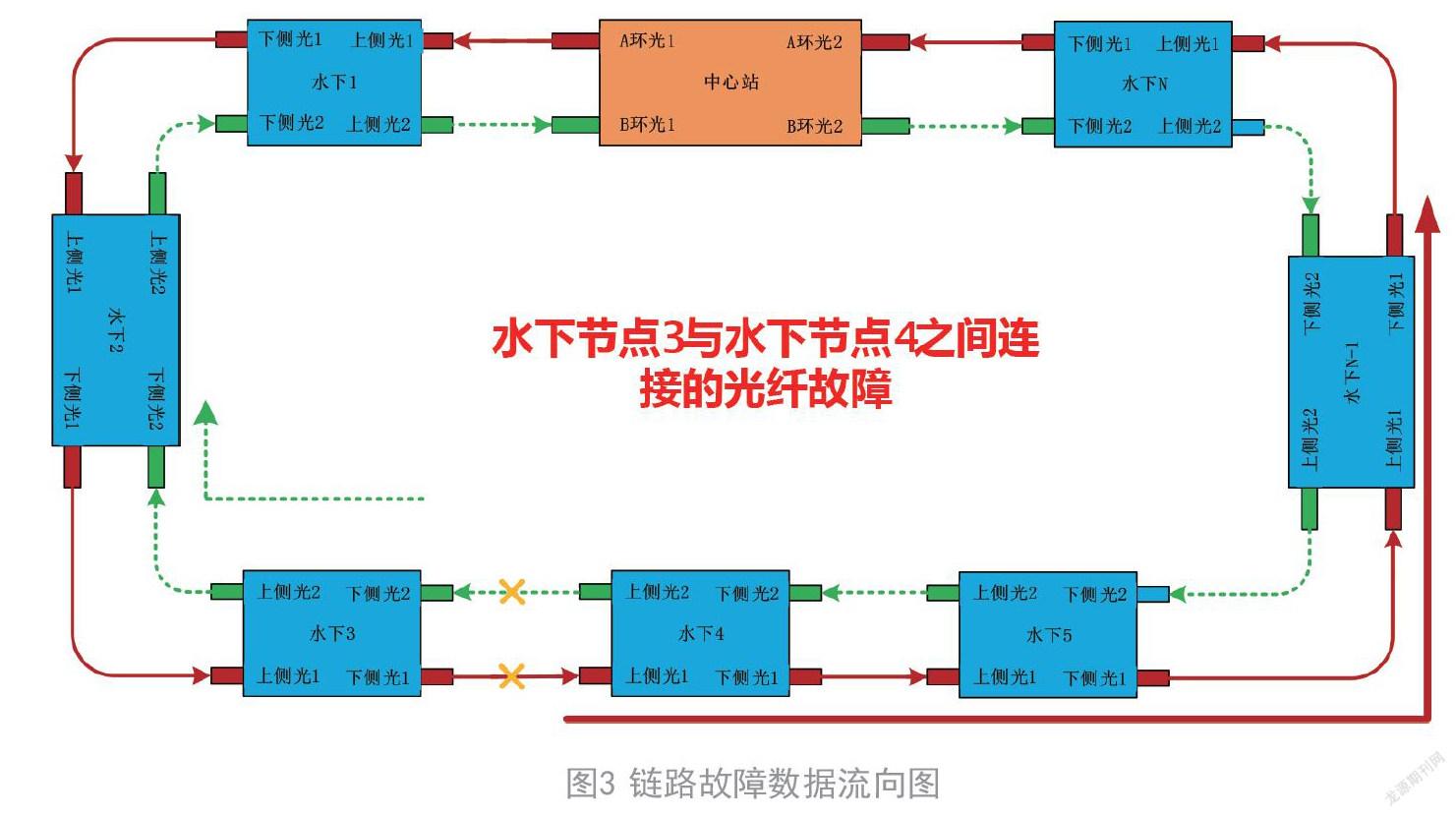

由于数据可以沿顺时针、逆时针2个方式传输,采用环形组网的方式时,1个节点故障其后续节点数据还能正常逐级上传。图3给出了集中光纤链路故障、节点故障时数据传输链路图。

如图3所示,当水下节点3和水下节点4之间的光纤出现故障,如果采用的是单纯的级联组网方式,此时节点3之后的所有节点数据都无法正常传输,但是在环形组网方式下,由于具有顺时针和逆时针2个环路,此时节点3之前(含节点3)的所有节点数据可以通过顺时针(虚线)方向将数据上传到岸上节点。其可靠性较单级联方式有很大的高,但是在这种方式下,由于每次路径不一致,从而导致每次数据传输的时延不一致,此时为了使各个数据通道的输出时延保持一致,势必需要在岸上数据处理中心增加时延调整模块,实现对各通道数据时延的实时调整。

2时延调整实现方案

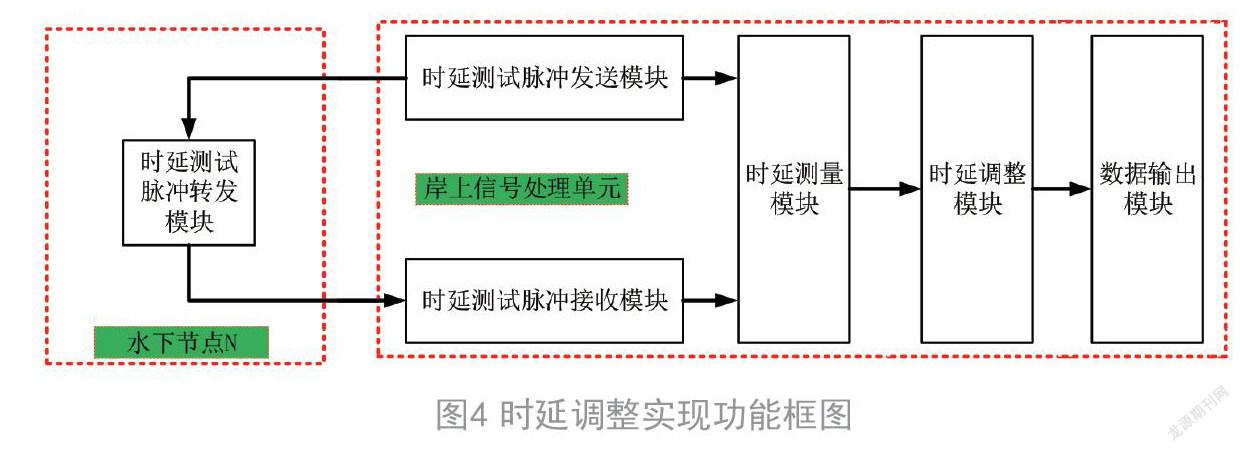

系统时延调整实现的功能框图如图4所示。

时延调整系统由时延测试脉冲发射模块、时延测试脉冲转发模块、时延测试脉冲接收模块、时延测量模块、时延调整模块及数据输出模块组成,各功能模块功能描述如下。

●时延测试脉冲发送模块:根据实际需要产生时延测试脉冲信号,经岸上与水下节点的信号传输通道传输到水下的N个节点,该信号也作为时延测量模块进行时延测量的基准信号。

●时延测试脉冲转发模块:

该模位于各个水下节点,主要功能是完成岸上传来的时延测试脉冲的转发,经由与下发路径相同的链路回传给岸上信号处理单元。

●时延测试脉冲接收模块:接收各个水下节点回传的时延测试脉冲信号,输出给时延测量模块进行时延测量。

●时延测量模块:以时延测试脉冲发送模块产生的时延测试脉冲信号作为基准信号,测试时延脉冲接收模块输入的脉冲信号与该信号的时延差,作为时延测试脉冲信号过1个下发及上传数据回路的传输时延。

●时延调整模块:根据时延测量模式的各个水下节点的传输时延,对该时延数据进行分析处理、延时调整,将各个水下节点调整为同步输出。

3节点时延分析及测量

3.1水下节点时延分析

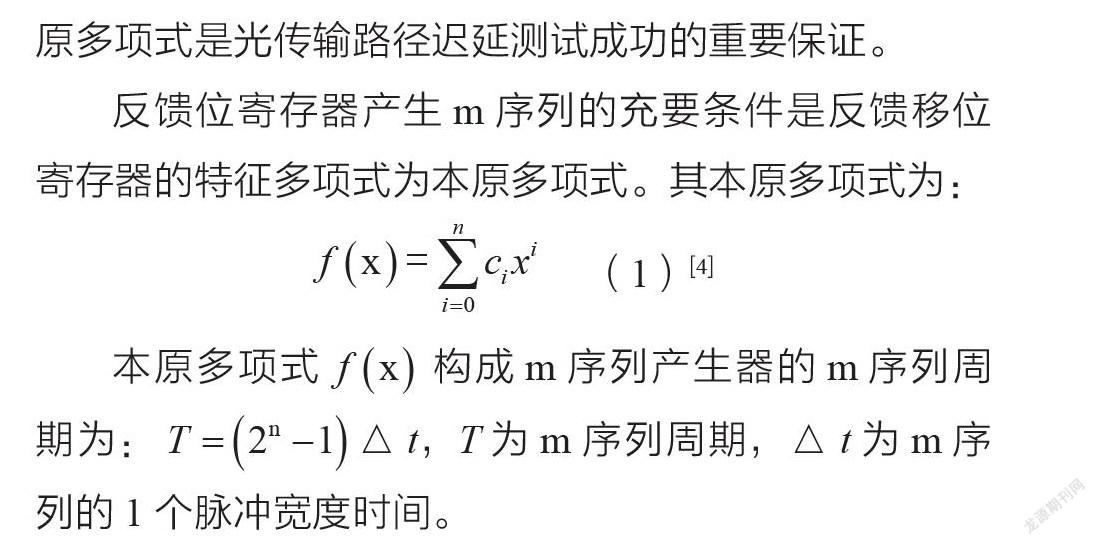

水下各个节点线路传输迟延时间成如图5所示,每个节点模拟信号线路传输迟延间包括由D/A转换迟延、输出接口电路迟ΔT1、光环网传输线路迟ΔT2、输入接口路迟延、和A/D转换迟延ΔT。系统中每个子站信号3的ΔT、ΔT均固定且相同,各子站的传输迟延差由ΔT132不同产生。只要测试出每个子站点的路由迟延ΔT2,即可计算出各子站点的传输迟延时间差,由传输迟延时间差计算出各子站点的传输延周期,并依据传输迟延周期對各子站点信号进行同步处理。

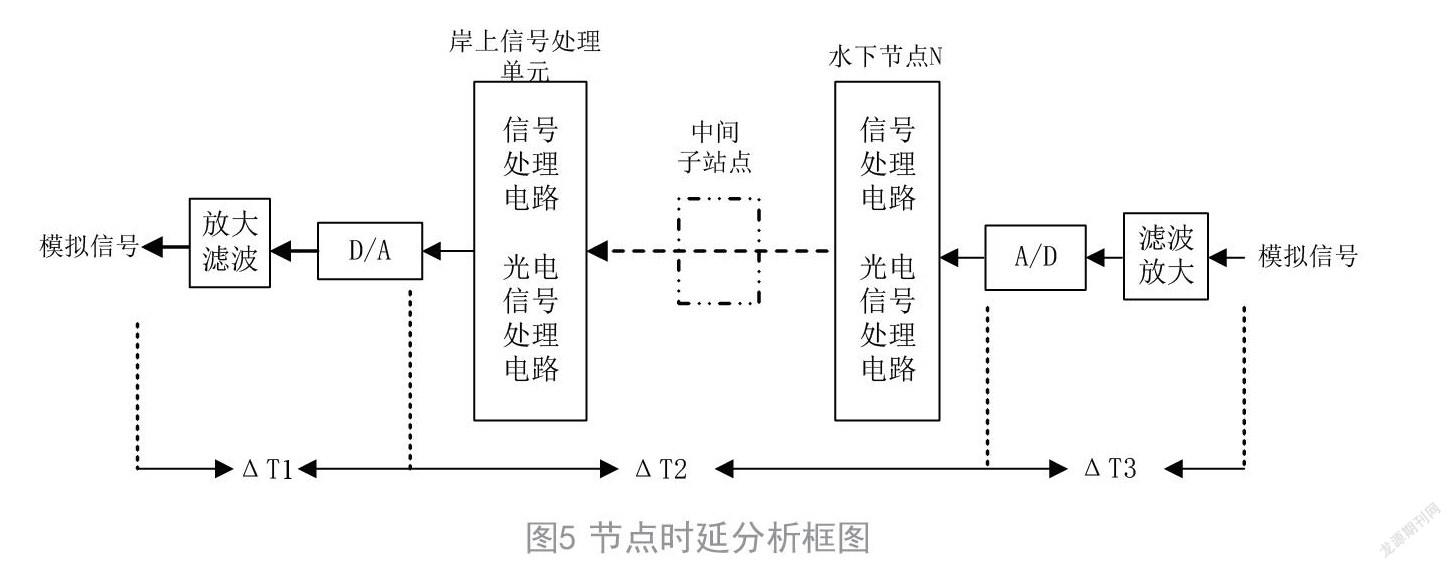

3.2基于伪随机序列的环路传输迟延测试

水下各节点到岸上信号处理单元不同路由迟延测试实现原框图如图6所示。在岸上信号处元产生1个长周期伪随机序列时延测试脉冲信号,在进行节点时延测试时,用该脉冲信号替代岸上信号处理单元的空闲数据进行输至子站点在信号处理后经所选测试路由传输至子站点,子站点解出时延测试脉冲信号后回环,替代子站点的A/D数据进行数据打包,在信号处理后经过所选测试路由传输至岸上信号处理单元。在岸上信号处理单元恢复出回环的时延测试脉冲信号,并与岸上信号处理单元提供的时延测试脉冲信号基号进行比较,计算出子站点到岸上信号处理单元的传输迟延时间(回环迟延时间除2),保存测试结果。根据各自的路由迟延测试结果,各站点的信号传输给岸上信号处理单元。

在进行时延测试时,产生的时延测试脉冲信号采用伪随机序列(即m序列[3])。构成m序列产生器的本原多项式选择对测量的距离有关键影响。如果路径的迟延时间超过序列的1个循环周期时间,则可能出现测试结果小于实际迟延时间,得出错误结论。m序列的1个循环周期时间太长,则m序列产生器和数字相关器设计复杂。因此选择合适的本原多项式是光传输路径迟延测试成功的重要保证。

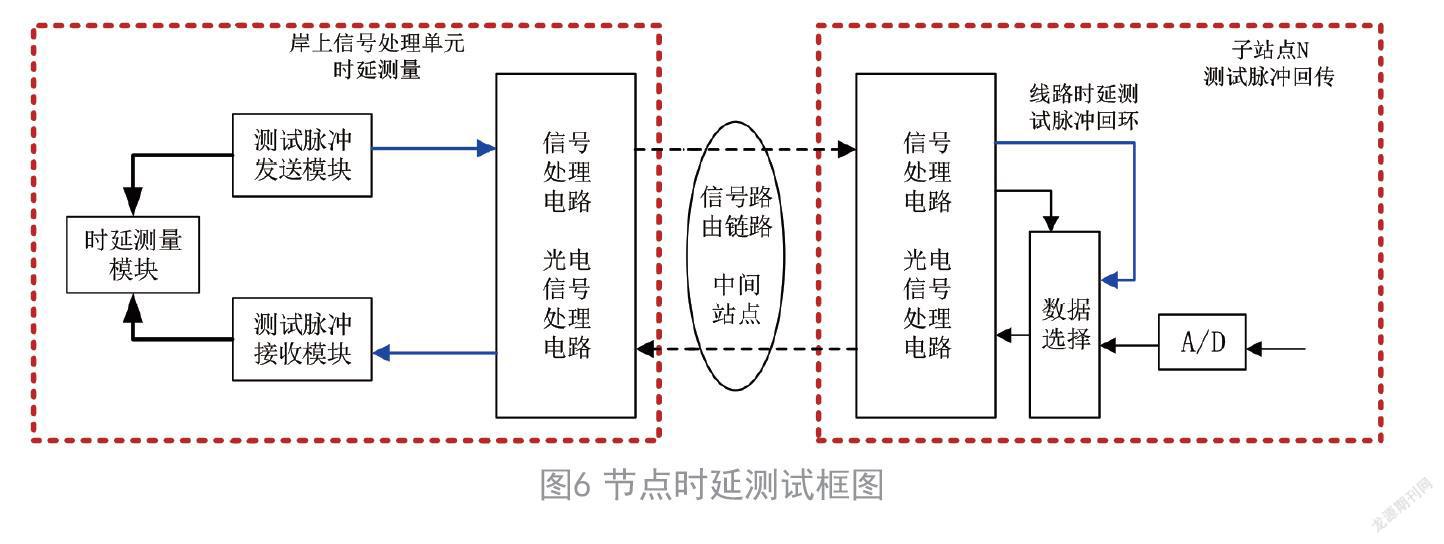

反馈位寄存器产生m序列的充要条件是反馈移位寄存器的特征多项式为本原多项式。其本原多项式为:

本原多项式f(x)构成m序列产生器的m序列周期为:T=(2n1)△−t,T为m序列周期,△t为m序列的1个脉冲宽度时间。

假设环网最长路由为20个节点,环网光传输路径小于等于50km,则m序列从本端传输到远端再回传至本端最长传输迟延时间约为:

站点信号处理时间×20+光路传输迟延时间

每个子站点信号处理时间为5个A/D采样周期(fs=2Mbit/s),即2.5μs。光纤传输迟延5ns/m。

环网最长路由迟延时间为:

△T=2.5×20+(5ns/m×50000m)/1000=300μs

m序列周期T应大于300μs。依据T>△T(T为序列周期,△T为环路延迟时间),T=(2n-1)△t(n为m序列长度,△t为m序列脉冲宽度),△t=0.1μ(s水声信号采集频率为2Mbit/s,随机码宽度为0.1μs,换算到频域为10Mbit/s,远大于信号采样频率,满足使用要求),n取整,计算出n=12(T=409μs),即m序列的1个脉冲宽度为0.1μs,系统迟延测试精度为1个伪随机码脉冲宽度,测试环网传输迟延时,选用f(x)=x12+x6+x4+x+1本原多项式构成m序列产生器。

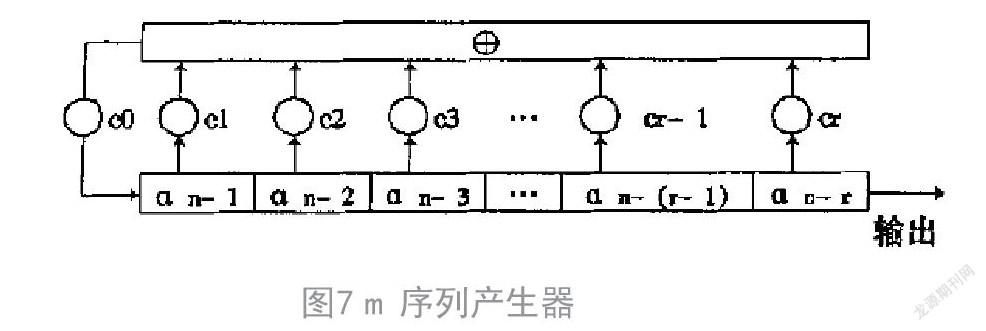

本原多项式选定后可利用FPGA丰富的可编程资源,依据反馈函数和连接形式构建12位移位寄存器加异或反馈网络的m序列产生器其结构如图7所示。

将水下节点回传测试冲信号输入到时延量模块,对时延测量模块内部与测试脉冲基准信号采用数字相关技术进行时延测量。

多位数字相关器[5]可以由一位相关器级联构成。N位数字相关器的运算通常可以分解为以下2个步骤:1对应位进行异或运算,得到N个1位相关运算结果;2统计N位相关运算结果中0或1的数目,得到N位数字中相同位和不同位的数目。

数字相关器[5]的设计一般考虑采用串行输入检测方式,即在N(N为m序列的长度)个时钟周期内依次对两路串行输入信号A、B进行异或运算,并统计数据位相同个数。

采用系统时钟对时延测试脉冲信号基准信号与回传的信号进行数字相关运算,当不同时在同1个时钟下对时延测试脉冲基准信号移位,移位后再次运算,直至两个信号完全相关,此时的移位时延即为链路时延时间,计算方法如下:

△τ=ty×ny

△τ为链路时延时间,ty为移位时钟,ny为移位次数。ty的选择与系统的同步精度要求有关,一般选择与m序列码元宽度一致。

4时延调整

通过采用m序列及数字相关技术,得到每个水下节点的实时传输时延,需要统计分析所有节点的时延参数,综合该参数从系统上考虑,调整时延使所有节信号同步输出。时延调整在岸上中心理单元内部用FPGA完成。

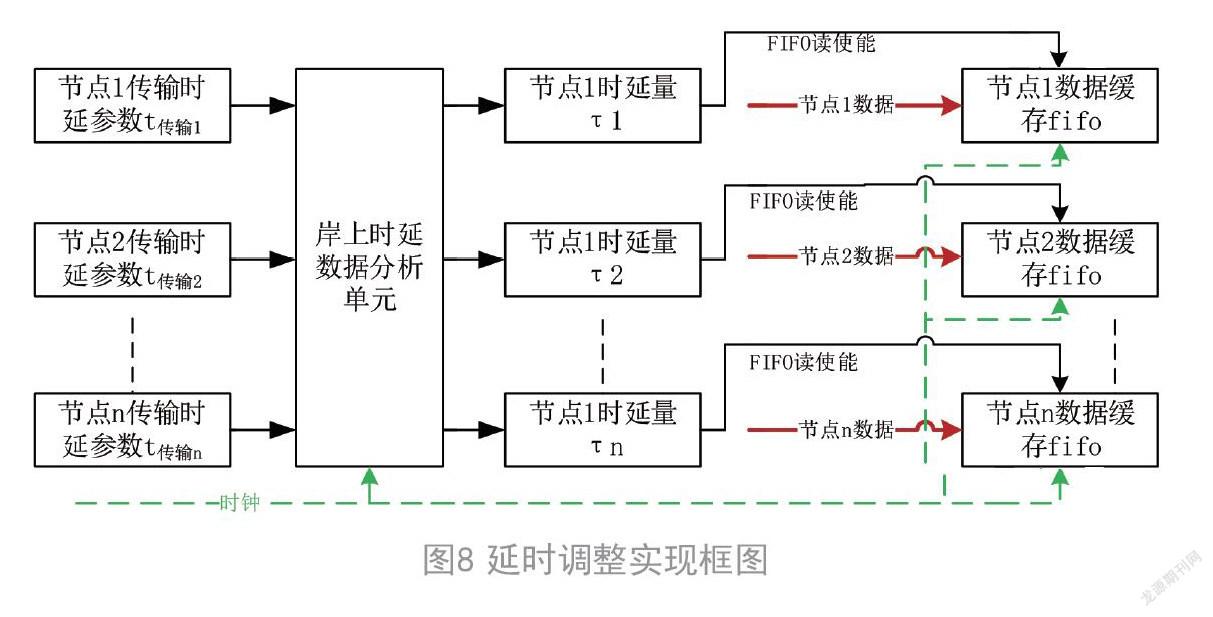

时延调实的实现原理如图8所示。

所有水下节点的时延参数td传递到岸上时延数据分析单元,在该单元内部通过分析处理计算出在当前路径下所有水下节点数据上传的最大时延tmax,选取这个节点的时延数据作为基准,计算出其他节点时延调整量τ,τ=tmax-td,并根据该参数输出各个通道的数据缓存FIFO的读使能。先将水下节点上传的有数据先输入到节点数据缓存,数据缓存采用FPGA内部的IP核,使用先进先出(FIFO)存储模式实时写入,按照各个通道的时延调整值进行控制,读出由岸上时延数据分析单元。时延控制的精度与数据读出的时钟频率有关。采用XilinxSpartan6FPGA时,其信号处理时钟最高能到350Hz,此时1个时钟周期的脉宽/调整周期可达3ns,大大高于水声信号采样周期2MHz,满足系统的使用要求。

5结束语

在水下信息网络中采用首尾相连的环形组网形式,大大提高了网络的可靠性;通过采用FPGA生成m序列及数字相关技术实现了传输链路时延参数的精确测量;利用FPGA的高速信号处理能力及内部自带FIFOIP,对各个水下节点信号时延进行精准调整,实现了系统中所有水下节点信号的同步输出。通过实际应用驗证,上述技术水下信号的输出时延一致性能达到1个时钟周期以内,大大减小了后续信号处理的压力,在水下信号的采集、监控、处理方面具有广阔应用前景。

参考文献:

[1]段文海,李震.双环自愈型水下光纤通信传输系统[J].光纤通信技术,2013,37(2):53-55.

[2]聂宝栋,黄敏,张勇.并联型水下光纤网络系统[J].光纤通信技术,2013,36(1):19-21.

[3]徐德余,唐再良.近世代数[M].成都:四川大学出版社,2006.

[4]孙鹏,叶萌华,张辉.数字相关器的FPGA实现[J].北京电子科技学院学报,2008,16(2):10-11.