铁电存储器的故障模型和March C-1T1C测试

魏蓬博

摘 要:铁电存储器读写时间短、功耗低、可重复擦除性好,因此,在航天航空、军事和公共交通等领域得到了越来越广泛的应用。一個晶体管和一个电容(1T1C)单元结构是常见的铁电存储器存储单元。本文对1T1C铁电存储阵列提出了几种基于电气缺陷的故障模型,包括晶体管常开、常关、开路和桥接故障。与现有的存储器故障相比,发现了两个新的故障,即写入故障(WDF)和动态写入故障(dWDF)。此外,还提出了一种改进的March C-1T1C测试,可以有效覆盖现有的故障和新发现的故障。

关键词:铁电存储器;存储故障;March C测试;Hspice仿真

中图分类号:TP333文献标识码:A文章编号:1003-5168(2020)28-0005-04

Failure Model and March C-1T1C Testing of Ferroelectric Memory

WEI Pengbo

(School of Mechanicl and Electrical Engineering, Xichang University,Xichang Sichuan 615013)

Abstract: Ferroelectric memory has gained more and more electric researchers' favor with the advantages of short time of reading and writing, low power consumption, and good repeatable erasability. A transistor and a capacitor (1T1C) cell structure are common ferroelectric memory cells. In this paper, we presented several fault models based on electrical defects for 1T1C ferroelectric memory arrays, such as transistor stuck-open and stuck-on faults. Two new faults, write fault (WDF) and dynamic write fault (dWDF) were found compared to existing memory faults. In addition, an improved March C-1T1C test was also proposed to provide good coverage of both existing and newly discovered failures.

Keywords: ferroelectric memory;storage failure;March C test;Hspice simulation

1 研究背景

铁电随机存储器能满足电子设备小型化、低功耗和长寿命的空间应用要求[1],有着良好的空间应用潜力。空间环境中存在宇宙射线和带电粒子,电子设备要求具有良好的耐辐射性能。大量实验表明,铁电材料对辐射有很高的耐受性[2]。

铁电存储器存储数据的功能主要是由铁电薄膜材料为介质的铁电电容实现的。当外加电场加到铁电晶体时,晶体中的中心原子会顺着电场的方向发生移动。当移动的原子通过一个能量壁垒,会引起电荷的击穿。铁电材料的极化特性会随着这个外加电场发生改变,当这个电场去掉以后,数据信息就保存在铁电晶体中。在没有外加电场的情况下,极化特性会呈现出两种稳定状态[3]。

本文研究了4种电气缺陷引起的铁电存储器的故障模型及相邻单元之间的桥接缺陷。此外,研究者还提出了一种测试算法来覆盖定义的故障。

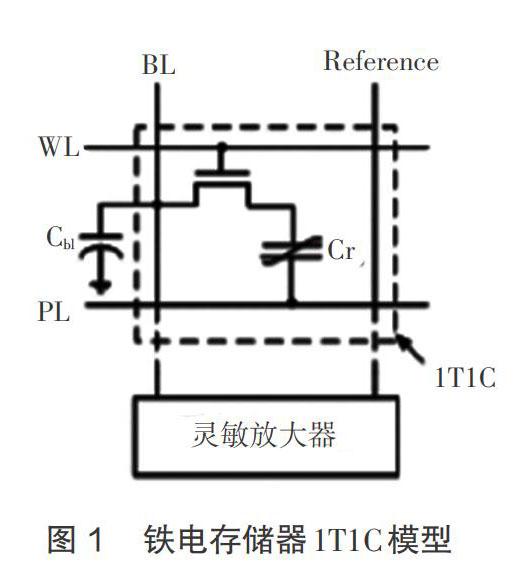

2 1T1C铁电存储器单元

1T1C铁电存储器的电路由1个存取晶体管和1个铁电电容(1T1C)构成,如图1所示。该结构的铁电电容[Cf]的一端通过存取MOS管连接位线(Bit Line,BL),另一端连接驱动线(Power Line,PL),MOS管的开断通过字线(Word Line,WL)控制,[Cbl]是位线BL上的寄生电容。

图2为铁电存储器1T1C故障模型,其中ATon和ATopen表示存取晶体管固定导通和固定关闭的缺陷。此外,Ro1、Ro2和Ro3表示1T1C单元内可能存在开路缺陷。由于铁电存储器存储密度很高,因此需要考虑相邻1T1C单元之间的桥接缺陷。图3所示的是铁电存储器2×2 1T1C结构阵列用于缺陷分析。

通过注入以下的电气缺陷来分析铁电存储器的存储单元可能出现的故障行为:①晶体管恒定导通,即无论栅极电压如何,晶体管始终处于导通状态;②晶体管恒定关闭,即无论栅极电压如何,晶体管始终处于关闭状态;③开路缺陷,连接线内出现冗余的电阻;④桥接缺陷,两条信号线之间出现冗余电阻。

3 故障模型仿真

3.1 晶体管正常工作

在仿真具有缺陷注入的铁电存储器之前,须验证铁电存储器2×2 1T1C结构阵列的正确性。图4是本次仿真模型,包括2×2的1T1C结构阵列、地址译码和控制译码。其外围电路的设计参考Sheu等报道随机存储器的外围电路[4]。图5(a)显示了铁电存储器执行w1r1和w0r0操作序列时的无缺陷模拟波形。PRE信号用于打开铁电存储器,若PRE=1,则可执行读/写操作。若WR=1,则执行写操作,并将Din的数据写入寻址单元;若WR=0,则执行读操作,并将存储在寻址单元中的数据读出到Dout。

3.2 晶体管恒定关闭

仿真过程中,通过不同缺陷注入的仿真来对不同缺陷进行分析。设定开路缺陷和桥路缺陷的电阻在0到∞区间。此外,每次只注入一个缺陷,然后執行电路仿真。若1T1C单元的晶体管恒定关闭,假设1T1C单元中晶体管的等效电阻为RAT,则RAT=∞。因此,从理论分析可知,无论写入数据如何,等效电阻将为∞,读取数据将恒为逻辑1。图5(b)显示了在w0r0操作下1T1C单元有晶体管恒定关闭且初始状态为逻辑1时的波形,验证了理论分析的正确。因此,晶体管的缺陷会导致固定1故障即SAF(1)故障。

3.3 开路缺陷

如图2所示,若开路缺陷位于BL和PL之间,如Ro1或Ro2,则1T1C单元的等效电阻增加,这会导致电容两端的电压降低。若电容两端的电压小于晶体管阈值电压[Vth],则该单元不能被编程。因此,电容的电压值取决于晶体管的初始状态。当单元中的开路缺陷Ro1或Ro2电阻很大时,开路缺陷将导致SAF(1)故障,而不管电容的初始状态如何。相反,若单元中的开路缺陷Ro1或Ro2的电阻不大,则开路缺陷可能导致SAF(1)故障或导致固定0故障[SAF(0)故障]、翻转0故障[TF(↑/0)故障]或未知读取故障(URF)[5]。

3.4 晶体管恒定导通和桥接缺陷

晶体管卡住和桥接缺陷可能导致单单元故障或双单元故障。对于双单元故障,一个单元是入侵单元,另一个单元是受害单元,入侵单元影响受害单元的状态。

为分析缺陷导致的双单元故障,入侵单元和受害单元的状态如下所示:Sa={0,1,0w1,1w0,0r0,1r1};Sv={0,1}。其中,Sa和Sv分别表示入侵单元和受害单元的状态;0和1表示当前状态值;w/r表示读/写操作;1w0即表示当前状态是1写入0[6]。通过Hspice仿真,注入可能的桥接缺陷和晶体管恒定导通。

以桥接缺陷(RB4)为例,若晶体管恒定导通缺陷(ATon缺陷)被注入单元C(0,0)中,图6(a) 显示了如果入侵单元C(1,0)执行写1写0(w1w0)序列,且受害单元C(0,0)具有初始状态1,这两个缺陷的仿真结果。注入ATon缺陷C(0,0)恒为逻辑0。原因是当C(1,0)执行写0(w0)操作时,因ATon缺陷,C(0,0)也被写入;所以,在入侵单元中执行的写入操作,受害单元的状态受到干扰,由此,我们认为这两个单元具有写入故障(WDF)。但是,如果注入RB4的电阻大于晶体管的导通电阻,则受害单元的状态不是逻辑0,受害单元受到入侵单元的干扰较小,即桥接缺陷的电阻值会影响入侵单元干扰。

由于电容两端的电压受到通过电容的电流持续时间和大小的影响,因此入侵单元的缺陷大小和写操作的次数也会受到影响。以ATon和RB4的缺陷为例说明:如图7(a)所示,假如单元C(0,0)具有ATon缺陷,晶体管的导通电阻远小于RB4的电阻。假设入侵单元和受害单元的初始状态为逻辑1。如果缺陷大小很小,则入侵单元C(1,0)中仅一个写0操作就可以改变受害单元C(0,0)从高阻抗电压(UHRS)变低阻抗电压(ULRS)这样的状态,翻转成逻辑0。

但是,如果考虑如图7(b)左图所示,晶体管的导通电阻约等于RB4的电阻,则入侵单元中的一次写0操作不能将C(0,0)的电容两端的电压更改为ULRS。但是,若在入侵单元C(1,0)中执行两个连续的写0操作,则电容两端电压可以减少到ULRS,并且受害单元的状态被翻转。图6(b)显示出了当入侵单元执行1w0w0序列并且受害单元注入ATon和RB4缺陷且初始状态为1时的波形。与图4(a)所示的波形相比,发现受害单元的数据也翻转了。因此,在入侵单元中通过大于两次连续写入操作将激活WDF,称该故障为动态写入故障(dWDF)。

4 March C-1T1C测试

在铁电存储器理论1T1C结构分析和仿真分析中发现两个新故障,即写入故障(WDF)和动态写入故障(dWDF)。通过改进March C算法覆盖铁电存储器1T1C新出现的两种故障,提出新型的March C-1T1C算法:

?(w0);?(r0,w1,r1,(w1)a-1);?(r1,(w0)b);?(r0,(w1)a);?(r1,(w0)b); (1)

其中,a和b分别表示用于检测dWDF所需的连续写入1和写入0操作的数量。March-1T1C由五个March元素组成,M1=?(w0);M2=?(r0,w1,r1,(w1)a-1);…;M5=?(r1,(w0)b)。March C-1T1C算法覆盖可能出现的故障的方式主要表现在以下几方面。

①SAF(1)故障:通过M1和M2的第一次读操作即可以检测出。

②SAF(0)故障:通过M2可以检测出。

③TF(↑/0)故障:可通过M1和M2中r1读操作检测出。

④CFst(0,0):如果入侵单元的位置高于受害单元,可以通过M2和M3检测出;如果入侵单元的位置低于受害单元,可以通过M4和M5检测出。

⑤WDF和dWDF可分成以下三种情况:第一,如果故障为WDF(1,1)和dWDF(1,1)且入侵单元位置低于(高于)受害单元,可通过M1和M2(M3和M4)检测出;第二,如果故障为WDF(0,0)和dWDF(0,0)且入侵单元位置低于(高于)受害单元,可通过M2和M3(M4和M5)检测出;第三,如果故障为WDF(1,0)和dWDF(1,0)且入侵单元位置低于(高于)受害单元,可通过M2和M3(M4和M5)检测出。

5 结语

本文针对铁电存储器2×2 1T1C存储单元阵列可能出现的缺陷内容进行了全面分析,并通过Hspice仿真模拟晶体管恒定导通、恒定关闭、开路缺陷和桥接缺陷的电气缺陷对1T1C型铁电存储阵列的影响,发现了两个新的功能故障,即写入故障和动态写入故障。最后提出March C-1T1C测试算法,以有效地覆盖铁电存储器2×2 1T1C存储单元阵列的故障。

參考文献:

[1] J. F. Scott, P. De Araujo, A. Carlos. Ferroelectric memories[J]. Science(Washington, D. C.),1989(4936):1400–1405.

[2] J. Schwank, R. Nasby, S. Miller, et al. Total-dose radiation-induced degradation of thin filmferroelectric capacitors[J]. IEEE Transactions on Nuclear Science,1990(6):1703–1712.

[3]Bosser A L , Gupta V , Javanainen A , et al. Single-Event Effects in the Peripheral Circuitry of a Commercial Ferroelectric Random-Access Memory[J]. IEEE Transactions on Nuclear ence,2018(99):1.

[4] Shyh-Shyuan Sheu,Pei-Chia Chiang,Wen-Pin Lin,et al. A 5ns fast write multi-level non-volatile 1 K bits RRAM memory with advance write scheme[C]// Symposium on Vlsi Circuits. IEEE,2009.

[5] S. Kannan, J. Rajendran, R. Karri, et al. Sneak-path testing of crossbar-based nonvolatile randomaccess memories[J]. IEEE Transactions on Nanotechnology, 2013(3):413–426.

[6] Chen Y X,Li J F . Fault modeling and testing of 1T1R memristor memories[C]//2015 IEEE 33rd VLSI Test Symposium (VTS).2015.