SHA算法的硬件设计与实现

张阳

摘 要 本文先简单介绍了一种用于消息认证的加密算法——SHA的原理,接着结合FPGA的硬件特性,重点阐述了一种用于安全协处理器中的SHA密码芯片的方案设计及优化方法,最后给出了硬件实现过程和较好的测试结果。

关键词 散列函数;安全散列算法;SHA

引言

Hash函数是把可变输入长度串转换成固定长度输出串的一种函数。一个安全的hash函数必须满足下面的条件:对任意长度的消息,产生固定长度的hash值;由消息到hash值的映射过程易于实现;由hash值反映射为原始消息是不可行的;欲构造任意两个不同的明文,使其有相同的hash值,也是不可行的。常用的单向hash函数有MD5,SHA等,而SHA因其实现更简单,安全性更高,而更为广泛地应用于身份认证,数据完整性鉴别等方面。

SHA(Secure Hash Algorithm)由美国国家标准和技术协会(NIST)开发,于1993年作为联邦信息处理标准(FIPS PUB 180)发表。SHA由麻省理工学院的Ron rivest开发,设计很近似于MD4模型,易于硬件实现。本文所述的SHA密码芯片采用FPGA技术实现,主要应用于安全协处理器中[1]。

1 SHA算法原理

SHA对长度不超过264的消息产生160位的消息摘要输出,其步骤如下:

(1)消息预处理。先填充附加位,使消息长度对512取模余448。即使信息已经达到需要的长度,也需进行填充,因此填充消息长度范围是1至512。附加位为单个“1”和若干个“0”。按上述方式填充后,再填充64位原消息長度,使消息长度恰好是512的整数倍。

(2)SHA运算。其运算流程如图1所示。图中,CV为160位的hash值。先将其初始化为CV0,与对应的消息分组Y0作SHA运算后生成hash值CV1;再将CV1与Y1作SHA运算后生成CV2。共进行L次迭代运算后得到的CVL即为最终的hash函数值。

将CV用5个32位字(A,B,C,D,E)表示,其初始值CV0为如下16进制值:

A=67452301;B=EFCDAB89;C=98BADCFE;D=10325476;E=C3D2E1F0。

在图1的SHA运算功能模块中,先将Yi分为80个16位的子分组;再分别参与80轮迭代;最后将最终迭代结果的每个字与CVi的对应字作模232加法,从而生成CVi+1。

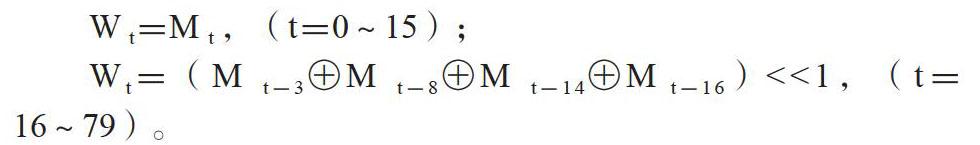

Y的子分组过程为:先将512位Y分为16个32位M t(t=0~15),再由此产生80个32位子分组W t(t=0~79)。产生方式如下:

W t=M t ,(t=0~15);

Wt=(M t-3⊕M t-8⊕M t-14⊕M t-16)<<1,(t=16~79)。

<<表示循环左移,+表示模232加,Ft与Kt随t变化。

(3)输出hash值。将进行L次SHA运算后得到的CVL缓存后输出。

2 密码芯片的方案设计

该SHA密码芯片用于安全协处理器(PCI板)上,受外围电路时钟频率和数据宽度限制。为使该设计芯片和外围电路协调工作,可将SHA算法系统的设计方案分为如下三个模块:消息预处理模块、SHA算法实现模块和hash值输出模块 [2]。SHA算法实现模块是设计的核心模块,主要完成SHA运算。根据其流程特点及硬件结构,进行如下设计和优化。

2.1 子分组W的生成

如上节所述,1次SHA运算需要80个32位子分组Wt,而在实际设计时,根据其产生规律和硬件结构,仅需16×32位的RAM和1个32位的寄存器即可。先将Wt(t=0~15)依次存于RAM中;而32位寄存器用以存储从RAM中取出4个相应的Wt进行异或移位的值;此后,每个新的Wt均直接从该寄存器中直接读取,并同时更新RAM中对应的Wt的值。因此,每个新的Wt的产生公式则变为:

wt <=(w(t mod 16) xor w((t+2)mod 16) xor w((t+8)mod 16) xor w((t+13)mod 16))<<1;

80个子分组Wt在经过上述5轮RAM循环写操作后全部产生。而80个子分组Wt参与加密运算,即对RAM的读操作,也与写操作同时进行。经过上述处理,能最大程度地节约FPGA中宝贵的存储资源,并能较好的简化硬件操作的复杂度。

3.2 80轮迭代

由于80轮迭代的流程完全相同,故可以设计一个迭代模块,再对其复用80次,每次迭代的输出存入寄存器中,作为下一轮迭代的输入,这样可极大的优化FPGA的硬件资源。其中,循环移位运算硬件容易实现。Ft是关于B、C、D和t的非线性函数,可采用多路选择器产生。在具体实现时,可将B、C、D参与运算的可能的结果预先以异步方式先算出,再由t作判断,指定1路结果[3]。

3.3 模232加法运算

模232加法运算多次应用于SHA运算过程中,直接关系到密码芯片的运算速度。考虑到模块的复用性,所有的模加运算均采用4个8位分块的超前进位加法器并接实现,其结构如图4所示。

参考文献

[1] 殷辉,胡晓宇.适用于家庭安全网关的HMAC SHA3算法的硬件设计[J].集成电路应用,2020,37(5):14-17.

[2] 房海松,司伟建.基于FPGA的二维谱峰搜索算法硬件架构设计[J].空天防御,2020,3(1):58-64.

[3] 谷会涛,武宗涛.基于双重流水同步迭代的SM3算法高速硬件设计[J].计算机与网络,2020,46(2):54-56.