基于FPGA 的手势信号实时采集综合性实验项目研究

郑雪峰,马学条,汤 峻,陈 龙,杨 柳

(杭州电子科技大学 电子信息技术国家级虚拟仿真实验教学中心,浙江 杭州 310018)

借助信息技术能有效解决实验教学过程中时间、地域和安全等限制问题,对于探索实验教学新模式具有重要意义[1]。我校数字电路教师团队为了实施全方位开放式教学,围绕拓展实验内涵、激发学生学习兴趣、培养学生工程创新意识等,开发了“基于FPGA 的手势信号实时采集综合性实验项目”,借助远程虚拟仿真实验教学手段,实现了全方位开放式教学,有效地拓宽了数字电路实验教学的时空领域。

1 实验教学模式

数字电路实验教学一般是利用实验室数字电路实验箱,学生在实验室里完成实验设计,然后提交实验总结报告。这种教学方式缺乏灵活性,不能激发学生的学习兴趣和实验热情[2]。

经过多年实验教学改革与实验平台建设,形成了“远程虚拟实验”教学模式,如图1所示。学生只需连接网络,通过开放式实验教学管理系统,即可在寝室、实验室或教室等区域远程共享实验教学资源,突破时间、空间限制,进行数字电路虚拟仿真实验操作,远程提交仿真结果,实现“处处能学、时时可学”的泛在化学习[3]。

图1 远程虚拟仿真实验教学流程图

2 综合创新性实验项目开发

“基于FPGA 的手势信号实时采集综合性实验项目”,旨在使学生综合运用电子设计自动化(EDA)技术,通过自主设计、虚拟仿真等环节,完成实验设计。使学生将理论和实验知识融会贯通,提高设计复杂数字系统的能力及实践创新能力[4]。

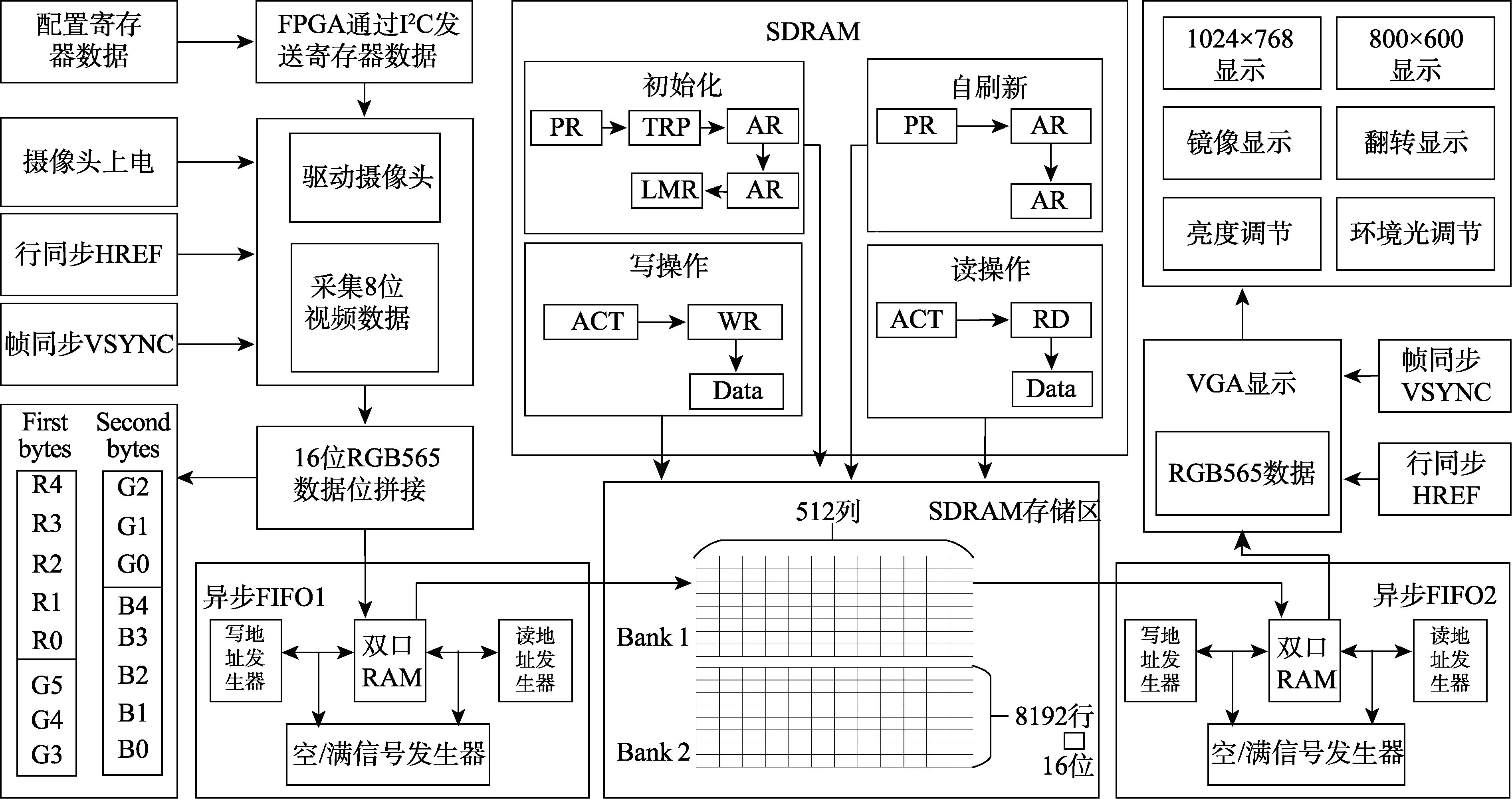

如图2 所示,实验系统由数据采集模块、异步FIFO 模块、SDRAM 模块和VGA 显示模块等组成。通过I2C 配置好OV5640,将采集到的8 位特定分辨率信号转化为RGB565 格式;将转换好的16 位的像素信号通过FIFO1 缓存,同时存入SDRAM;存入每帧像素后,将SDRAM 输出给FIFO2;再将FIFO2 输出的每帧数据通过VGA 模块进行显示。

图2 “基于FPGA 的手势信号实时采集综合性实验”系统框图

2.1 数据采集电路设计与仿真

数据采集模块采用OV5640 摄像头进行图像采集,外接18 根引脚。SCLK、SDAT 为I2C配置引脚;DB0~DB7为采集像素数据;CMOS_HREF、CMOS_VSYNC 为摄像头行同步信号和帧同步信号;PCLK 为I2C 配置好的像素时钟;XCLK 为输入时钟;3.3 V 供电引脚和接地引脚;复位引脚,低电平有效;PWDN 为上电控制引脚,高电平有效。采集的过程为先通过摄像头的上电时序之后,FPGA 通过I2C 配置其寄存器,设置输出格式为RGB565,输出分辨率为1024×720。由于摄像头采集的是8 位像素数据,而RGB565 格式为16位信号,所以需要将两个8 位信号合成16 位信号。一个PCLK 上升沿,采集一个8 位信号,输出一个16位RGB565 信号,则需要两个PCLK。当帧同步信号VSYNC 从低电平到高电平跳变时,标志一帧采集的结束,当满足VSYNC 为低电平并且HREF 为高电平时,才是有效像素。由数据手册可知,OV5640 采集的前10 帧是无效帧,因此有效帧应该从第12 帧开始算起。寄存器配置及采集位拼接电路如图3 所示。

FPGA 通过I2C 协议向摄像头发送配置摄像头所需的寄存器值,以下是常用的配置寄存器值。

分辨率设置:

Reg_Data<=24'h380804;

Reg_Data<=24'h380900;

Reg_Data<=24'h380a02;

Reg_Data<=24'h380bd0;

亮度调节:

Reg_Data<=24'h558740;

Reg_Data<=24'h558801;

镜像调节:

Reg_Data<=24'h382107;

Reg_Data<=24'h382100;

翻转调节:

Reg_Data<=24'h382047;

Reg_Data<=24'h382047;

2.2 FIFO 模块设计与仿真

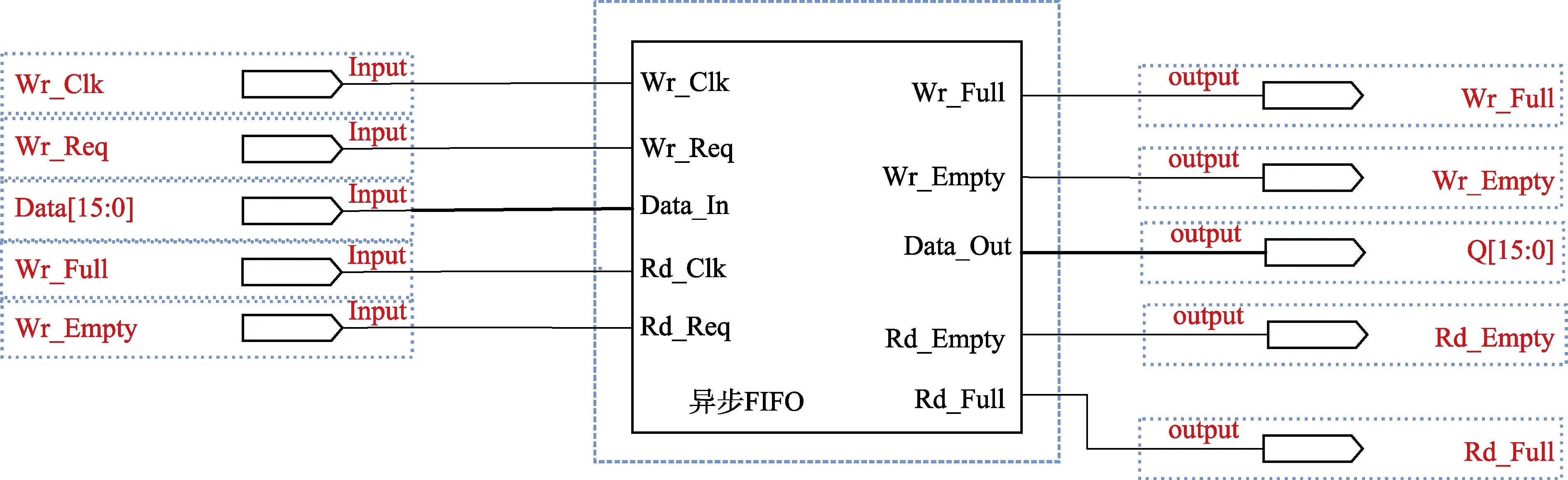

实验设计中需采用两个异步 FIFO,记为异步FIFO1 和异步FIFO2。异步FIFO1 主要负责缓冲来自摄像头采集的像素,然后交给SDRAM 缓存;异步FIFO2 主要负责接收来自SDRAM 的像素信号,然后投到VGA 上显示。摄像头采集的视频数据时钟频率为24 MHz,SDRAM 的驱动时钟频率为100 MHz,因此需要异步FIFO1 作为中间缓冲。VGA 显示的时钟频率为65 MHz,与SDRAM 的驱动时钟频率也不同,因此需要通过异步FIFO2 进行缓冲。如图4 所示,当两个独立的系统主频不一样时,需要通过异步FIFO作为缓冲,使得数据可以从一端传送到另一端[5]。

图3 寄存器配置及采集位拼接电路框图

图4 异步FIFO 框图

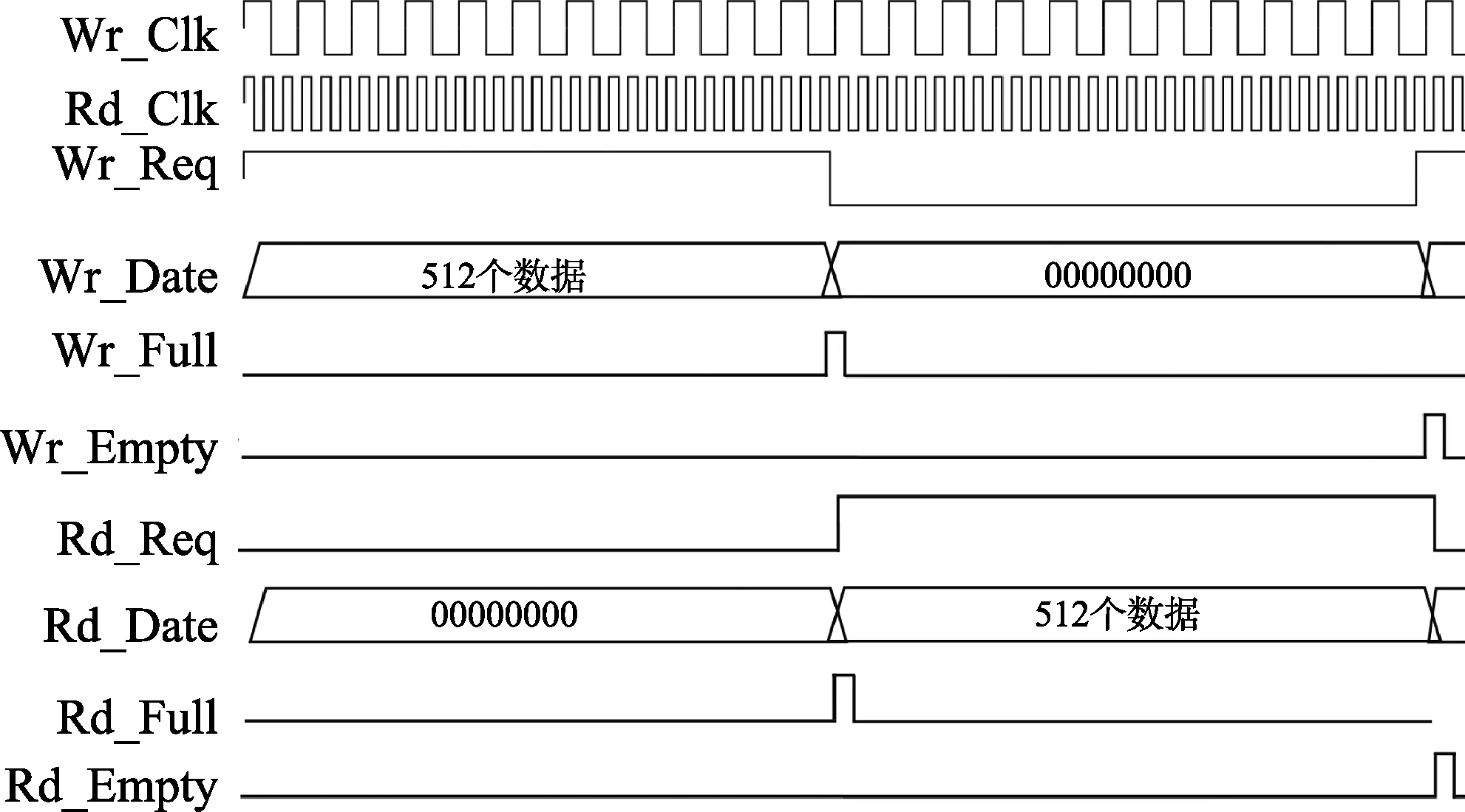

设置异步FIFO 模块的数据为16 位,深度为512 个单元。对FIFO 模块进行仿真,时序仿真结果如图5 所示。其中,Wr_Req 为写信号,Wr_Clk 为写时钟,Wr_Data为写数据,Wr_Full 为写满标志,Wr_Empty 为写空标志,Rd_Req 为读信号,Rd_Clk 为读时钟,Rd_Data 为读数据,Rd_Full 为读满标志,Rd_Empty 为读空标志。

图5 FIFO 模块仿真图

由异步FIFO 仿真图可知,在输入端24 MHz 频率Wr_Clk 下写入256 个数据,写请求信号Wr_Req 在写入过程中一直呈现有效电平状态,写满后Wr_Full 信号拉高,写请求信号Wr_Req 拉低。在n 个时钟后,Rd_Full 读满信号拉高,于是在输出端100 MHz 频率的Rd_Clk 下,开始往外读出数据,在读数据过程读请求信号Rd_Req 一直呈现有效电平状态,在顺利读出256 个数据后,读空信号Rd_Empty 拉高,读请求信号拉低,n 个时钟后,写空信号Wr_Empty 开始拉高,准备继续写入数据。之后,这一过程不断循环执行[6]。

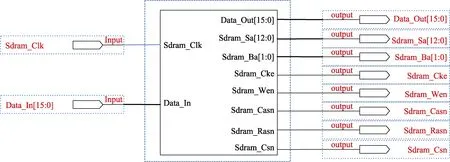

2.3 SDRAM 模块设计与仿真

SDRAM 采用型号为HY57V2562GTR 的芯片,256 M 容量,16 根数据线,13 根地址线,2 个区选线,5 根命令控制线。实验设计中,SDRAM 模块共分初始化、刷新、写操作、读操作等四个步骤。

在对SDRAM 进行写入读出的过程中,常规操作是对Bank1 中写入一帧数据,然后由异步FIFO2 读出并显示,接着继续写入下一帧。这种操作使得在写入SDRAM 过程中,异步FIFO2 无法读取,只能等待一帧写完才能读取。如果实验过程采用乒乓操作法原理,则在对Bank1 写入第一帧数据后,异步FIFO2 开始读出Bank1 中的一帧数据,同时异步FIFO1 向SDRAM中的Bank2 中写入下一帧数据。如此交替往复的读写过程,省去了大量等待时间,加快了视频传输效率[7]。

SDRAM 模块电路框图如图6 所示。其中:

Sdram_Clk(输入时钟频率):100 MHz。

Data_In(写数据):来自异步FIFO1 写入的16位RGB565 数据。

Data_Out(读数据):由异步FIFO2 读出至显示的16 位RGB565 数据。

Sdram_Sa(地址信号):读写地址,行列共用,A0—A12 为行地址,CA0—CA8 为列地址。

Sdram_Ba(区选信号):该块SDRAM 共有4 个Bank 区,每个Bank 可以存储64 Mbits。

Sdram_Cke(命令信号):片选信号,拉低有效。

Sdram_Wen(命令信号):片选信号,拉低有效。

Sdram_Casn(命令信号):片选信号,拉低有效。

Sdram_Rasn(命令信号):片选信号,拉低有效。

Sdram_Csn(命令信号):片选信号,拉低有效。

图6 SDRAM 模块电路框图

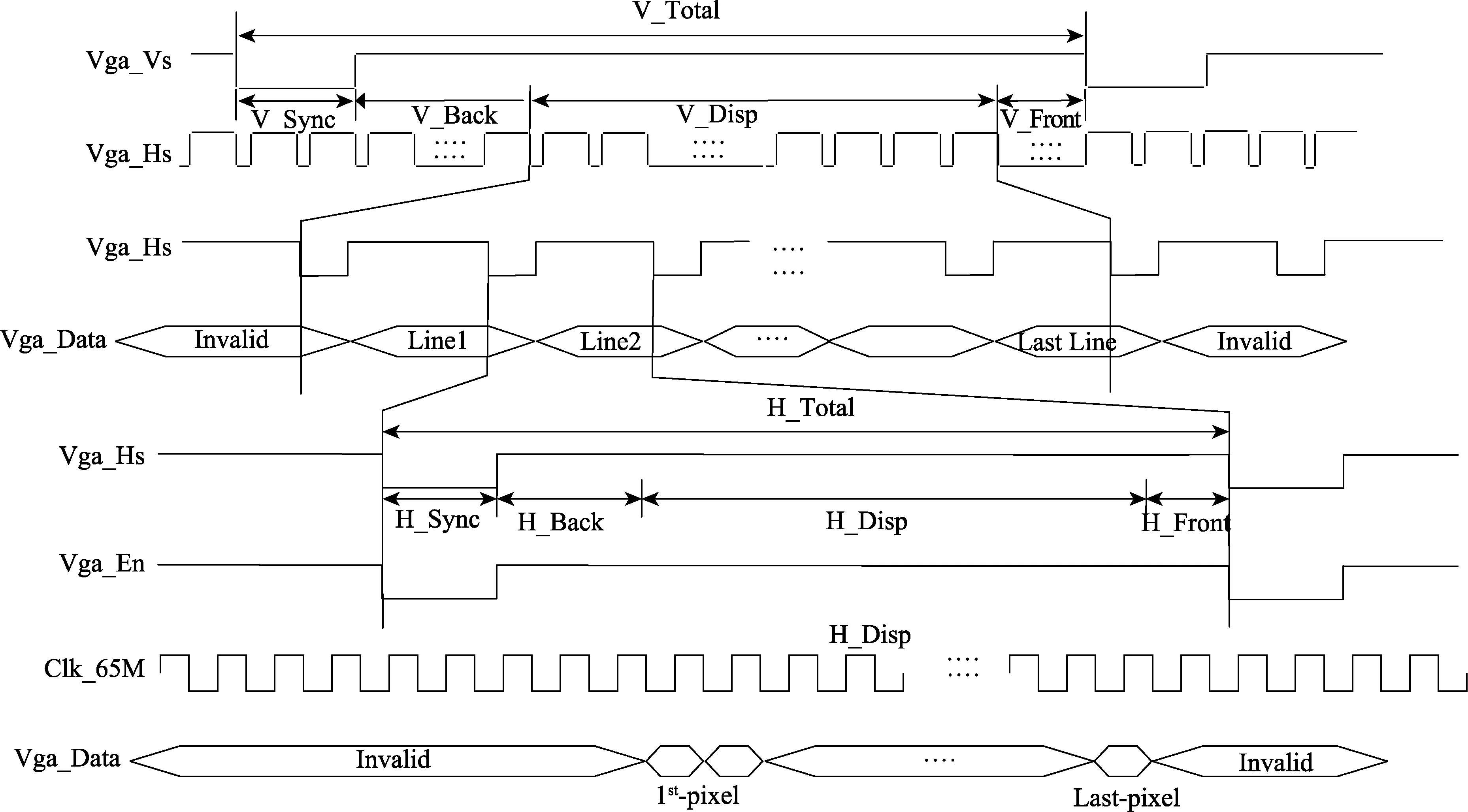

2.4 VGA 显示电路设计与仿真

VGA 显示模块电路框图如图7 所示。实验设计中,VGA 显示分辨率为1024*768,控制时钟为65 MHz。该电路设计中,需要描述VGA 的显示时序,包括行、帧同步信号,行消隐、帧消隐像素以及相关时序参数。有效像素的显示,行同步信号处于高电平;有效信号的显示,帧同步信号处于高电平。其中:

Clk_65M(输入时钟):VGA 显示时钟。

Vga_Data(输入数据):来自异步FIFO2 的16 位RGB565 数据。

Vga_En(使能信号):行帧同步的共同使能信号。

Vga_Hs(行同步信号):选择出VGA 上有效行信号区间。

Vga_Vs(帧同步信号):选择出VGA 上有效帧信号区间。

Vga_Rgb(输出数据):显示到VGA 显示器上的数据

VGA 行帧同步信号仿真结果,如图8 所示。其中:

H_Front 24 个像素时钟 V_Front 3 个行时钟

H_Sync 136 个像素时钟 V_Sync 6 个行时钟

H_Back 160 个像素时钟 V_Back 29 个行时钟

H_Disp 1024 个像素时钟 V_Disp 768 个行时钟

H_Total 1344 个像素时钟 V_Total 806 个行时钟

2.5 实验结果

根据系统方案设计要求,在原理图编辑文件中调用已生成的数据采集模块元件、异步FIFO 模块元件、SDRAM 模块元件和VGA 显示模块元件,构成图像采集显示系统顶层电路。选用FPGA 开发板进行硬件测试,硬件测试系统包括OV5640 摄像头、VGA 显示器、数字示波器和数字可调电源等[8]。针对同一手势信号,1024×768分辨率原图、800×600 分辨率原图、1024×768 分辨率镜像、1024×768 分辨率翻转、1024×768 分辨率亮度调节、1024×768 分辨率环境光调节等结果,如图9 所示。

图7 VGA 显示模块电路框图

图8 VGA 行帧同步信号仿真示意图

图9 “基于FPGA 的手势信号实时采集综合性实验”测试结果

2.6 硬件测试

完成远程实验仿真操作后,学生可利用实验室配备的FPGA 测试系统开展虚实融合测试,实现仿真指导实体实验、实体实验验证仿真的闭环流程。FPGA测试系统包括上位机、开发板、下载器、OV5640 摄像头、VGA 显示器等,在顶层文件设计的电路中定义输入输出引脚并进行锁定,编译后下载.sof 文件,在VGA 上显示各种处理后的图像。硬件测试系统如图10 所示。

图10 硬件测试系统

3 实验教学实施效果

数字电路实验课程面向我校电子信息、通信、自动化等12 个电子类专业的学生,每年直接授课学生1800 多人。团队教师对传统数字电路实验教学在教学内容、教学方法、课程组织及时间安排上存在的问题进行了研究和改革,以电子设计自动化(EDA)技术的学习为手段,注重工程能力、分析能力和实践能力的培养,构建了一个从基本实践技能向创新能力逐级递进的实践阶梯。“基于FPGA 的手势信号实时采集综合性实验”项目,提高了学生设计复杂数字系统的能力和参与学科竞赛的积极性[9]。

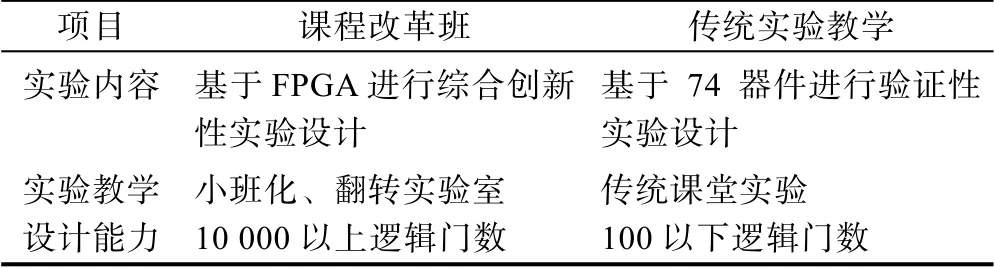

如表1 所示,学生在完成传统数字电路实验教学后(大学第四学期),其设计的电路规模仅为几十个逻辑门(如交通灯等),而参加课程改革的学生(大学第二学期),其设计的复杂数字系统规模大都在10 000逻辑门以上,学生设计数字系统的能力和水平得到很大提升[10]。学生通过自主完成实验项目设计、方案优化、硬件测试、撰写报告等工作,锻炼和提升了实践创新和工程应用能力,这些学生近三年共主持国家级、省级创新创业计划13 项。

表1 课程改革班与传统实验教学班情况对比

4 结语

经过多年实践与改革,基于FPGA 开发设计的综合创新性实验教学项目已成功应用于我校数字电路实验教学,具有如下特点:

(1)团队教师以开放式远程虚拟仿真实验平台建设为契机,拓宽数字电路实验教学时空领域,学生突破时空束缚,实现“处处能学、时时可学”的泛在学习[11]。

(2)采用“小班化、翻转实验室”模式进行综合创新性实验教学,激发了学生实验的自主性和创新性,符合创新能力培养要求。

(3)将传统数字技术与现代数字技术有机融合,采用FPGA 进行实验设计,有效解决了在有限课时内完成复杂数字系统设计的难题[12]。