实力搭上阿里、百度 走近这家AI芯片独角兽的硬核技术

李实

随着人工智能产业的兴起和市场空间的扩大,越来越多的公司开始进入人工智能产业,同时也顺带推出了不少新技术。在人工智能计算芯片方面,业内除了有英伟达、谷歌、英特尔这样的巨头在征战外,一些创业公司也凭借天才的设计和独创的技术希望跻身其中并分得一杯羹。来自英国的Graphcore就正是一家这样的创业公司,他们推出的IPU计算芯片尚未诞生,就引得业内巨头纷纷投资,近期更是推出了堪称史上算力规模数一数二的全新AI计算芯片,并且以独特的架构设计和技术特点得到了业界多家企业的青睐。从这一点来看,Graphcore的新技术和新产品的确值得我们进一步了解。

2020年6月,备受大家关注的全球超级计算机排行榜TOP500更新了最新一期的榜单。在新一期的榜单中,出现了一家名为Graphcore的公司。作为一家来自于英国的创业公司,Graphcore从2015年成立到现在也仅仅只有5年时间。但是就在这短短的5年中,Graphcore凭借其独特的技术,获得了来自微软、百度、阿里、宝马、博世、戴尔、三星等各行业巨头的青睐,其累计融资已经超过了4.5亿美元,公司估值也已经达到了19.5亿美元。Graphcore之所以能够获得如此多的投资,并且在这么短的时间内就推出了全新的芯片,还是由于它掌握了先进的设计思想并推出了令人满意的产品。

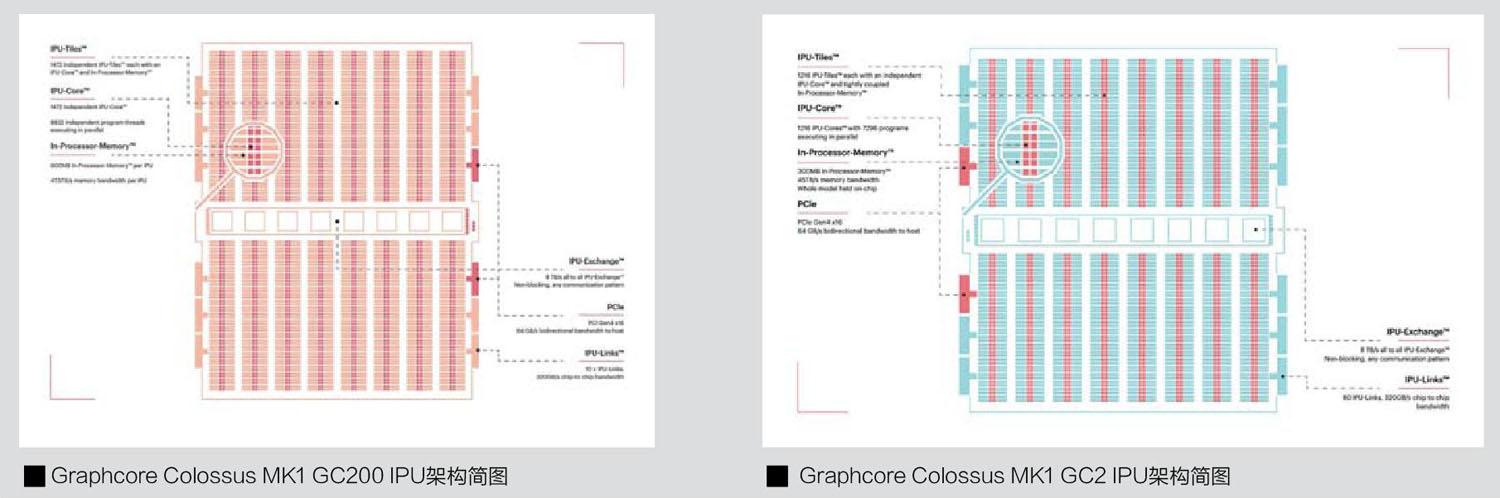

目前Graphcore一共推出了2款产品。第一款产品全称是GraphcoreColossusMK1GC2IPU(下简称为“GC2”),它采用了16nm工艺,集成了236亿晶体管。目前没有查到GC2的芯片面积,但是估计在600平方毫米之上。令人震惊的是Graphcore最新推出的一款名为GraphcoreColossusMK2GC200IPU(下简称“GC200”)的芯片,芯片面积高达823平方毫米,采用台积电7nm工艺制造。相比之下,之前英伟达推出的A100GPU芯片面积是826平方毫米,也是采用了台积电7nm工艺制造。GC200的芯片面积虽然比A100小了3平方毫米,但是GC200集成了高达594亿晶体管,相比英伟达A100的540亿晶体管,数量高出了10%。毫不夸张地说,在芯片尺寸方面,GC200虽然以微小的差距惜败,但是传统单芯片封装却包含了目前全球最多的晶体管数量、再加上Graphcore仅仅是一家创业公司,其第二款产品的规模就如此庞大,还是相当令人惊讶的。

如果进一步从它具体的计算能力来看的话,Graphcore宣称IPU对比传统产品,能够将自然语言处理的速度进一步提升20%~50%,并为图像分类带来更低的延迟以及相当于传统架构差不多6倍的吞吐率,还能够让金融模型的训练速度提升26倍以上。那么,IPU产品是如何带来如此巨大的性能提升的呢?

针对AI计算的并行架构:IPU架构简述

作为一个全新的产品,Graphcore在推出IPU之前进行了大量的深入研究,包括研究目前和未来可能出现的人工智能架构以及计算模型,试图找到其中的关键节点并加以优化,并最终实现在具体的产品之上。在IPU推出之后,Graphcore又进行了大量有关产品实现、系统架构、软件环境等方面的工作,并撰写了大量的技术文档供用户参考。本文这一部分的内容来自于Graphcore发布的《Citadel Securities Technical Report-Dissecting the Graphcore IPU Architecture via Micro benchmarking Dec 2019》白皮书。在这本白皮书中,Graphcore详细介绍了IPU是什么,和CPU以及GPU的差别在哪里,IPU如何实现更高的效率以及其独特的架构等。由于其内容已经相当完善,因此本文编译了其中比较重要和关键的部分以飨读者。

Graphcore推出的产品被称为IPU,全称是IntelligenceProcessingUnit,智能处理单元。在Graphcore的描述中,IPU是一种针对人工智能和机器学习的全新大规模并行计算架构。任何IPU计算设备的核心都是IPU处理器本身,这意味着IPU的设计目标是在相对大量的并行线程中,高效地执行细粒度操作,并且这种操作不同于其他大规模并行架构(例如GPU)。在这一点上,IPU提供了真正的MIMD(多指令、多数据)并行性,尤其是独创地将分布式的本地内存作为设备上唯一的内存形式,从而使得设备的运行不再需要外置內存的参与。在数据格式方面,IPU能很好地适应各种不规则数据,在不同的细粒度、不规则计算中呈现出色的效能。

从宏观上来看,一个IPU包含了数千个IPU计算块,一个IPU计算块包含了计算核和本地内存。除了寄存器文件外,IPU本身不提供额外的内存接口,只拥有分布式的本地内存。内部通讯方面,IPU中包含了专用的内部通讯交换器,允许不同的IPU计算块之间实现交互的高带宽、低延迟通讯。对外通讯方面,IPU采用了Graphcore的专用互联,能够实现和不同IPU之间的高效率通信。另外,每个IPU还包含了和CPU通讯的2个PCIe4.0总线。

本地SRAM搭配MIMD:IPU如何突出重围

IPU强调细粒度并行性,这意味着IPU可以高效地运行诸如不规则数据、稀疏数据或者拥有控制流的应用程序。和SIMD/SIMT架构不同的是,IPU不需要使用大量连续向量数据的线程来实现高效率,可以以高度并行的MIMD方式在较小的数据块上运行单独的处理线程。每个线程可以拥有完全不同的代码和执行流,且不会导致性能损失。与之相反的是,目前的GPU需要大量的连续矢量计算才能实现高效率,这对数据源和整个计算过程的控制又提出了较高要求。为了实现这样的计算优势,IPU在架构上与通常用于执行机器学习或者人工智能工作负载的平台(比如CPU或者GPU)有很大区别。

CPU运行模式:较少的复杂内核,偏向于控制和单线程

先来看CPU部分。CPU倾向于提供相对较小数量的复杂内核。简单来说就是用更少的核心搭配更复杂的内核,比如在目前桌面处理器上,常见的产品最多也就16个内核,即便是顶级处理器,其内核数量也不会超过64个。但是每一个内核都拥有多级复杂的流水线和厚重的前端、后端单元。

在架构方面,CPU核心具有复杂的延迟降低技术,如分支预测和乱序执行。这些优化使得CPU在单线程性能和控制代码方面优于其他处理单元,但可能会以能源效率和芯片本身的累计算术吞吐量为代价。由于CPU本身架构的原因,即使如今大多数CPU提供了向量化(比如SIMD、单指令、多数据,典型的就是英特爾AVX-512这样的指令集),但是在大型、常规、基于数组的工作负载上,它们在大规模并行浮点运算或能源效率(每瓦特性能)这些方面也无法与GPU相提并论。

不仅如此,为了隐藏内存延迟,CPU通常使用包含多个缓存级别的深层内存层次结构以及复杂的预取预测器,更增加了整个系统的执行代价,降低了计算效率,尤其是用于真正计算和性能输出的晶体管占比的下降。

GPU运行模式:大量并行计算核心的SIMT架构

接下来我们再看看GPU。GPU的特点是在每个芯片上拥有更小、更多的计算内核。GPU核心在架构方面相比CPU更简单,通常不提供分支预测、无序执行或硬件预取等功能。但是GPU核心的数量极其庞大,这就要求其在计算并行度上有极为出色的表现。

为了达到这个条件,GPU将它们的核心排列成多组同步运行的集群。这样可以使得集群中的所有核心在任何时间点都执行相同的指令。线程被有规律地集合成为波次(warp)、波次再被规律地排列成为计算簇(clusters)。每个波次中单独的一个线程都会相对独立地执行相同的操作。这种执行模型称为SIMT,也就是单指令多线程。

在单指令多线程方面,人们还为GPU配备了大量的数据缓存和多级存储结构,但它们隐藏内存延迟的基本方法仍然是不断地切换线程以及尽可能地将它们塞满整个计算核心。在这种方法中,当一堆线程等待内存(显存)中的操作数时,硬件将直接挂起这个等待中的线程,并将其切换到另一个已经从内存中接收到操作数并准备继续执行的线程。GPU编程模型也明确鼓励开发人员在线程并行性上进行更多优化,以便始终有一部分线程准备执行,而其余线程等待操作数。

除了执行方面的内容以外,GPU对于主内存的访问也存在一定的要求。目前GPU的编程模型要求,只有当负载和存储操作在每个波次内涉及相邻的内存区域时,才允许GPU以峰值吞吐量访问主内存。并且这种内存访问在一些操作中,要求必须遵循一定规则的状态出现,那些无法遵循一定规则的内存访问只能达到理论峰值内存带宽的一小部分。为了获得最佳性能,开发人员必须实例化共享同一程序的大线程块,尝试以协调至相应规则的方式使用输入(输出)数据,并有节制地使用控制流。另外值得一提的是,SIMT对线程的要求非常严格,当线程在它的控制流中分离时,GPU将不得不停下来等待后续数据载入,这会使得它的性能受到一些影响。

从上面的这些描述中可以看出,GPU擅长于那种规则的、密集的、并行化的、数据流为主的工作负载,这些工作负载配合相关的规则和一致的控制流将使得GPU运行效率大大提升。在这类工作负载上,GPU往往比CPU更节能且更高效,这不是由缓存或面向延迟的特性(比如分支预测)所决定的,而是由于它用于计算的晶体管比例更高。

IPU运行模式:本地SRAM搭配大量计算核心

再来看看IPU。IPU在很多方面和GPU有点类似。比如IPU同样具备巨大的核心数量,但这些核心将拥有更为复杂的计算能力,能够执行完全不同的程序。IPU减少内存延迟的方法是革命性的—它完全消除了共享内存。IPU只提供本地的、能紧密耦合到每个核心的分布式小内存。在这一点上,IPU的内存更像是一个个计算核心自己的“小便签”,而不是大家一起使用的“大账本”。另外,IPU采用的分布式小内存使用了SRAM,能够比内存或者显存使用的DRAM提供更快的速度和更高的带宽,当然还有更低的延迟(低至6个时钟周期,DRAM一般在20~30个时钟周期甚至更高)。SRAM的性能与L2CPU缓存相当,也要显著优于GPU的共享内存(或NVIDIA称为的L1缓存)。在采用了独特的分布式内存模

式后,IPU所拥有的显著优势是当控制流出现发散的情况时,或者当它们的内存访问地址发散时,IPU核心不会遭受严重的性能损失,而这往往是GPU面临的比较困难的问题。实际上,IPU核心在受到不相关指令的不连贯内存访问时,几乎没有什么性能损失。这是因为IPU核心只从各自的本地内存访问数据,这与访问模式无关。这使得IPU在执行那些采用不规则或者随机数据访问模式的应用程序,或者类似控制流控制的应用程序时比GPU更高效。当然,这里的前提是计算任务本身需要处理至适合IPU的存储模式。

在计算效能方面,和CPU、GPU类似的是,IPU也是通过保证核心始终处于工作负载中来实现更高的效率。具体来说,每个IPU块都提供了对6个线程的硬件支持,其功能类似于CPU上常见的SMT技术(同步多线程,或英特尔的超线程)。因此,每个IPU块都可以驻留6个执行上下文,这在一定程度上隐藏了指令延迟(依赖、内存访问和分支延迟),减少了相应的管道停顿,并增加了总吞吐量。此外,每个IPU块还可以根据静态的循环调度在线程之间不断跳转任务。同样在软件层面,为了获得最大的占用率,依旧鼓励软件设计人员实例化更多线程以方便IPU调用。

另外一个值得提及的内容是IPU的算术吞吐量。IPU的计算实现方式是采用名为累积矩阵乘积(AMP)单元的专用单元,这种专用单元被设计在每个IPU计算块中,专门用于加速矩阵乘法和卷积运算。一个AMP单元每个时钟周期可完成64个混合精度或16个单精度浮点运算。上一代IPUGC2的单精度计算能力高达31.1TFlops/s,混合精度计算能力高达124.5TFlops/s。最新一代的IPUGC200暂时没有看到相关的数据,但是官方宣称其计算能力相比第一代提高了8倍之多。这也远远超过了目前GPU所能达到的计算速度。

当然,它所具备的实际算术性能极大地依赖于特定的数值工作负载,因此可能与理论数据有很大的不同。根据Graphcore的测试,第一代GC2芯片的单精度性能明显优于英伟达的V100GPU(每颗芯片的比较)。在复杂一些的计算中,由于受到的限制因素比较多,暂时很难得到明确的结果。

在内存方面,IPU采用的是分布式SRAM本地内存方案。在GC2中(GC200的数据暂时没有更新),IPU的每个块包含256KBSRAM,在整个处理器上总计是304MB。每个块都有一个独立的、连续的21位地址空间,由6个硬件执行上下文共享,其中本地执行的代码和本地处理的数据必须相互匹配。在GC2芯片中,本地内存的名義带宽达到45TB/s,而延迟为6个时钟周期。虽然IPU的容量低于典型的GPUDRAM内存(如32GB),但IPU内存在速度上弥补了它们在容量上的不足。比如与英伟达T4GPU上的L1缓存和共享内存相比,IPUSRAM的延迟更短,与IntelSkylake、KabyLake、CoffeeLakeCPU上L2缓存的延迟相当,容量基本相当(值得注意的是,GC200的每个计算核心的SRAM本地内存容量要大得多)。从实际情况来看,IPU内存的总大小可以消除在GPU和CPU上类似缓存层次结构的相应需求,从而极大地释放了传统多级内存模式中占用的资源,并且可以大幅度提高数据存取效能。

IPU的通讯模式:更为有效地交换数据

互联体系是IPU的核心架构之一。正是由于优秀的互联体系设计,IPU系统上的每个计算块才能紧密地工作并彼此有效地交换数据。这也是那些拥有多个IPU芯片的大规模系统真正可以被看做一个单一的、一致性的设备的原因。

具有多个IPU芯片的系统独立地公开单个IPU设备,同时它也会公开每个IPU核心。在目前的情况下,IPU设备有能力将多个IPU核心或者系统虚拟为一个设备,并向用户提供它们所有的内存和计算资源,这样一来它将允许用户训练和推断比单个IPU容量更大的模型,同时利用多个IPU芯片的计算能力。

为了搭建这样的系统,IPU将互联部分分为了片上互联和片外互联(设备互联)两个部分。在GC2上,它的片上互联总吞吐量为7.7TB/s,而GC200的片上互联吞吐总量则为8TB/s。在GC2的1216个计算块中,每一个块都可以同时使用6.3GB/s的带宽,并将数据传输到芯片上的任意目的地。片上计算块到计算块的交换延迟为165ns或更低,并且在负载高于该值时不会降低。

片外互联部分,面向系统内其他设备,IPU可以通过PCIe接口连接到它的主机系统并获取数据,在GC2和GC200中,PCIe已经被升级到PCIe4.0x16。两个并行的IPU芯片之间可以由三个链路连接,每个链路的名义双向带宽为64GB/s,其中两个预留给板内传输。IPU芯片之间的实际基准测试的连接带宽高达108GB/s。另外在建立更大规模的系统互联方面,IPU提供了名为IPU-link连接方式,IPU单芯片提供了多个IPU-link连接通道,最大能提供320GB/s的互联带宽。

IPU的运行模式:BSP批量同步并行

最后我们再来看看运行模式。由于没有外部内存,因此IPU的运行模式非常独特。IPU采用的是一种被称为BSP(BULKSYNCHRONOUSPARALLEL,批量同步并行)的运行模式。这种模式分为三步,第一步是本地计算。每个IPU的计算核心预先计算本地已经准备好的数据,不同的进程之间不会进行通讯。第二步是同步,在所有进程都达到同步点之前,任何进程都不会进行下一步操作或者通讯。第三部是通讯,进程开始利用片上和片外(如果存在多个IPU集群进行互连的话)互联系统交换数据,每个进程都可以向每个期望的数据目的地发送信息,此阶段不会进行任何计算。然后再进行下一次的计算、同步和通讯,周而复始,直到所有计算完成。

IPU的计算模式设计是非常独特的,其单向通讯、处理器只操作本地SRAM以及控制流程的简化,这使得整个操作的效率得到大幅度提升。不过这样的设计也带来了一些问题,比如计算和通信必须是串行的,另外所有计算核心必须步调一致,也就是维持极高吞吐量,否则就会出现不同核心之前的互相等待(所以Graphcore才为每个核心设计了SMT模式,支持6个线程同步)。这样一来,整个架构的压力更倾向于软件方面,硬件则大大简化了。

总的来看,IPU架构和芯片相比传统的AI加速芯片,带来了三个重要的改变,分别是MIMD多指令多数据流、包含本地SRAM的片上计算系统、解决了大规模并行计算处理核之间的效率问题。这三大系统集体运作,才带来了我们今天看到的Graphcore的产品以及其强悍的性能。

更大规模的产品实现:

Graphcore Colossus

MK2 GC200 IPU

在了解了IPU的架构以及其设计的相关内容后,让我们继续来了解GC200芯片。

在这里需要先声明的是,目前Graphcore推出的GC200芯片主要以标准的1U刀片服务器的方式提供,型号为IPU-MachineM2000(下简称“M2000”)。每一个M2000设备中包含了4个GC200芯片。Graphcore提供的大量官方数据都以M2000作为基本单位展示,毕竟最终售卖的是M2000刀片服务器。

根据Graphcore的数据,每一个GC200芯片都包含了1472个独立的IPU内核,能够执行8832个独立的并行计算线程,每个IPU可以执行6个线程。数据格式上,GC200支持IEEEFP32格式、FP16.32(16位乘32位累加)以及FP16.16(16位乘法累加)计算。在计算特性方面,GC200支持算术随机取整并可以以处理器的全速运行,因此GC200可以将所有的计算格式保持在16位,从而减少内存、读写需求等,同时又提供了全精度的计算结果。这个计算方法和目前谷歌、英伟达采用的BF16计算方法有一定的相似之处。不仅如此,每个IPU内核都可以从Graphcore开发的一种称为AI-Float的浮点技术中获得性能提升,同时AI-Float算术块还为稀疏算术浮点运算提供了本机支持。Graphcore为各种稀疏操作提供了库支持,包括块稀疏性和动态稀疏性。这意味着GC200不仅可以在推理中,还可以在训练过程中提供更高效的稀疏数据计算,从而帮助创作者创建新型复杂模型,以更少的参数、更短的训练时间以及更少的能量提供最先进的性能。根据Graphcore展示的数据,拥有4个GC200的M2000刀片服务器将带来超过1PFlop的AI计算能力。

除了相关的计算能力外,和之前的产品一样,GC200不再需要外部存储设备,整个处理器自带片上内存,这种内存被称为“In-Processor Memory”。GC200拥有高达900MB的片上SRAM作为内存,每个处理器内核都拥有自己的RAM,以最低能量的访问实现最高效率的数据读取。相比此前的GC2,GC200带来了超过3倍的数据存储空间,足以让处理器在高速运行中容纳大的数据模型、预先状态等内容,最大限速的加速整个系统。

由于片上内存的容量大幅度提升,Graphcore还带来了整合在《Poplar》管理软件中的、可以用于访问“Streaming Memory”的“Exchange-Memory”软件功能,通过联合使用这款软件,GC200可以支持拥有千亿个参数的超大模型。内存带宽方面,在《Exchange-Memory》软件的帮助下,拥有4个CG200芯片的M2000服务器支持数据密度高达450GB的Exchange-Memory,带宽也能够高达180TB/s。相比现有7nm的GPU产品,GC200的Exchange-Memory数据密度达到了前代产品的10倍,内存带宽则达到了前代产品的100倍。

数据通信方面,M2000内置了专用的AI通信网络,称作IPU-Fabric。这个通讯系统的核心一款名为GraphcoreGC4000IPU-Gateway的通讯芯片,这款芯片能够提供2.8Tbps的带宽,并且能够实现芯片之间的高速互联功能。值得一提的是,GC4000互联芯片还为多个M2000刀片服务器之间的互联提供支持,多个M2000服务器互联后,GC4000最多可以提供Pb级别的带宽。在这种连接中,IPU-Fabric将以3D环形拓扑的形式连接所有的计算核心,连接方式支持标准的铜连接或者OSFP光学连接器,也非常方便。

最后还是来看看性能方面的内容。由于IPU这类产品非常专业,因此对其性能很难得到具体的测试结果。Graphcore在2020年6月4日更新了软件系统后,在官网上展示了一些GraphcoreGC2针对英伟达V100的性能测试对比结果。包括自然语言BERT训练和推理,图像识别ResNeXt训练和推理、可分离卷积分析、时间序列分析、自动编码器训练(推荐/排名,基于Netflix数据)、马尔科夫链蒙特卡洛概率学习、强化学习等模型。从这些测试的数据可以看出,IPU在优化得当的情况下展示出了相比GPU更为出色的性能。在强化学习、概率学习等应用中带来了数十倍的性能提升,在可分离卷积分析中根据不同情况,性能提升幅度大约在4倍到100倍左右。其余的一些测试中,IPU基本都拥有1.25倍到6倍左右的性能提升。

需要注意的是,这里的性能对比是基于上代GC2和上代英伟达V100,两家公司最新的产品GraphcoreGC200和英伟达A100的性能对比还没有太多资料。考虑到Graphcore宣称GC200的性能相比GC2最多达到了8倍的提升,因此GC200的性能有很大可能是胜过A100的。

写在最后

总的来看,Graphcore推出的新品在计算性能方面表现非常出色,整体架构设计也几乎避开了目前主流的CPU和GPU的缺陷,堪称一个充满突破性和划时代的AI计算产品。剩下的问题就是Graphcore能否更进一步,发展壮大了。一般来说,在AI这种快速发展的产业界,新创意、新产品年年都有,层出不穷,但大部分都在大浪淘沙中变得无影无踪。一个全新的技术体系和创新思想最后是否能发展壮大,还得看是否有好的产业环境和生态支持。在这一点上,Graphcore还算不错,微软、阿里、百度等巨头都纷纷对其提供了支持,Graphcore中文官网的资料也很详细,国内市场空间应该也很广阔。在GC200发布后,已经有多家AI厂商宣布考虑和Graphcore合作。目前的問题主要还是Graphcore本身,能否继续在现有技术和软件架构的基础上,扬长避短,加强优势,解决难题,才是Graphcore和旗下芯片进一步扩张市场的最根本因素。