基于Protues的静态CMOS逻辑电路的设计与仿真

钱香 李丽萍

摘 要:微电子学是一门理论性较强的学科,为了提高学生的学习效果及学习兴趣,在课程中加入实验教学环节。静态CMOS逻辑电路是集成电路中常用的逻辑电路。本文介绍了Protues软件在集成电路设计教学中的应用,通过实例讲解如何用Protues软件进行静态CMOS逻辑电路的设计与仿真。学生通过软件设计并仿真电路,加深对知识点的理解,提高学习效果和学习兴趣。

关键词:集成电路 CMOS Protues 表决器

中图分类号:G642.0 文献标识码:A 文章编号:1674-098X(2020)06(b)-0104-02

集成电路产业是信息技术产业的核心。《中国集成电路产业人才白皮书(2018-2019年版)》数据显示我国集成电路人才的缺口较大,预计到2021年存在26.1万人的缺口[1]。无锡被公认为是中国的“硅谷”,微电子企业较多,可是并不是每个高职院校都开设了微电子技术专业,微电子技术专业的学生数量远远满足不了企业的需求。对非微电子技术专业的学生开设微电子学相关课程一方面可以拓宽学生的知识面,另一方面可以让将来从事微电子工作的学生更快适应工作。

微电子学是一门理论性较强的学科,讲解专业知识时比较枯燥,学生容易缺乏兴趣,且不容易理解。为了提高学生的学习效果及学习兴趣,在课程中加入实验教学环节。其中集成电路设计一般使用Cadence软件,学生必须到实验室才能使用,且入门稍难。对于非微电子技术专业的学生来说,可以用Protues软件来进行简单的电路设计。Protues软件中的元器件种类多、电子仪器多、仿真分析丰富,且在电子专业课程中使用较多,学生相对熟悉容易完成实验内容。下面介绍用Protues软件设计并仿真集成电路设计中的静态CMOS逻辑电路的方法。

1 静态CMOS逻辑电路的构成方法

CMOS反相器是静态CMOS逻辑电路的基本单元之一[2]。无论输入高电平还是低电平,电路中只有一个MOS管导通,电源到地没有直流通路,所以电路只有由于PN结漏电和MOS管的亚阈值漏电产生的很低的静态功耗。

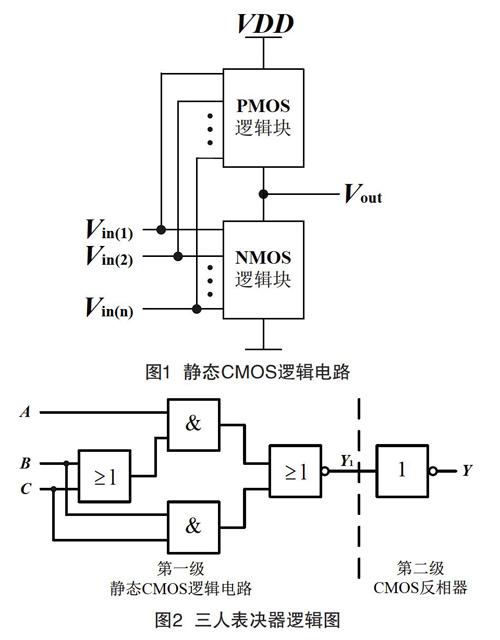

静态CMOS逻辑电路是在CMOS反相器的基础上构成的,用NMOS逻辑块代替反相器中的NMOS管,用PMOS逻辑块代替反相器中的PMOS管,如图1所示[3]。NMOS逻辑块的构成规律是“串与并或”,PMOS逻辑的构成规律是“串或并与”。静态CMOS逻辑电路类似于CMOS反相器,输出执行反相的逻辑功能。在一定的输入信号下,NMOS和PMOS逻辑块中只有一个逻辑块导通,另一个逻辑块截止。

2 静态CMOS电路设计

以数字电子技术中常见的三人表决器电路为例,讲解如何用静态CMOS逻辑电路进行设计。三人的表决意见分别用A、B、C表示,同意用1表示,反对用0表示;表决结果用Y表示,表决通过用1表示,不通过用0表示。根据数字电子技术的知识,可以得出表决器的逻辑表达式为:

或写为:

因静态CMOS逻辑电路是实现带“非”的功能,将逻辑表达式转换为与或非的形式:

用静态CMOS逻辑电路实现三人表决器的逻辑图如图2所示。电路由两级静态CMOS逻辑电路构成,其中第二级是CMOS反相器。

3 Protues软件设计与仿真

在Protues软件中加载电路中需使用的MOS管,NMOS管选用TN2501,PMOS管选用TP2502,按照NMOS和PMOS逻辑块的构成规律设计出三人表决器的电路图,如图3所示。输入信号较少时,可以采用虚拟示波器显示仿真结果。将输入信号A、B、C分别接到示波器的A、B、C端相接,输出信号Y接到示波器的D端。

设置电源电压VDD为5V,输入信号A、B、C分别设置為频率是1kHz、2kHz、4kHz的方波。对三人表决器电路仿真,示波器显示的仿真结果如图4所示。图中从上到下依次为:A、B、C和Y。从仿真结果可以看出,只有A、B、C中同时有两个或三个信号为1时,输出为1,符合三人表决器的功能。

Protues软件提供电路分析功能,对于数字电路可以直接显示出电路中任何节点的波形,这一点在输入信号较多时分析输出结果较为方便,图5即为三人表决器电路用数字分析显示的波形图。

4 结语

本文以三人表决器为例,介绍了用Protues软件设计并仿真静态CMOS逻辑电路的方法,通过对电路设计仿真,掌握电路的设计方法。随着信息化的发展和普及,学生计算机的操作水平不断提升,用软件对电路进行仿真,可以提高学生的学习效果和学习兴趣。学生也可以在自己的电脑上安装Protues软件,课后可以有更多的时间来学习集成电路设计,提高自己设计电路的熟练度。

参考文献

[1] 杨坤漓.数字电子时钟逻辑电路的教学设计与仿真[J].电子制作,2019(20):29-30,38.

[2] 李伟华.VLSI设计基础[M].3版.北京:电子工业出版社,2013.

[3] 王文彬,杨定坤,罗坤,等.基于Cadence的静态CMOS门电路仿真设计[J].科学技术创新,2019(24):64-65.