一种小型化记录仪光纤数据接口

史占付 展学磊

西安机电信息技术研究所,中国·陕西 西安 710065

针对小型化抗高过载数据记录仪接口传输速率慢无法适应光纤数据记录的问题,设计了一款具有12.5Gbps 光纤数据接收能力的数据接口,数据接口采用了Aurora 协议8B/10B 编码接收、光电转换、FPGA 高速串行GTX 接收、DDR3 缓存,再以CML 接口发送给数据记录仪。

数据记录仪;Aurora 协议;HTG8503 模块

1 引言

图像识别技术的应用需要高清图片数据传输,传统的RS485、1553B 和CAN 总线等在带宽很难满足需求,大功率部件的频繁动作和天线辐射等干扰源通过传导和辐射等方式对通信系统造成干扰,光纤通信因其具备通信速率高、传输距离远和抗电磁干扰等特点被广泛应用。现有小型化抗高过载数据记录仪接口不能满足光纤通信要求,具有高速串行收发器的FPGA 多采取BGA 封装,无法满足数据记录器仪抗高过载的需求[1]。

针对光纤通信系统的特点,开发并设计一款光纤数据接口,满足抗高过载数据记录仪需求,论文详细描述了光纤数据接口的实现方法、系统组成、原理框图、程序流程、试验验证和原理样机等。

2 方案

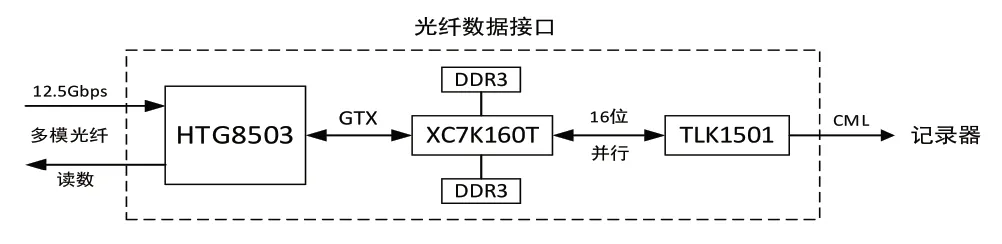

光纤数据接口接收4 路3.125Gbps 光纤数据,通过HTG8503 将多模光纤信号转换成高速差分电信号,该电信号经过FPGA 高速串行收发器GTX 接收,GTX 接收来的数据因速率较高不能直接被数据记录仪存储,经两片DDR3 缓存,再以CML 接口形式发送给数据记录仪记录。CML 接口采用TI 公司TLK1501 芯片,数据记录仪也采用该芯片,该芯片采取64 脚VQFP 封装(非BGA 封装),经灌封后具有较强的抗过载能力,CML 接口简单只有一路双绞差分输入线和一路双绞差分输出线(读数用)[2]。

光纤数据信号记录后弹体落地,光纤数据接口因有BGA封装器件抗冲击能力较弱直接损坏,数据记录仪抗过载能力强,回收后只需连接几根线更换一个新的光纤数据接口就能实现高速数据读取。

3 光纤数据接收和转发

光纤数据接口使用的是多模光纤,HTG8503 模块实现高速光电转换,XC7K420T 利用高速串行收发器GTX 接收数据,2 片DDR3 缓存数据,TLK1501 芯片以CML 接口形式将数据发送给数据记录器。光纤数据接口原理框图如图1所示。

图1 光纤数据接口原理框图

光纤数据接口有4 个通道,每通道码率3.125 Gbps,总的码率为3.125x4=12.5Gbps,数据传输采用Aurora 协议8B/10B 编码协议接收,接收速度换算成字节速度为1.25GBps。单包光纤传输最大容量为5Gb(625MB),镁光MT41K512M16 芯片16 位数据带宽存储速度为1.6GBps,采用两片DDR3 缓冲速度可达3.2GBps,满足光纤传输最大速率为1.25GBps 的要求,2 片DDR3 的存储容量为1GB,满足单包光纤传输最大容量为5Gb(625MB)的需求,采取2 片DDR3 缓存的设计方案有一定的设计余量,方便以后的需求扩展[3]。

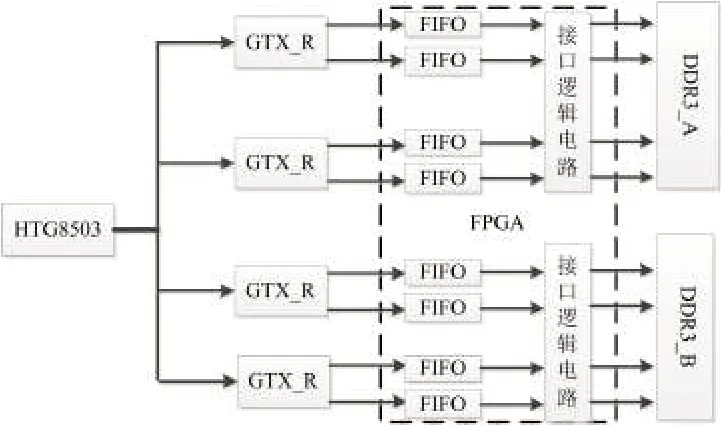

光纤数据接口按Aurora 协议接收光纤数据,Aurora 协议是由Xilinx 公司提供的一个开放的、免费的链路层协议,按Aurora 协议接收到的光纤数据为32 位并行数据保存在2个FIFO(宽度为32 位)中,每两路光纤数据保存在一个DDR3 中,当第一个FIFO 存储满以后就开始向第二FIFO 保存数据,控制逻辑将第一个FIFO 中的数据保存在DDR3 中,依次循环将接收到的所有数据保存在DDR3 中。向FIFO 写入的时钟频率速度为78.125MHz,78.125×4=312.5MB/s,即一路光纤向FIFO 写入的速度为312.5MB/s,两路光纤信号总的写入速度为625MB/s,一个DDR3 缓存两路光纤数据。选择DDR3 时钟频率为312.5MHz,其写入数据的速度为312.5×4=1250MB/s,这样向DDR3 写入的速度是接收数据速度的两倍,可以留出时间对DDR3 进行刷新。操作DDR3接口逻辑电路的时钟频率按照2:1 配置即为156.25MHz,数据宽度为64 位,接口逻辑以156.25MB/s 的速度从两个FIFO中读取数据并写入到DDR3 中。光纤数据接口FPGA 链路逻辑配置如图2所示。

图2 光纤数据接口FPGA 链路逻辑配置图

光纤平均存储速率为1Gbps(125MBps),采用2 通道CML 信号发送,发送时钟频率为40MHz,16 位数据宽度,总的发送速度为160MB/s,满足转发速度要求。建立4 个大小为2K 的缓冲区(数据宽度64 位),每个DDR3 对应两个缓冲区,2 个缓冲区对应一个CML。从DDR3 读取数据的时钟频率为156.25MHz,读取1 页的时间为1.6384μs,CML 发送1 页数据(大小为2k)的时间为25.6μs,读取1 页后关闭该页,然后等间隔刷新16 次[4]。2 个传输通道并行独立工作。DDR3 软件转发逻辑图如图3所示。

图3 DDR3 数据转发软件逻辑图

光纤数据总容量为32GB,要求数据存储速度为1Gbps,存储速度换算成字节为125MBps,镁光工业级SLC 颗粒FLASH 存储器同步存储速度可达200MBps,但该芯片采取BGA 球删封装,抗过载能力较弱,故不能采用。数据记录器采取4 片48 引脚TSSOP 的FLASH 芯片设计,该存储芯片异步存储速度最大为50MBps,留有一定设计余量实际使用为40 MBps,4 片存储速度为160MBps 总容量满足需求。光纤数据接口速率满足情况见表1。

表1 光纤数据接口速率满足情况

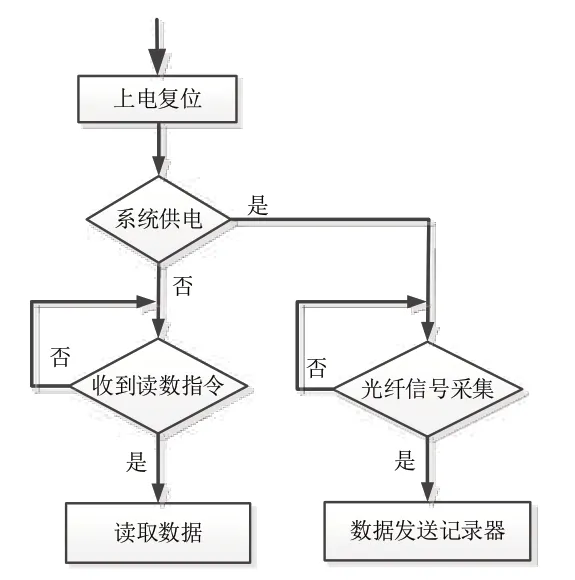

光纤数据接口识别上电后首先识别是否系统供电,如果是系统供电,则进入采集状态,否则是地面供电,则进入读数状态。系统供电时,同步接收光纤通道的数据,接收有效的光纤数据后,光纤数据存储模块进入数据存储状态,直到记录满或者断电;地面供电时,接收到有效的地面命令后,进入地面控制状态,可以读取记录的数据、擦除已存储的数据、读取状态等。光纤数据接口进入存储状态后不再接收地面发送的命令,进入地面控制状态后也不再接收光纤通道的数据。解码用FPGA 软件流程图如图4所示。

图4 光纤数据接口FPGA 软件流程图

4 仿真测试

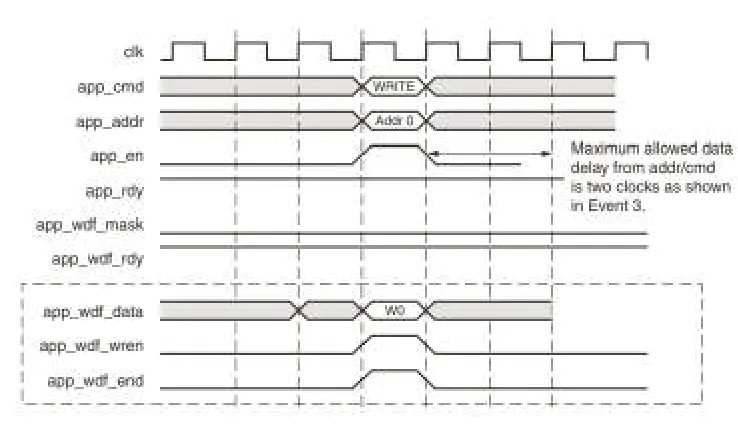

DDR3 单个数据写操作时地址控制信号与写数据信号严格按照时序图对齐。判定写允许信号可以设定为:

app_rdy & app_wdf_rdy,app_wdf_end = app_wdf_wren

这里app_en 信号有效时间为1 个clock,不能随意延长。如果单个写操作都是写入128 个数据,要求app_en 信号和app_addr 信号有效时间均为128 个clock,需要完全对齐,不能随意延长[5]。

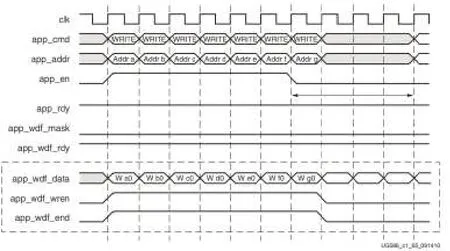

连续写操作时写数据可以不受写指令时序的制约,地址控制信号和写数据控制信号可以完全独立。可以分别使用独立的计数器。实际调试过程中发现:app_wdf_rdy 有效时间比 app_rdy 有效时间更连续。

在实际使用测试可知,一直单个数据写操作效率理论上低于连续的写操作效率,但实际使用效率相差很少,而且前者方法更容易理解,编程更容易一些。图5为单个数据写操作时序图,图6为连续数据写操作时序图。

图5 单个数据写操作时序图

图6 连续数据写操作时序图

5 原理样机

由设计方案利用candence 软件绘制原理图,并制成12层PCB 版图,焊接调试后板载GTX 在线ibord 外环仿真测试速率可以达到6.5Gbps,满足设计需求,DDR3 时钟频率为800M,程序运行半个小时,DDR3 写入和读取误码率基本为0,图7为光纤数据接口原理样机。

图7 光纤数据接口原理样机

6 结论

采用Aurora 协议8B/10B 编码接收、光电转换、FPGA高速串行GTX 接收、DDR3 缓存再以CML 接口发送给数据记录仪的由光纤数据接口,方案设计合理、在线仿真正确、原理样机验证可行。