基于NiosⅡ软核的音频播放系统设计与实现

付扬 李成

摘 要: 利用SoPC设计灵活和软硬件可编程的优势,开发设计基于Nios Ⅱ嵌入式软核的SoPC音频播放系统。该设计在SoPC Builder下开发了基于Nios Ⅱ软核的基本系统,利用Verilog语言进行了I2C数据传输模块和音频配置模块的硬件设计,并在Nios Ⅱ IDE软件环境下实现音频播放的软件设计。以Altera公司FPGA EP2C35F48418为核心芯片,以TLV320AIC23B为音频模块,通过SoPC的软硬件协同设计成功实现了一款通用的音频播放系统。该设计采用SoPC技术,具有可靠性、灵活性和扩展性强的优势。

关键词: 音频播放; 系统开发; 硬件配置; 软件设计; 系统验证; 协同设计

中图分类号: TN912.2?34 文献标识码: A 文章编号: 1004?373X(2020)10?0059?04

Design and implementation of audio playing system based on NiosⅡsoft core

FU Yang, LI Cheng

(College of Computer and Information Engineering, Beijing Technology and Business University, Beijing 100048, China)

Abstract: The SoPC audio playing system based on Nios Ⅱ embedded soft core is developed and designed by making use of the SoPC′s advantages of flexible design and programmable software and hardware. In this design, the basic system based on Nios Ⅱ soft core is developed with the SoPC Builder, the hardware designs of I2C data transmission module and audio configuration module are performed by means of the Verilog language, and the software design of audio playing is realized in the Nios Ⅱ IDE software environment. With FPGA EP2C35F48418 made in Altera Corporation as the core chip and TLV320AIC23B as the audio module, a universal audio playing system is implemented successfully by means of the co?design of SoPC hardware and software. The SoPC technology is adopted in the design, and the design has the advantages of reliability, flexibility and expansibility.

Keywords: audio player; system development; hardware configuration; software design; system verification; co?design

0 引 言

可编程片上系统(System on a Programmable Chip,SoPC)是一種特殊的嵌入式系统,首先它由单个FPGA芯片融入了很多模块,特别是软核微处理器,能够完成整个系统的主要逻辑功能,其次它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,具备软硬件在系统可编程的功能。Altera 公司的Nios Ⅱ软核处理器是基于哈佛结构的RISC通用嵌入式处理器软核,能与用户逻辑相结合,编程至该公司的FPGA中,处理器具有32位指令集、32位数据通道、可配置的指令以及数据缓冲,它特别为可编程逻辑进行了优化设计。以Nios Ⅱ软核为处理器的SoPC设计灵活、高效、成本低廉,以此开发的消费电子产品将具有很大的竞争力。

多媒体技术中,特别是音频播放技术,在手持终端产品中具有巨大应用潜力和市场前景,基于SoPC技术设计开发支持多媒体技术的手持播放产品将具有可靠性高、体积小、耗电少和灵活性强等特点。本设计采用SoPC设计方案,基于Nios Ⅱ处理器软核构建系统,利用Verilog硬件描述语言完成了I2C数据传输模块、音频配置模块等系统与外围硬件接口的设计,并通过软件实现从SD卡中读取数据并传送到硬件系统中对数据进行处理,最终实现了具有大容量移动存储功能并能流畅播放音频文件的音频播放系统[1]。

1 硬件模块化设计

利用Quartus Ⅱ软件中的SoPC Builder创建基于Nios Ⅱ处理器的基本系统,在此系统的基础之上,通过Verilog硬件描述语言设计I2C通信模块、音频配置模块,并对各个模块进行仿真验证,最终完成硬件总体结构的设计[2]。

1.1 基于NiosⅡ软核基本系统构建

为了更好地完成数据的传输与储存,并且保证音频文件播放的流畅性,在构建一个SoPC系统时选用Nios Ⅱ/f快速软核。此软核具有最高的系统性能,中等FPGA使用量。在添加Nios Ⅱ/f快速软核时将重置向量存储器设置为FLASH,常向量存储器设置为SDRAM,并设置偏移地址以保证此内核可以正常工作。选用Nios Ⅱ处理器后,继续为系统配置SDRAM存储器、TIMER定时器、System ID peripheral系统标识符、Avalon?MM流水线桥接口IP核、JTAG边界扫描调试串口IP核、定时器EPCS控制器、FLASH控制器、外部存储器控制器、三态总线桥等系统必要的IP核,如图1所示,分配好地址范围后,构成基于Nios Ⅱ的基本系统[3]。

1.2 I2C数据传输模块设计

I2C由两条双向串行总线(SCL,SDA)构成,可以完成多个器件之间的数据交换。主从器件之间在SDA总线上进行数据传输,SCL总线的功能是进行时钟同步。数据传输以字节为单位,每位占用一个时钟,其中最高有效位在先,每个字节后跟随一个应答位(ACK)。只有在总线处于“非忙”状态时,数据传输才能开始。在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。当时钟线SCL为高电平状态时,数据线SDA由低电平变为高电平的上升沿被认为是“停止”信号。随着“停止”信号的出现,所有的外部操作都结束。audio_config中I2C总线配置模块是按照上述I2C总线规范和标准时序,用Verilog语言设计实现的[4]。

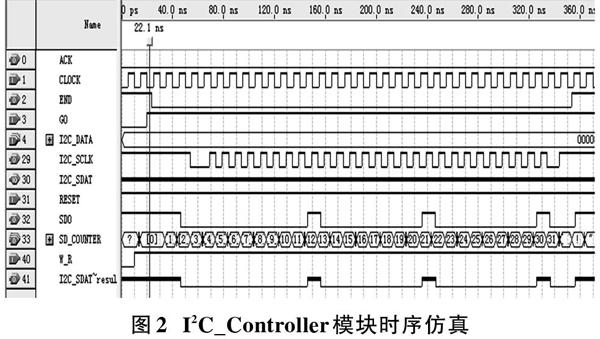

I2C控制器需要在33个时钟周期内完成一次24位的数据传输。I2C控制器完成一次数据传输可以分为4个阶段:第1个阶段为初始化控制器;第2个阶段为启动传输;第3个阶段为传输数据;第4个阶段为停止传输。初始化控制器在第1个时钟周期完成,启动传输在第2和第3周期完成,数据传输在第4~30周期完成,其中包含3个ACK应答位,而停止传输则在最后3个周期完成。设置一个6位的计数器SD?COUNTER用于对传输周期进行计数。设置一个寄存器SCLK用于产生开始与停止的条件。在开始前与停止后SCLK均保持高电平,数据传输阶段为低电平[5]。对设计模块进行时序仿真,结果如图2所示。

通过时序仿真图2可以看出,根据设计计数器的值在4~30之间是产生与时钟信号同频率的SCLK信号。为模拟数据的传输,将数据信号DATA始终设置为0。可以看到在计数器为0~2时,把数据储存到24位寄存器SD0中,在计数器为3~11时发送从设备地址,在计数器为12~20时发送从设备寄存器地址,在计数器为21~29时发送数据,在计数器为30~32时停止,并在每部分完成后将SD0置1作为ACK应答位。在传输开始之前和传输结束之后SCLK均保持高电平。可见时序仿真结果验证了本模块设计的正确性。

1.3 音频配置模块设计

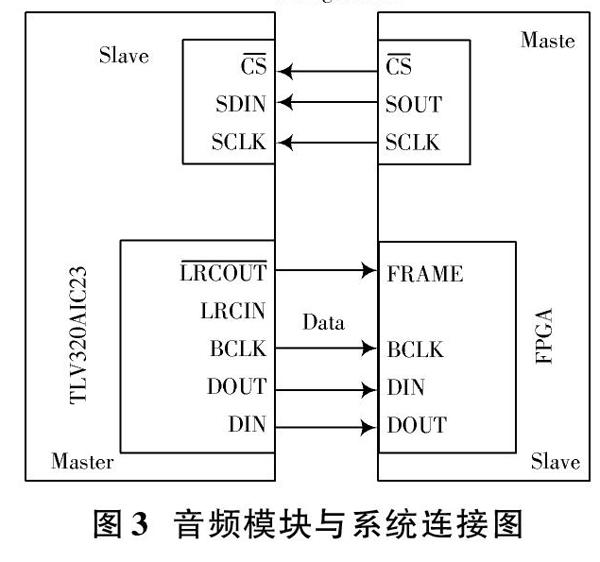

音频配置模块设计选用型号为TLV320AIC23B的芯片对音频信号进行处理。FPGA通过TLV320AIC23B芯片的控制接口,对TLV320AIC23B芯片的11个控制寄存器输入控制字,用以设置芯片的工作模式。而该芯片有两种控制接口类型,分别是三线模式的SPI接口和兩线模式的I2C接口模式。因为选用了I2C接口模式,所以MODE=0。TLV320AIC23与FPGA器件EP2C25F48418的连接结构如图3所示[6]。

在2?wire模式下,数据利用SDIN传送串行数据,SCLK作为串行时钟。SCLK为高电平时,SDIN产生一个下降沿指示传输开始。开始沿的后7位决定2?wire总线上的哪个设备接收数据。R/W决定了数据传输的方向。TLV320AIC23B是一个仅写设备,所以仅当R/W为0时设备反应。在此模式下,TLV320AIC23B仅工作于从模式,其地址由CS管脚决定。通过第9个时钟周期将SDIN的一个上升沿用来标志传输结束。控制字分为两个部分:一个部分为地址;另一个部分为控制数据。B[15:9]为地址,B[8:0]为控制数据[7]。

根据以上时序要求在Quartus Ⅱ开发环境下通过Verilog硬件描述语言描述audio_config模块,在该模块中调用I2C_Controller模块根据I2C协议对数据进行传输,并对TLV320AIC23B进行配置[8]。对此模块进行的仿真如图4所示。为便于观察结果,将时钟频率与I2C传输频率之比调低。从图中可以看出,该模块实现了对时钟模块的分频,使其与I2C控制模块频率相匹配,从而能够正确地完成数据的传输。mSetup_ST寄存器在不同状态下完成了对标志位的改变,同时LUT_INDEX寄存器在不同状态下根据TLV320AIC23B寄存器地址把数据传输给LUT_DATA寄存器,完成了对TLV320AIC23B的配置,此时序仿真验证了此模块满足设计要求。

2 系统FPGA验证

在系统硬件中,除了基于Nios Ⅱ的基本系统和音频配置模块外,为使系统能够正常运行还需要加入锁相环PLL(Phase?lock Loop),设计所使用的开发平台上只有一个50 MHz的时钟信号,通过PLL生成三个50 MHz的时钟,一个为系统时钟,另外两个50 MHz的时钟分别为存储器提供时钟信号及外设芯片的时钟信号。使用Altera的基本宏功能来生成PLL,通过Altera的IP工具MegaWizard管理器定制基本宏功能参数。设置输入输出管脚,对整个系统进行编译,从而完成了整个系统硬件部分的配置与设计[9]。

系统成功完成FPGA验证,编译报告如图5所示,整个SoPC系统硬件占用EP2C35F48418芯片6 075个逻辑单元,占用芯片资源的18%,其中用于实现组合逻辑功能的LUT表使用了5 311个,寄存器总共使用了3 305个,使用片内存储器96 384位以及1个PLL锁相环, 很好地完成硬件配置。

3 软硬件协同设计实现音频播放

为满足SD卡读取数据的相关时序并读取相应的数据,在SD_Card.h文件中定义如下语句,通过软件与硬件结合的方式,将数据送到相关的接口,从而按照SD卡时序要求完成数据读取的任务[10]。

//SD卡设置输入输出方向

#define SD_CMD_IN IOWR(SD_CMD_BASE, 1, 0)

#define SD_CMD_OUT IOWR(SD_CMD_BASE, 1, 1)

#define SD_DAT_IN IOWR(SD_DAT_BASE, 1, 0)

#define SD_DAT_OUT IOWR(SD_DAT_BASE, 1, 1)

// SD卡输出高低电平

#define SD_CMD_LOW IOWR(SD_CMD_BASE, 0, 0)

#define SD_CMD_HIGH IOWR(SD_CMD_BASE, 0, 1)

#define SD_DAT_LOW IOWR(SD_DAT_BASE, 0, 0)

#define SD_DAT_HIGH IOWR(SD_DAT_BASE, 0, 1)

#define SD_CLK_LOW IOWR(SD_CLK_BASE, 0, 0)

#define SD_CLK_HIGH IOWR(SD_CLK_BASE, 0, 1)

//SD卡输入读操作

#define SD_TEST_CMD IORD(SD_CMD_BASE, 0)

#define SD_TEST_DAT IORD(SD_DAT_BASE, 0)

读取SD Card的函数为SD_read_lba(Buffer,j,1);表示从SD Card的第j个扇区开始,读取一个扇区放在 char Buffer[]里。这样就可以从SD Card里读取数据,需要设置4个全局变量以跟踪SD Card的读取情况,流程图如图6所示。Int Sector:记录SD Card的扇区;Unsigned char Buffer[512]:从SD Card里读出来先放在这里;Int IsFinish:判断第j个扇区是否用完;Int Sector

OffSet:Buffer数组中的下标。

系统运行后从控制台打印出的系统读取当前的字节数,这些数据表明系统正在从SD卡中读取音频文件数据到缓冲区SDRAM中,验证了之前通过PIO接口以软硬件结合的方式来满足SD卡传输数据的时序要求,从而验证了从SD卡中数据读取任务完成的正确性。

播放的音频文件为WAV格式。WAV为微软公司开发的一种声音文件格式,它符合RIFF(Resource Interchange File Format)文件规范,用于保存Windows平台的音频信息资源,被Windows平台及其应用程序所广泛支持,支持多种音频数字,取样频率和声道。标准格式化的WAV文件和CD格式一样,也是44.1 kHz的取样频率,16位量化数字,因此声音文件质量和CD相差无几。音频DAC控制器被集成到了Avalon总线结构中,Nios Ⅱ处理器检查音频DAC控制器的FIFO存储器是否被填满。如果FIFO不满,处理器读取一个512字节段,通过Avalon总线将数据发送至音频DAC控制器的FIFO。AUD_FULL_BASE变量为标志判断存储器是否已满,在已经完成数据读取的情况下,便可以将读入的音频文件的数据流输入到由TLV320AIC23B为主体的音频播放模块,即可完成音频播放的任务[11]。

通过NiosⅡ处理器系统硬件运行此软件,在控制台可以看到显示SD卡中的数据被读入到系统缓存中,读入无误并且完成后便可将耳机或者扬声器连接到音频输出接口,即可听到声音清晰且播放流畅的音频文件,从而成功实现了基于NiosⅡ软核的音频播放系统的设计。

4 结 语

本文设计采用超大规模集成电路,实现基于 Nios Ⅱ软核为核心的SoPC嵌入式数字音频播放系统。 该系统通过Verilog语言对I2C数据传输模块和音频处理模块的设计,很好地解决了数据传输和FPGA与TLV320AIC23B之间接口的匹配问题,并通过SoPC的软硬件协同设计实现了音频文件的流畅播放。由于采用先进的SoPC技术,选用Nios Ⅱ软核作为处理器,使得在较低的时钟频率下具备更高性能和具有硬件加速、定制指令等优势,同时模块的Verilog硬件语言设计具有极大的灵活性,所以该音频播放器具有处理能力强、复用性强、可裁剪、扩展性好等特点,该设计在多媒体产品中具有一定实用价值和应用前景。

参考文献

[1] CHU P P.基于Nios Ⅱ的嵌入式SoPC系统设计与Verilog开发实例[M].金明录,门宏志,译.北京:电子工业出版社,2015.

[2] 杨秀增,杨仁桓.基于FPGA的高精度超声波测距仪设计[J].现代电子技术,2017,40(1):145?147.

[3] 张艳.基于FPGA低频信号发生及分析仪设计[J].自动化与仪器仪表,2016(6):40?41.

[4] 吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2017.

[5] 张晓龙.基于Avalon?MM的I2C总线控制器设计及VMM验证[J].计算机测量与控制,2016,24(2):147?150.

[6] Altera Corporation. Avalon interface specification [EB/OL]. [2013?11?01]. http://www.Altera.com.cn /devices/processor/nios2/benefits/performance/ni2?high?performance. html.

[7] 江一帆,江飚.基于NiosⅡ的音频录播系统设计[J].计算机应用,2014,34(z1):262?264.

[8] 秦玉龙.Avalon总线的音频编解码控制器IP核设计[J].单片机与嵌入式系统应用,2017,17(6):60?62.

[9] 万宇,祝忠明,李灿,等.基于Nios Ⅱ的音頻播放器硬件实现[J].中国集成电路设计,2014(10):33?36.

[10] 陈侠,李开航.基于SoPC和Nios Ⅱ的SD卡文件系统的设计[J].现代电子技术,2012,35(16):12?14.

[11] Altera Corporation. NiosⅡcustom instruction user guide [EB/OL]. [2013?11?01]. http://www.Altera.com.cn/ literature/lit?sop.jsp.